1

(21)4404695/24-24

(22)04.04.88

(46) 07.02.90. Бюл. № 5

(71)Дагестанский политехнический институт

(72)Ш.-М.А.Исмаилов и Э.Х.Хаспулатов

(53)681.3(088.8)

(56)Авторское свидетельство СССР № 525946, кл. Н 03 М 7/18, 1974.

Авторское свидетельство СССР Р 1388996, кл. Н 03 М 7/18,20.06.86.

(54)ПРЕОБРАЗОВАТЕЛЬ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ СЧИСЛЕНИЯ В ОСТАТОЧНЫХ КЛАССАХ в двоичный код

(57)Изобретение относится к вычисли1Z С1

тельной технике и может быть использовано при разработке быстродействующих устройств преобразования чисел в современных цифровых вычислительных машинах. Цель изобретения - сокращение аппаратурных затрат. Преобразователь содержит выход 1 преобразователя, регистр 2, мультиплексор 3, вычитатель 4 по совокупности модулей, мультиплексор 5, счетчик 6, блок 7 памяти, накапливающий сумматор 8, информационный вход 9 преобразователя, вход 10 начальной установки преобразователя, тактовые входы 11-13 преобразователя. 2 ил., 1 табл.

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерный преобразователь чисел из кода системы счисления в остаточных классах в позиционный код | 1990 |

|

SU1798921A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1990 |

|

RU2029434C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЛА ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД | 2002 |

|

RU2235423C2 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1986 |

|

SU1410281A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Генератор случайных чисел | 1985 |

|

SU1262492A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке быстродействующих устройств преобразования чисел в современных цифровых вычислительных машинах. Цель изобретения - сокращение аппаратурных затрат. Преобразователь содержит выход 1 преобразователя, регистр 2, мультиплексор 3, вычитатель 4 по совокупности модулей, мультиплексор 5, счетчик 6, блок 7 памяти, накапливающий сумматор 8, информационный вход 9 преобразователя, вход 10 начальной установки преобразователя, тактовые входы 11-13 преобразователя. 1 табл., 2 ил.

ел

Јъ

00

со

Изобретение относится к вычисли™ тельной технике и может быть использовано в цифровых машинах, функционирующих в системе счисления в остаточных i-лассах.

Целью изобретения является сокращения аппаратурных затрат

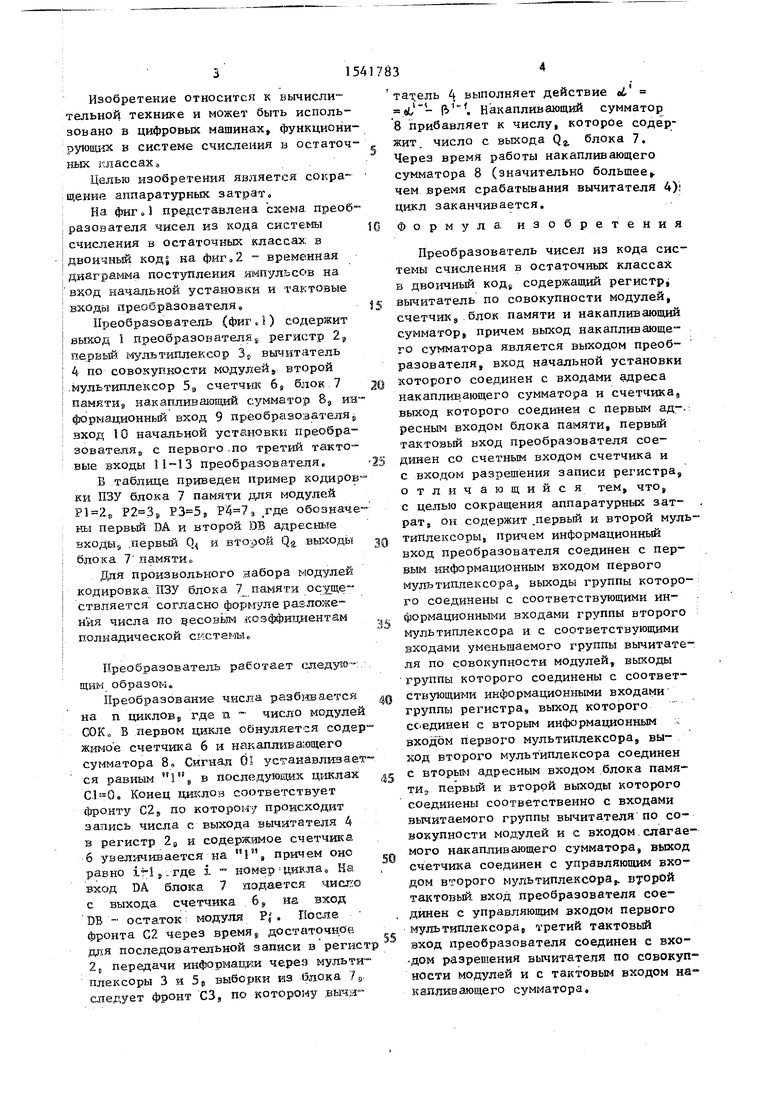

На фиг о 1 представлена схема преоб- разоватапя чисел из кода системы счисления а остаточных классах в двоичный код; на фиг,2 - временная диаграмма поступления импульсов на вход начальной установки и тактовые входы преобразователя.

Преобразователь (фиг,) содержит выход I преобразователяг регистр 2г первый мультиплексор 3S вычятатель 4 по совокупности модулей, второй мультиплексор 58 счетчик 69 блок 7 памятиэ накапливающий сумматор 89 информационный вход 9 преобразователя jj вход 10 начальной установки преобразователя „ с первого по третий тактовые входы 11-13 преобразователя.

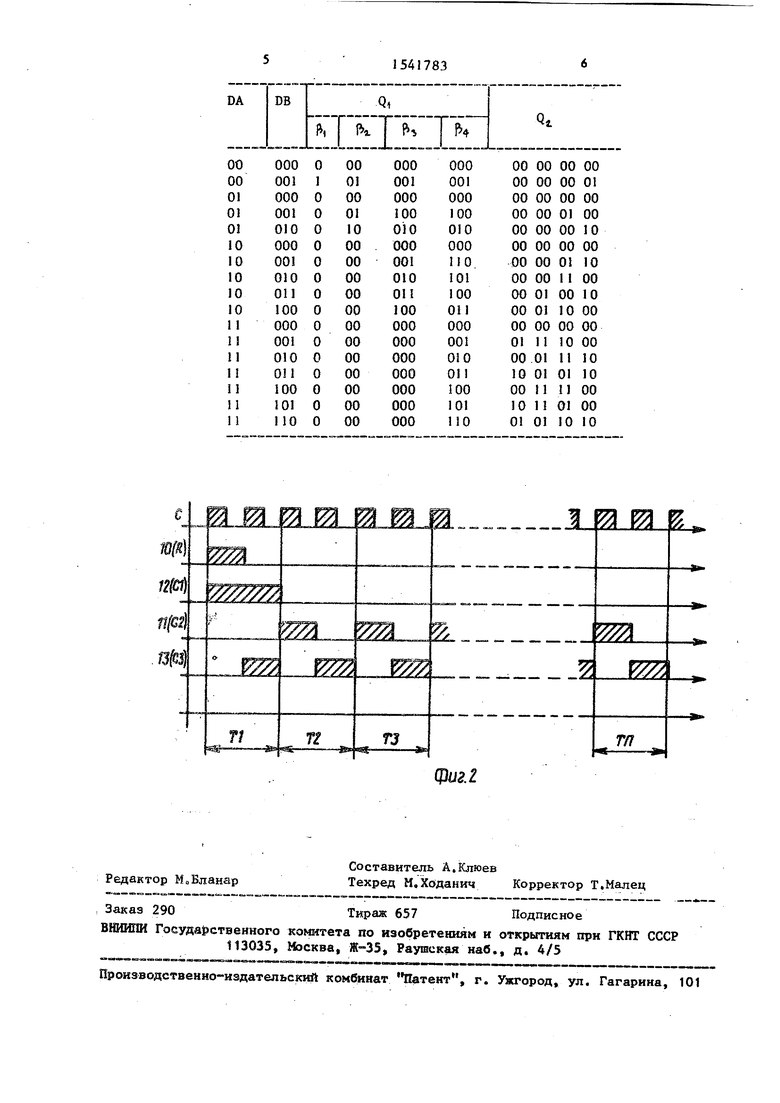

В таблице приведен пример кодировки ПЗУ блока 7 памяти для модулей , .где обозначены первый DA и второй DB адресные входы., первый О и второй Q выходы блока 7 памяти

Для произвольного набора модулей кодировка ПЗУ блока 7 памяти ствляется согласно формуле разложения числа по десовым коэффициентам полиадической системы

Преобразователь работает следующим образом.

Преобразование числа разбивается на п циклов9 где о. число модулей СОК„ В первом цикле обнуляется содержимое счетчика б и накапливающего сумматора 8, Сигнал 0 устанавливается равным 1, в последующих циклах Конец циклов соответствует фронту С28 по которой/ происходит запись числа с выхода вычитателя 4 в регистр 29 и содержимое счетчика 6 увеличивается на s причем оно равно г-1г.где i - номер цикла,, На вход DA блока 7 подается чисто с выхода счетчика 6Э на вход Щ - остаток модуля P,j , После фронта С2 через время, достаточное для последовательной записи в регист 26 передачи информации через мультиплексоры 3 ч 5( выборки из блока 7В следует фронт СЗ, по которому вычл

тат.ель 4 выполняет действие ot, . Накапливающий сумматор 8 прибавляет к числу, которое содержит, число с выхода Q блока 7. Через время работы накапливающего сумматора 8 (значительно большее чем время срабатывания вычитателя 4): цикл заканчивается.

Формула изобретения

Преобразователь чисел из кода системы счисления в остаточных классах в двоичный код8 содержащий регистр, вычитатель по совокупности модулей, счетчик8 блок памяти и накапливающий сумматор, причем выход накапливающего сумматора является выходом преобразователя, вход начальной установки которого соединен с входами адреса накапливающего сумматора и счетчика, выход которого соединен с первым ад-- ресным входом блока памяти, первый тактовый вход преобразователя соединен со счетным входом счетчика и с входом разрешения записи регистра, отличающийся тем, что, с целью сокращения аппаратурных затрат, он содержит .первый и второй мультиплексоры, причем информационный вход преобразователя соединен с первым информационным входом первого мультиплексора, выходы группы которого соединены с соответствующими информационными входами группы второго мультиплексора и с соответствующими входами уменьшаемого группы вьгчитате- ля по совокупности модулей, выходы группы которого соединены с соответствующими информационными входами группы регистра, выход которого соединен с вторым информационным входом первого мультиплексора, выход второго мультиплексора соединен с вторым адресным входом блока памяти,, первый и второй выходы которого соединены соответственно с входами вычитаемого группы вычнтателя по совокупности модулей и с входом слагаемого накапливающего сумматора, выход счетчика соединен с управляющим входом второго мультиплексораj, второй тактовый вход преобразователя соединен с управляющим входом первого мультиплексора, третий тактовый вход преобразователя соединен с вхо- дом разрешения вычитателя по совокупности модулей и с тактовым входом накапливающего сумматора.

0

5

ЯЙ

«аёп

Авторы

Даты

1990-02-07—Публикация

1988-04-04—Подача