I Изобретение относится к вычисли- (гельной технике и может быть нсполь- |зовано в устройствах обработки и пере ачи цифровой информагщи для преоб- разования чисел из непозиционного кода в позиционный.

Целью изобретения является упрощение устройства.

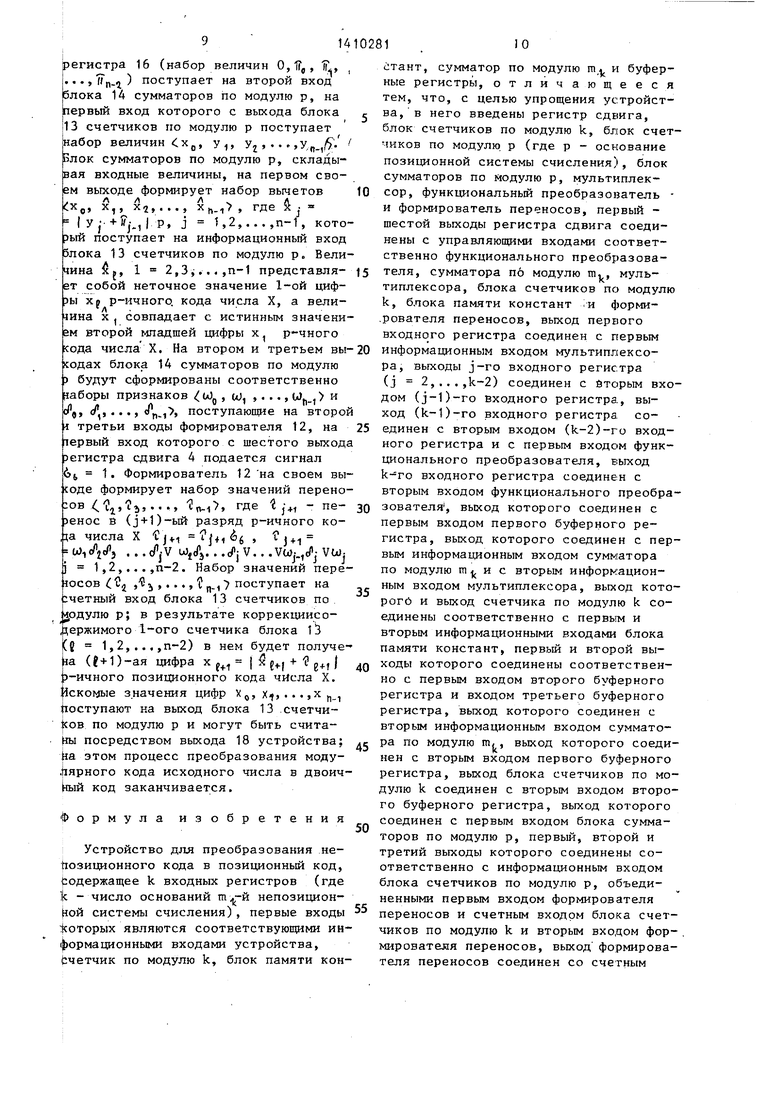

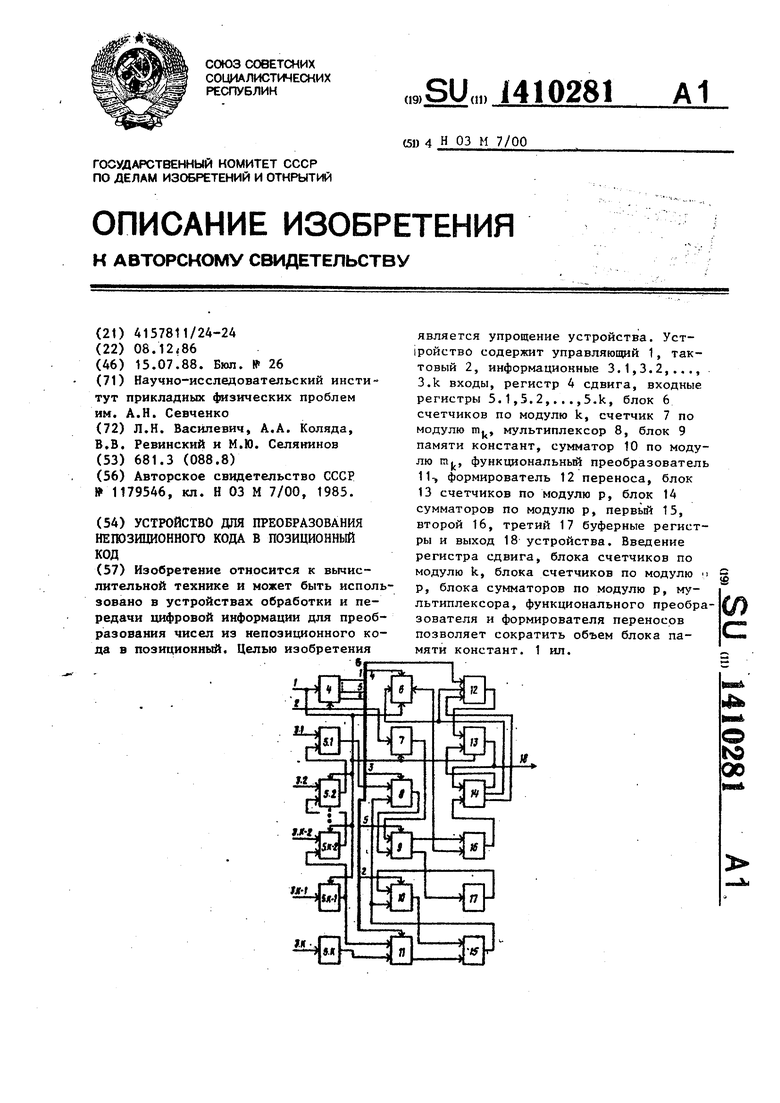

На чертеже представлена схема уст- зойства преобразования непозиционного кода в позиционный.

Устройство содержит управляющий 1, тактовый 2, информационные входы 3,1, 3.2,.,.,3.k устройства, регистр 4 сдвига, входные регистры 5.1, 5.2,... 5.k, блок 6 счетчиков по модулю k, ;четчик 7 по модулю k, мультиплексор 3, блок 9 памяти констант, сумматор 10 по модулю т, функциональный преоб эазователь 11, формирователь 12 пере- ;Носов, блок 13 счетчиков по модулю р, первый 15, второй 16, третий 17 буферные регистры и выход 18 устройства i Регистр сдвига имеет разрядность бит, единичный вход триггера младшего (нулевого) разряда регистра сдвига 4 и нулевые входы триггеров остальных разрядов регистра сдвига 4 в совокупности составляют его уста- новочный вход, который подключен к управляющему входу 1 устройства, управляющий вход сдвига регистра сдвига 4 соединен с тактовым входом 2 устройства. Прямой и инверсный выходы младшего разряда регистра сдвига 4 являются соответственно его первым и вторым выходами, прямой выход (k-1)- |ого разряда регистра сдвига 4 явля- ;ется его третьим выходом, прямой и и ;инверсный выходы k-oro разряда реги- ICTpa сдвига 4-являются соответствен- |но четвертым и пятым выходами регистра сдвига 4, прямой выход (k+1)-oro. :разряда регистра сдвига 4 является его шестым выходом. На каждом такте работы устройства по сигналу, подаваемому с тактового входа 2 устройства на вход управления сдвигом регистра сдвига 4, его содержимое сдвигается на один бит в сторону старших разрядов.

Разрядность i-oro входного регистра 5.1 составляет в бит (i 1,2,... k), где b , bi

через обозначается наименьшее целое число, не меньшее х; т,, m ,.. ., m { - основания модулярной системы

счисления, являющиеся попарно просты- и числами.

Блок памяти 9 для хранения коне- ; тант обладает емкостью 2 слов разрядностью n lopjp ;-(- bk бит; Т log.jkr, b р bij (i 1,2,..., k) n - количество цифр р-ичного представления числа-, п logrt(2M)r М - г

р, nijj - вспомогательньй модуль

П

е-о

выбираемый из условий т j ,

m j 7, 2 -m о +k-2 . В память блока 9 по

адресу (i-1)-t-2 х 5 записывается .набор

констант Vj , X ,, . .,., , R., i, 1,2,...,k, где х( , x(i) ,

(i

rt-t

(i) J,0

- цифры р-ичного представ -1

1

ления числа М: .., | М . -Х; |т

,2,...,k-i; xU), x(«i;...,x ;;jj, цифры р-ичного представления числа Х-М

k-1

где

t risf-lMu-Xil i.

1 :s

m

k

Ч- |м;,-: е

М п mj , Mj/mj

1,2,...,k-1 (1) (2)

ЧIv

если X f с m

.- m,, если X.7/m

через х обозначается ближайшее к х целое число, ,1,... ,т.-1J, i

9 9.Ч. f / Л

Цифры X -, .,,.,.,х ., р-ичного представления числа снимаются с первго вьгхода блока памяти 9 для хранения констант, на втором выходе которого формируется величина R, i 1,

J jlx.

Сумматор 10 по модулю m может быть реализован с помощью постоянного запоминающего устройства емкостью

,гвк

слов разрядностью b | бит (Ь

jlogjm), в память которого по адресу Х(+2 Y, записывается константа

2 V.k «tO b n-4функциональный преобразователь реализуется на основе постоянного запоминающего устройства, обладающего емкостью г слов разрядностью Ъ бит (bj j, j k-1, k). В его память по адресу Х 4-2 X записывается вычет

QC 1 RM+ Rfeh, « )-i4™™ ,.t -K-i

R,

r-1

k,

через IY I обозначается наименьший неотрицательный вычет, сравнимый с величиной Y по модулю т.

Блок 14 сумматоров по модулю р содержит п сумматоров по модулю р с формированием признаков переполнения и равенства суммы вычету р-1. Выходы суммы признака переполнения w , и

признака о, равенства суммы вычету р-1 i-oro сумматора (i 1,2,...,п) блока 14 являются соответственно первым, вторым и третьим выходами сумматора. Первые выходы всех сумматоров блока 14 в совокупности образуют первый выход блока 14, вторые выходы сумматоров с первого по (п-1)-ый блока 14 в совокупности образуют второй выход блока 14; третьи выходы сумматоров со второго по (п-1)-ый в совокупности образуют третий, выход блока 14.

Блок 6 счетчиков по модулю k содер жит п-1 счетчиков по модулю k. Входы об-нуления всех счетчиков блока 6 объединены и являются входом обнуления блока 6. Счетные входы счетчиков по модулю k блока 6 в совокупности образуют счетный вход блока 6.

Блок 13 счетчиков по модулю р содержит п счетчиков по модулю р; счетные входы счетчиков блока 13 с третьего по п-ый в совокупности образуют счетный вход блока 13; информационные входы всех счетчиков блока 13 в совокупности образуют его информационный вход.

Формирователь 12 переносов служит для формирования переносов ;., в )-ый разряд р-ичного кода числа ) где величина, подаваемая на первый вход формирователя 12 D jf, . u)icr3...(jV.... V U)i.,«fiV-(u. j 1,2,...,n-2.

Формирователь 12 может быть реализован с помощью п-2 формирователей переносов и группы из п-2 двухвходо- вых элементов И. .

Устройство работает следующим образом.

По сигналу р 1, подаваемому с управляющего входа 1 устройства на установочньй вход регистра сдвига 4, входы обнуления счетчика 7 по модулю k, блока 6 счетчиков по модулю k и блока 13 счетчиков по модулю р, а так

0

5

0

5

0

5

0

5

0

5

МОДУЛЯРНЬГЙ код (Х, Xj,..., Хц)

ходкого целого числа X из диапг

же на управляющие входы входных регистров 5.2,5.3,...,5.k-1, в младший (нулевой) разряд регистра сдвига 4 записывается единица, а остальные его разряды обнуляются; счетчик 7 по модулю k и счетчики, входящие в состав блоков 6 и 13, обнуляются,

) ис- диапазона модулярной системы счисления D -М, -М+1,...,М-1J через входы устройства 3.1,3.2,...,3.k записывается во входные регистры 5.1,5.2,...,5.k; после- чего начинается первый такт работы устройства; сигналы 6,, 6 .«., 6/ , вырабатываемые соответственно на выходах с первого по шестой регистра сдвига 4, являются управляющими сигналами.

На первом такте работы на управ- ляю1щ й вход мультиплексора 8 с третьего выхода регистра сдвига 4 поступ пает сигнал 6 О, в соответствии с чем содержимое х первого входного регистра 5.1 через первый информационный вход мультиплексора 8 поступает на первый информационный вход блока 9 памяти констант, на второй информационный вход которого с выхода счетчика 7 по модулю k поступает величина , на управляющий вход блока 9 памяти констант с пятого выхода регистра сдвига 4 поступает сигнал 6j 1; из блока 9 памяти констант по адресу О + , считывает(1|

X

М (1)

ся набор констант V , (.х . . . ,х , , R , . при зтом цифры X J , X , , ... ,х р-ичного представления числа М-1, fc.2lM ,-X J ,с первого блока 9 памяти констант передаются во второй буферный регистр 16 через первый его вход (на второй вход второго буферного регистра 16 поступает нулевая информация, так как 4 0), а вычет R запоминается в третьем буферном регистре 17. Одновременно с этим содержимые х . „ входного регистра 5.k-1 и X 1 входного регистра 5.k поступают соответственно на первый и второй информационные входы функционального преобразователя 11, на управляющий вход которого с первого выхода регистра сдвига 4 подается сигнал 6, 1, вычет Q, форми- руемьй на выходе функционального преобразователя 11 передается в первый буферный регистр 15 через второй его вход (на первый вход первого буфернэго регистра 15 в это время поступает нулевая информация, так как ) Кроме того,, на первом такте содержимое регистра входного 5,j пересылается в регистр 5.J-1 (на управляющий вкод входного регистра 5.J с управляющего входа 1 устройства поступает сигнал Г 0) для всех j 2,3,..., k-1; по сигналу Г 1, поступающему с тактового 2 входа устройства, содержимое регистра сдвига 4 сдвигается на один бит в сторону старших разрядов, а содержимое счетчика 7 по модулю k увеличивается на единицу.

На втором такте работы устройства содержимое R третьего буферного регистра 17 поступает на первьй вход сумматора 10 по модулю т, на второй Еход которого подается величина QQ с выхода первого буферного регистра 15, сумматор 10 по модулю т. находит вычет ( который запоминается в первом буферном регистре 15 (4 1, (oi 0). Содержимое второго буферного регистра 16 (набор цифр . Е-ИЧНОГО представления х , х ( j . ...,) поступает на второй вход Е лока 14 сумматоров по модулю р, на первый вход которого с выхода блока 3 счетчиков по модулю р поступает набор величины y j , У , У J,li ), гфичем У I О, j 0,1,...,п-1. Блок 4 сумматоров по модулю р, складывая по модулю р входные величины, на пер- юм своем выходе формирует набор вы- етов у(, у(,...,,, где у

ф jyV l , j 0,1,...,П-1, КС5форый поступает на информационный ход блока 13 счетчиков по модулю р, jjia счетньш вход которого с выхода фор 1 шрователя 12 переносов поступает наг (bop величин ,..., ,7, Г 0; 1 3,4,...,п ,( 0). Йа втором выходе блока 14 сумматоров ifio модулю р формируется набор двух- :&начных величин u)V , , ..., U) 7 где w j |( х(Я)(р, который пе- ;|)едается на счетный вход блока 6 Счетчиков по модулю k, при этом содер ;№мое (j + 1)-oro счетчика блока 6 уве- ,|1ичивается на 1, если w - 1 (j О 1,...,п-2).

Параллельно с изложенным на вто- такте работы на управляющий вход Мультиплексора 8 поступает сигнал 65 О, в соответствии с чем содер- teHMoe к первого входного регистра 5.1 поступает на второй информационный вход блока памяти 9, на первый информационный вход которого подается содержимое i 1 счетчика 7 по мо- дулю k. Из блока памяти 9 ( 6j 1)

чит

ti;

считывается набор констант V,

fit -i о

,...,х J;., , R2 , при этом цифры

,,.. . ,х ., р-ичного представления числа М (j,2 1 i fe-t i t 7

ся во второй буферный регистр 16 (), а вычет R записывается в третий вспомогательный регистр 17. Кроме этого,- на втором такте содержимое входного регистра 5.J пересылается в регистр 5.J-1 (Г, 0) для всех j ,., . ,k-1; содержимое регистра сдвига 4 сдвигается на один разряд в сторону старших разрядов, а содержимое счетчика 7 по модулю k увеличивается на единицу (Г 1).

На t-oM такте работы устройства (t 3,4,...,k-1) содержимое R.( . третьего буферного регистра 17 поступает на первый вход сумматора 10 по

модулю т,, на второй вход которого подается величина Q i.,c выхода первого буферного регистра 15; сумматор 10 по модулю т находит вычет Q ., (4-4 о горый запог-отнается в первом буферном регистре 15 (6-1 1 6i 0) . Содержимое второго буферного регистра 16 (набор цифр X (-, X J , .. ,,х 7р-ичного представления числа М , |М ,j . X.jJTn) поступа ет на второй вход блока 14 сумматоров по модулю р, на первый вход которого с выхода блока

0

13 счетчиков по модулю р поступает

Ai-ii V ( „(i- l.

набор величин

г ,

,у

где у

i- i

h-1

(fl

j IP, j 0,1,...g

n-1. Блок 14 сумматоров no модулю p складывая по модулю р входные величины,. на первом своем выходе формирует набор вьиетов у , у (, . . ., у где у) (у( + 0.1,..., п-1), который поступает на информационный вход блока 13 счетчиков по модулю р. Так как на данном такте , jTo с выхода формирователя 12 на счетный вход блока 13 счетчиков по модулю р поступает набор величин , v , ,,(-1-1; рпр i}( О (1 3 4

«,{ , -f-i U4J- J,4,...,,

n). На втором выходе блока 14 сумма- торов по модулю р формируется набор двухзначных величин (признаков переполнения) ,..... w .J-Jb,

гдеыМ

я О,1,...,n-2), который передается на счетный вход блока 6 счетчиков по модулю k; в (J + D-OM счетчике блока 6

формируется величина S j i. 5

Ы;

J

тупает на второй информационный вход блока памяти 9, на первый информа- ционный вход которого подается содержимое i k-1 счетчика 7 по модулю k. Из блока памяти 9 (6j 1)

представляющая собой сумму переполнений, произошедших при сложении по модулю р величин , х ,.,., х (J О,1,...,п-2). ТТараллельно с из- 0 ложенным на t-ом такте работы устройства на управляющий вход мультиплексора 8 поступает сигнал 6 О, в совается набор констант . ,

,((}

ответствии с чем содерзкимое х, перво- гистра 15 (набор цифр х , х

R, при этом цифры X ..., X р-ичного кода чиста 1.(Х)х хМJ .передаются во второй буферный регистр 15 (64 0).

На (k+1)-oM такте работы устройства содержимое второго буферного ре(Ь) V(U)

20

го входного регистра 5.1 поступает на15 второй информационный вход блока 9, на первый адре(;ный вход которого подается содержимое i t-1 счетчика 7 по модулю k. Из блока памяти 9 (бу 1) считывается набор констант V , X р , X ..,. ,х,, R, при этом цифры X , X ..., X J передаются во . второй буферный регистр 16 ( 6ц 0), а вычет RJ записывается в третий буферный регистр 17. Кроме этого на t-oM такте содержимое входного регистра 5.J пересылается в регистр 5.J-1 (Г 0) для всех j 2,3,..., k-1; содержимое регистра сдвига 4

U)

1

X i,.. /) поступает на второй вход блока 14 сумматоров по модулю р, на первый вход которого с выхода блока 13 счетчиков по модулю р поступает набор веу уШ ч У ф

Xfcl

н ,,.

Г

,(k)

V V S У л-t /

J

где 0,1,. ..,n-1. Блок

25

личин

/ff.

3 -t-. J 14 сумматоров по модулю р, складывая

по модулю р входные величины, на первом своем выходе формирует набор вычетов УО , У ,.,. ,У (,.,7, где у. lyW+ х(«|р (J 0,1,...,n-f), ко- торый поступает на информационный вхол блока 13 счетчиков. Так как на данном такте 6 О, то с выхода формисдвигается на один бит в сторону стар-30 рователя 12 на счетный вход блока 13

ших разрядов, а содержимое счетчика

7 по модулю k увеличивается на едисчетчиков по модулю р поступает набор

булевых величин , D J.... t .l

где , О (1 3,4,...,п).

ницу.

где , О (1 3,4,...,п).

u)

где

На (k-D-OM такте работы устройст- ром выходе блока 14 сумматоров по ва в первом буферном регистре 15 бу- 5 модулю р сформируется набор двухэнач- дет получен вычет Q j, совпадающий , ньрс. величин с машинным интервальным индексом исходного числа X.

Ч

Q.4 1(Х) (SlRjm,40

k

()1рУ( o,i::..,

п-2), который поступает на счетный вход блока 6 счетчиков по модулю k; в (j+1)-oM счетчике блока 6 формируre R i определяются формулами (1) и (2)4j 1,2,...,k); I(X)| ll|(X)v,, где I ((X) - интервальный индекс числа X, определяемый соот-дз изошедших при сложении по модулю р

. И/ V

V ется величина (i. i. w ;, представ

е

ющая собой сумму переполнении, про

ношением

(-f

X 1 М ;

1«1

i,k-l

м- ;,k-i

-,1

m.

величин , ,« . 7 (J 0, ...,п-2), Так как на данном такте управляющий вход блока 6 с четверт выхода регистра сдвига 4 поступает сигнал 1, то набор величин м « ь-г выхода блока 6 счет ков по модулю k передается через в рой вход во второй регистр 16 (6 в котором будет записан набор вели я . - р. Вычет у р совпа ет с младшей х р-ичного ко числа X.

На k-oM такте работы устройства выполняются действия, аналогичные описанным вьше на тактах со второго по (k-1)-ый. Отличие лишь состоит в том, что на k-OM такте на управляющий вход мультиплексора 8 поступает сигнал 6} 1, в соответствии с чем содержимое Q .5 1|((Х) первого буферного регистра 17 через второй информационный вход мультиплексора 8 пос

5

тупает на второй информационный вход блока памяти 9, на первый информа- ционный вход которого подается содержимое i k-1 счетчика 7 по модулю k. Из блока памяти 9 (6j 1)

0 вается набор констант . ,

,((}

гистра 15 (набор цифр х , х

R, при этом цифры X ..., X р-ичного кода чиста 1.(Х)х хМJ .передаются во второй буферный регистр 15 (64 0).

На (k+1)-oM такте работы устройства содержимое второго буферного ре(Ь) V(U)

гистра 15 (набор цифр х , х

0

5

U)

1

X i,.. /) поступает на второй вход блока 14 сумматоров по модулю р, на первый вход которого с выхода блока 13 счетчиков по модулю р поступает набор веу уШ ч У ф

Xfcl

н ,,.

Г

,(k)

V V S У л-t /

J

где 0,1,. ..,n-1. Блок

личин

/ff.

3 -t-. J 14 сумматоров по модулю р, складывая

15

25

счетчиков по модулю р поступает набор

булевых величин , D J.... t .l

где , О (1 3,4,...,п).

На ВТОром выходе блока 14 сумматоров по модулю р сформируется набор двухэнач- ньрс. величин

u)

где

ром выходе блока 14 сумматоров по модулю р сформируется набор двухэнач- , ньрс. величин

изошедших при сложении по модулю р

()1рУ( o,i::..,

п-2), который поступает на счетный вход блока 6 счетчиков по модулю k; в (j+1)-oM счетчике блока 6 формируVется величина (i. i. w ;, представля е

ющая собой сумму переполнении, проз изошедших при сложении по модулю р

. И/ V

0

величин , ,« . 7 (J 0,1, ...,п-2), Так как на данном такте на управляющий вход блока 6 с четвертого выхода регистра сдвига 4 поступает сигнал 1, то набор величин м ,, , « ь-г выхода блока 6 счетчиков по модулю k передается через второй вход во второй регистр 16 (6 0) в котором будет записан набор величин я . - р. Вычет у р совпадает с младшей х р-ичного кода числа X.

На заключительном (k+2)-oM такте работы устройства содержимое второго

регистра 16 (набор величин О,, , , ..., /Гр. ) поступает на второй вход блока 14 сумматоров по модулю р, на первый вход которого с выхода блока 13 счетчиков по модулю р поступает набор величин Хд, у,, У , .. . ,У,„.,. Блок сумматоров по модулю р, складывая входные величины, на первом своем выходе формирует набор вычетов . л л - Л (.х, X,, х,,. .., х.1 , где и j.

(У/ + и/и Р. J 1,2,...,п-1, который поступает на информационный вход блока 13 счетчиков по модулю р. Величина , 1 2,3j...,n-1 представля- 15 теля, сумматора по модулю т., муль{ет собой неточное значение 1-ой цифэы хр р-ичного. кода числа X, а величина X , совпадает с истинным значениk типлексора, блока счетчиков по модулю

k, блока памяти констант -и форми- .рователя переносов, выход первого входного регистра соединен с первым

ИМ второй мпадшей цифры х р-чного кода числа X. На втором и третьем вы-20 информационным входом мультиплексо- содах блока 14 сумматоров по модулю ра, выходы j-ro входного регистра э будут сформированы соответственно (j 2,...,k-2) соединен с йторым вхо- Каборы признаков (A)J, ьо, ,...,W., и дом (j-l)-ro входного регистра, вы- (/ ,, / ,,,..,«/ „.,, поступающие на второй ход (k-l)-ro входного регистра со- i третьи входы формирователя 12, на 25 единен с вторым входом (k-2)-ro вход- первый вход которого с шестого выхода ного регистра и с первым входом функ- зегистра сдвига 4 подается сигнал ционального преобразователя, Е1ыход 6(, 1. Формирователь 12 на своем вы- k-ro входного регистра соединен с оде формирует набор значений перено- вторым входом функционального преобра- :ов J., , .. ,, iln-i, где i у+, - пе- зО зователя , выход которого соединен с ренос в (+1)-ый разряд р-ичного ко- первым входом первого буферного регистра, выход которого соединен с первым информационным входом сумматора по модулю т и с вторым информационным входом мультиплексора, выход которого и выход счетчика по модулю k соединены соответственно с первым и вторым информационными входами блока памяти констант, первый и второй вы40

да числа X Dj., J+i Wi . .. (/ j.V и),(Л,. ... V. .. VWj./j VCOj i 1,2,...,n-2. Набор значений переносов Dj , 5 ,..., С p., 7 поступает на :четный вход блока 13 счетчиков по модулю р; в результате коррекциисо- держимого 1-ого счетчика блока 13 { 1,2,...,п-2) в нем будет получе35

аа (+1)-ая цифра х р | 5 {.( + (,., |

е-и I г+1 -ичного позиционного кода числа X.

icKOMbie значения цифр х.

х„

П-1

поступают на выход блока 13 .счетчи- icoB по модулю р и могут быть считаходы которого соединены соответственно с первым входом второго буферного регистра и входом третьего буферного регистра, выход которого соединен с вторым информационным входом сумматоliTaHT, сумматор по модулю т, и буферные регистры, отлич ающееся тем, что, с целью упрощения устройства, в него введены регистр ,

блок счетчиков по модулю k, блок счетчиков по модулю, р (где р - основание позиционной системы счисления), блок сумматоров по модулю р, мультиплексор, функциональный преобразователь - и формирователь переносов, первый - шестой выходы регистра сдвига соединены с управляющими входами соответственно функционального преобразователя, сумматора по модулю т., мультеля, сумматора по модулю т., мульk типлексора, блока счетчиков по модулю

k, блока памяти констант -и форми- рователя переносов, выход первого входного регистра соединен с первым

информационным входом мультиплексо- ра, выходы j-ro входного регистра (j 2,...,k-2) соединен с йторым вхо- дом (j-l)-ro входного регистра, вы- ход (k-l)-ro входного регистра со- единен с вторым входом (k-2)-ro вход- ного регистра и с первым входом функ- ционального преобразователя, Е1ыход k-ro входного регистра соединен с вторым входом функционального преобра- зователя , выход которого соединен с первым входом первого буферного регистра, выход которого соединен с первым информационным входом сумматора по модулю т и с вторым информационным входом мультиплексора, выход которого и выход счетчика по модулю k соединены соответственно с первым и вторым информационными входами блока памяти констант, первый и второй выходы которого соединены соответственно с первым входом второго буферного регистра и входом третьего буферного регистра, выход которого соединен с вторым информационным входом суммато

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Преобразователь непозиционного кода в позиционный код | 1984 |

|

SU1481895A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Устройство для нормализации чисел в модулярном коде | 1984 |

|

SU1242942A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки и передачи цифровой информации для преобразования чисел из непозиционного кода в позиционный. Целью изобретения в Г HiFez является упрощение устройства. Уст- 1ройство содержит управляющий 1, тактовый 2, информационные 3.1,3.2,..., 3.k входы, регистр 4 сдвига, входные регистры 5.1,5.2,...,5.k, блок 6 счетчиков по модулю k, счетчик 7 по модулю mj, мультиплексор В, блок 9 памяти констант, сумматор 10 по модулю т|, функциональный преобразователь 11-, формирователь 12 переноса, блок 13 счетчиков по модулю р, блок 14 сумматоров по модулю р, первый 15, второй 16, третий 17 буферные регистры и выход 18 устройства. Введение регистра сдвига, блока счетчиков по модулю k, блока счетчиков по модулю р, блока сумматоров по модулю р, мультиплексора, функционального преобразователя и формирователя переносов позволяет сократить объем блока памяти констант. 1 ил. rvd оо

ры посредством выхода 18 устройства; де ра по модулю т,, выход которого соедиha этом процесс преобразования моду- .Ьярного кода исходного числа в двоич- йый код заканчивается.

Формула изобретения

Устройство для преобразования не- tIoзищ oннoгo кода в позиционный код, Содержащее k входных регистров (где k - число оснований непозицион50

нен с вторым входом первого буферного регистра, выход блока счетчиков по модулю k соединен с вторым входом второго буферного регистра, выход которого соединен с первым входом блока сумматоров по модулю р, первый, второй и третий выходы которого соединены соответственно с информационным входом блока счетчиков по модулю р, объединенными первым входом формирователя

1ой системы счисления) , первые входы переносов и счетным входом блока счет- :|соторых являются соответствующими ин- чиков по модулю k и вторым входом фор- , формационными входами устройства, Счетчик по модулю k, блок памяти конмирователя переносов, выход формирователя переносов соединен со счетным

нен с вторым входом первого буферного регистра, выход блока счетчиков по модулю k соединен с вторым входом второго буферного регистра, выход которого соединен с первым входом блока сумматоров по модулю р, первый, второй и третий выходы которого соединены соответственно с информационным входом блока счетчиков по модулю р, объединенными первым входом формирователя

переносов и счетным входом блока счет- чиков по модулю k и вторым входом фор-

переносов и счетным входом блока счет- чиков по модулю k и вторым входом фор-

мирователя переносов, выход формирователя переносов соединен со счетным

и141028112

входом блока счетчиков по модулю р,чика по модулю k и блока счетчиков

выход которого соединен с вторым вхо-по модулю р объединены и подключены

дом блока сумматоров по модулю р ик управляющему входу устройства, вход

является выходом устройства, устано- сдвига регистра сдвига объединен со

вочный вход регистра сдвига, управляю-счетным входом счетчика по модулю k .

щие входы J-X входных регистров (j р подключен к тактовому входу устрой-0 2,...,k-1), входы обнуления счет-ства.

| Авторское свидетельство СССР 1179546, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-07-15—Публикация

1986-12-08—Подача