Сри.2

Изобретение относится к вычислительной технике и может быть использовано в ЦЭВМ, функционирующих в системе счисления в остаточных классах (ССОК) для пре- образования ч.исел, представленных в ССОК, в позиционный код,

Целью изобретения является уменьшение продолжительности вычислений за счет использования конвейерной структуры при построении преобразователя.

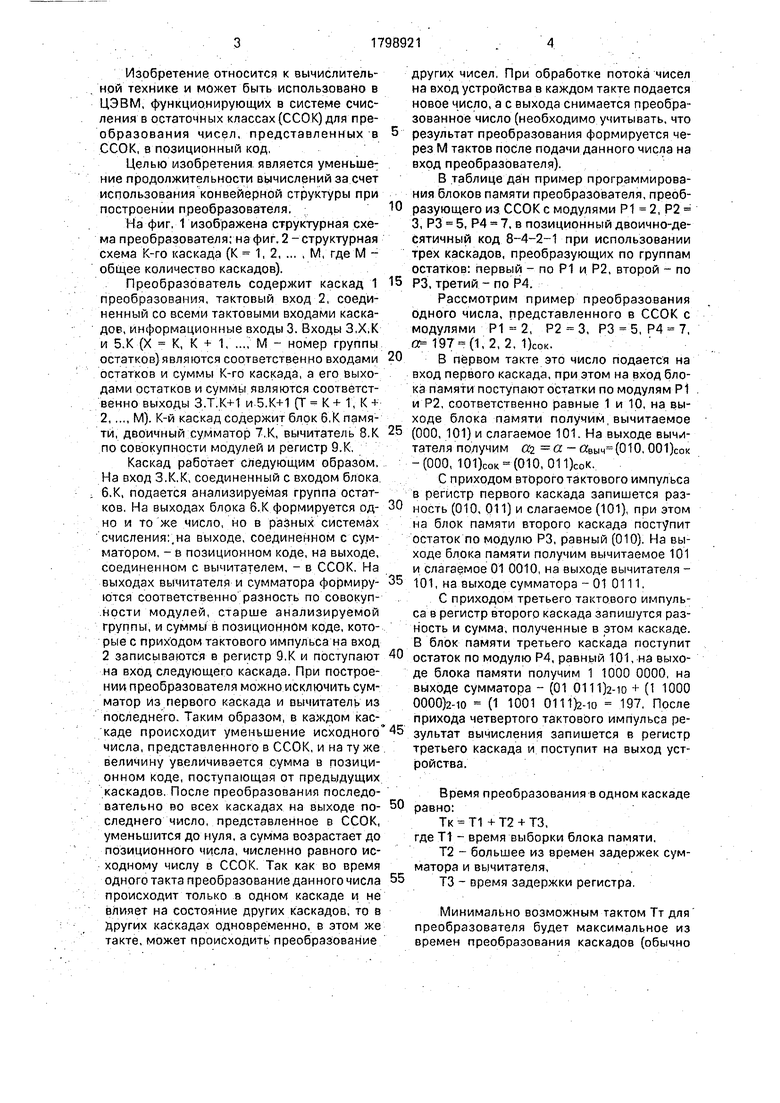

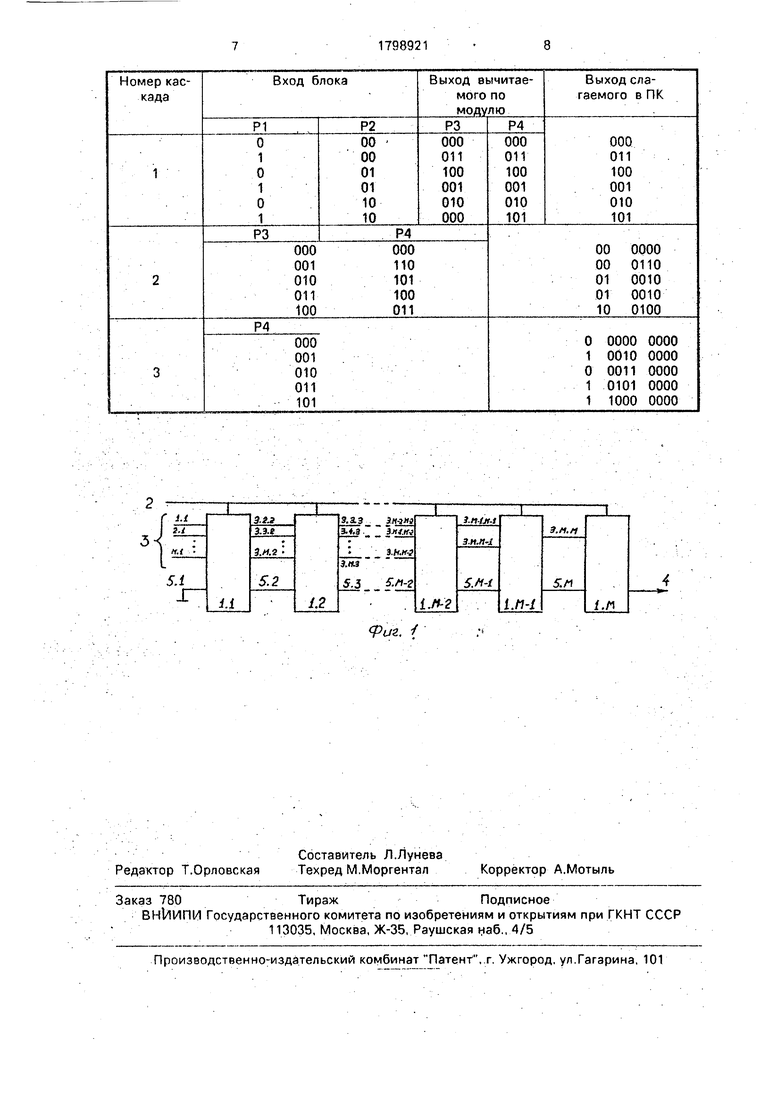

На фиг, 1 изображена структурная схема преобразователя: на фиг. 2 -структурная схема К-го каскада (К 1, 2, ... , М, где М - общее количество каскадов).

Преобразователь содержит каскад 1 преобразования, тактовый вход 2, соединенный со всеми тактовыми входами каскадов, информационные входы 3. Входы З.Х.К и 5.К (X К, К + 1, ..., М - номер группы остатков) являются соответственно входами остатков и суммы К-го каскада, а его выходами остатков и суммы являются соответственно выходы З.Т.К+1 и 5.К+1 (Т К+ 1, К + 2,..,, М). К-й каскад содержит блок 6.К памяти, двоичный сумматор 7.К, вычмтатель 8.К по совокупности модулей и регистр 9.К,

Каскад работает следующим образом. На вход З.К.К, соединенный с входом блока, б.К, подается анализируемая группа остатков, На выходах блока 6.К формируется одно и то же число, но в разных системах счисления:,на выходе, соединенном с сумматором, - в позиционном коде, на выходе, соединенном с вычитателем, - в ССОК. На выходах вычитателя и сумматора формируются соответственно разность по совокупности модулей, старше анализируемой группы, и суммы в позиционном коде, которые с приходом тактового импульса на вход 2 записываются в регистр 9.К и поступают на вход следующего каскада. При построении преобразователя можно исключить сумматор из первого каскада и вычитатель из последнего. Таким образом, в каждом каскаде происходит уменьшение исходного числа, представленного в ССОК, и на ту же величину увеличивается сумма в позиционном коде, поступающая от предыдущих каскадов. После преобразования последовательно во всех каскадах на выходе последнего число, представленное в ССОК, уменьшится до нуля, а сумма возрастает до позиционного числа, численно равного исходному числу в ССОК. Так как во время одного такта преобразование данного числа происходит только в одном каскаде и не влияет на состояние других каскадов, то в других каскадах одновременно, в этом же такте, может происходить преобразование

других чисел, При обработке потока чисел на вход устройства в каждом такте подается новое число, а с выхода снимается преобразованное число (необходимо учитывать, что

результат преобразования формируется через М тактов после подачи данного числа на вход преобразователя).

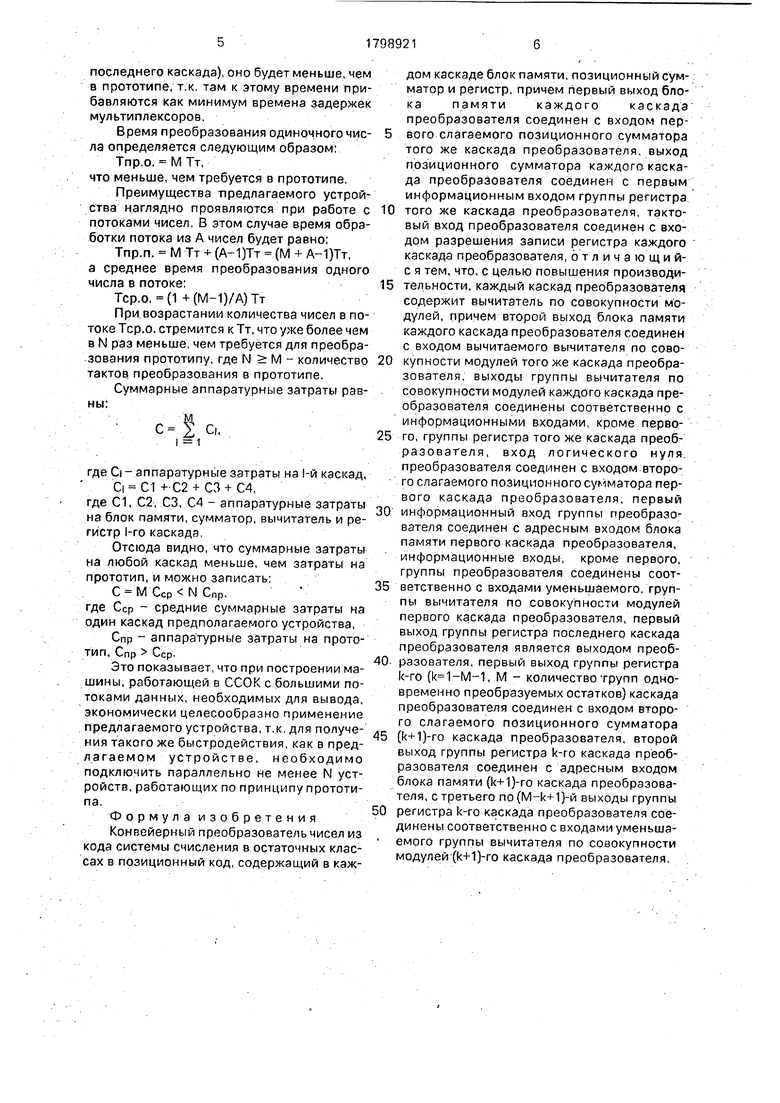

В таблице дан пример программирования блоков памяти преобразователя, преобразующего из ССОК с модулями Р1 2, Р2 3, РЗ 5, Р4 7, в позиционный двоично-десятичный код 8-4-2-1 при использовании трех каскадов, преобразующих по группам остатков: первый - по Р1 и. Р2, второй - по

рз, третий - по РА.

Рассмотрим пример преобразования одного числа, представленного в ССОК с модулями Р1 2, Р2 3, Р3 5, Р4 7, а 197(1,2,2, 1)сок.

в первом такте это число подается на вход первого каскада, при этом на вход блока памяти поступают остатки по модулям Р1 и Р2, соответственно равные 1 и 10, на выходе блока памяти получим,вычитаемое

(000, 101) и слагаемое 101. На выходе вычитателя получим «2 -О- -#выч(010, 001)сок -(000, 101)сок (010, 011)сок.

С приходом второго тактового импульса в регистр первого каскада запишется разность (010, 011) и слагаемое (101), при этом на блок памяти второго каскада поступит остаток по модулю РЗ, равный (010). На выходе блока памяти получим вычитаемое 101 и слагаемое 01 0010, на выходе вычитателя Ю1, на выходе сумматора - 01 0111.

С приходом третьего тактового импульса в регистр второго каскада запишутся разность и сумма, полученные в этом каскаде. В блок памяти третьего каскада поступит

остаток по модулю Р4, равный 101, на выходе блока памяти получим 1 1000 0000, на выходе сумматора - (01 0111)2-ю + (1 1000 OOOOJ2-10 О 1001 0111)2-10 197. После прихода четвертого тактового импульса результат вычисления запишется в регистр третьего каскада и поступит на выход устройства.

Время преобразования в одном каскаде равно:

Тк Т1 + Т2 + ТЗ, где Tt - время выборки блока памяти.

Т2 - большее из времен задержек сумматора и вычитателя, ТЗ - время задержки регистра.

Минимально возможным тактом Тт для преобразователя будет максимальное из времен преобразования каскадов (обычно

последнего каскада), оно будет меньше, чем в прототипе, т.к. там к этому времени прибавляются как минимум времена задержек мультиплексоров,

Время преобразования одиночного числа определяется следующим образом:

Тпр.о. М Тт, что меньше, чем требуется в прототипе.

Преимущества предлагаемого устройства наглядно проявляются при работе с потоками чисел. В этом случае время обработки потока из А чисел будет равно:

Тпр.п. М Тт + (А-1)Тт (М + А-1)Тт. а среднее время преобразования одного числа в потоке:

Тср.о. (1 +(М-1)/А)Тт

При.возрастании количества чисел в потоке Тср.о. стремится к Тт, что уже более чем в N раз меньше, чем требуется для преобразования прототипу, где N М - количество тактов преобразования в прототипе.

Суммарные аппаратурные затраты равны:

c-lc,.

. I 1

где Ci - аппаратурные затраты на 1-й каскад,

Ci C1+-C2 + C3 + C4, где С1. С2, СЗ, С4 - аппаратурные затраты на блок памяти, сумматор, вычитатель и регистр 1-го каскада.

Отсюда видно, что суммарные затраты на любой каскад меньше, чем затраты на прототип, и можно записать:

С М Сер N СПр.

где Сер - средние суммарные затраты на один каскад предполагаемого устройства,

СПр - аппаратурные затраты на прототип, Спр Сер.

Это показывает, что при построении машины, работающей в ССОК с большими потоками данных, необходимых для вывода, экономически целесообразно применение предлагаемого устройства, т.к. для получения такого же быстродействия, как в предлагаемом устройстве, необходимо подключить параллельно не менее N устройств, работающих по принципу прототипа.

Формула изобретения

Конвейерный преобразователь чисел из кода системы счисления в остаточных классах в позиционный код, содержащий в каждом каскаде блок памяти, позиционный сумматор и регистр, причем первый выход блока памяти каждого каскада преобразователя соединен с входом пёр- 5 вого слагаемого позиционного сумматора того же каскада преобразователя, выход позиционного сумматора каждого каскада преобразователя соединен с первым информационным входом группы регистра.

0 того же каскада преобразователя, тактовый вход преобразователя соединен с входом разрешения записи регистра каждого каскада преобразователя, отличающий- с я тем, что, с целью повышения производи5 тедьности, каждый каскад преобразователя содержит вычитатель по совокупности м о- дулей, причем второй выход блока памяти каждого каскада преобразователя соединен с входом вычитаемого вычитателя по сово0 купности модулей того же каскада преобразователя, выходы группы вычитателя по совокупности модулей каждого каскада преобразователя соединены соответственно с информационными входами, кроме перво5 го, группы регистра того же каскада преобразователя, вход логического нуля, преобразователя соединен с входом.второ- го слагаемого позиционного сумматора первого каскада преобразователя, первый

0 информационный вход группы преобразователя соединен с адресным входом блока памяти первого каскада преобразователя, информационные входы, кроме первого, группы преобразователя соединены соот5 вететвенно с входами уменьшаемого, группы вычитателя по совокупности модулей первого каскада преобразователя, первый выход группы регистра последнего каскада преобразователя является выходом преоб0 разователя, первый выход группы регистра k-го (к 1-М-1, М - количество трупп одновременно преобразуемых остатков) каскада преобразователя соединен с входом второго слагаемого позиционного сумматора

5 (k+1)-ro каскада преобразователя, второй выход группы регистра k-ro каскада преобразователя соединен с адресным входом блока памяти (k+1)-ro каскада преобразователя, с третьего no(M-k-M)-n выходы группы

0 регистра k-ro каскада преобразователя соединены соответственно с входами уменьшаемого группы вычитателя по совокупности модулей (k+1)-ro каскада преобразователя.

Фиг. /

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Преобразователь чисел из кода системы счисления в остаточных классах в двоичный код | 1988 |

|

SU1541783A1 |

| Преобразователь позиционного кода в код системы остаточных классов | 1986 |

|

SU1376245A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Специализированный процессор | 1977 |

|

SU684550A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1986 |

|

SU1388996A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1987 |

|

SU1587503A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1989 |

|

SU1793546A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЛА ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД | 2002 |

|

RU2235423C2 |

Изобретение относится к области вычислительной техники и может быть использовано в аппаратуре, функционирующей в позиционно-остаточных системах счисления, Целью изобретения является повышение производительности. Преобразователь содержит в каждом каскаде 1 блок 6 памяти, позиционный сумматор 7, регистр 9 и вычи- татель 8 по совокупности модулей 2 ил.

| Преобразователь чисел из кода системы счисления в остаточных классах в двоичный код | 1988 |

|

SU1541783A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода из системы остаточных классов в двоичный код | 1980 |

|

SU947850A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь непозиционного кода в позиционный код | 1984 |

|

SU1481895A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-02-28—Публикация

1990-01-08—Подача