ел

U

со ел ел

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Система передачи и приема цифровой информации | 1985 |

|

SU1288923A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Декодер балансного кода | 1990 |

|

SU1795556A1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Преобразователь последовательного кода в параллельный | 1989 |

|

SU1795557A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

Изобретение относится к радиотехнике. Цель изобретения - сокращение времени синхронизации для передачи двоичной адресной информации. Устройство содержит на передающей стороне кодер 1, г-р 2 тактовых импульсов, блок параллельного объединения 3, г-р 4 M-последовательности, дискретный канал 5 связи, на приемной стороне г-р 6 тактовых импульсов, регистры 7 и 9 сдвига, эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 8, регенератор 10 кодового слова, обнаружитель 11 безошибочного участка, формирователь 12 управляющих сигналов и блок 13 восстановления сигнала цикловой синхронизации. На передающей стороне адресную информацию преобразуют в кодовую последовательность, которая через канал 5 поступает на приемную сторону, где она записывается со скоростью, превышающей в N раз скорость ее передачи. Это позволяет при отсутствии тактовой синхронизации с принимаемой кодовой последовательностью получать N отсчетов за длительность одного кодового символа. После соответствующих преобразований принятая адресная информация поступает к получателю. 2 ил.

ФигА

Изобретение относится к радиотех- i нике, а именно к устройствам передачи дискретной информации, и может быть использовано в системах радиотелефонной связи для передачи двоичной адресной информации.

Цель изобретения - сокращение вре- Иени синхронизации для передачи двоичной адресной информации.

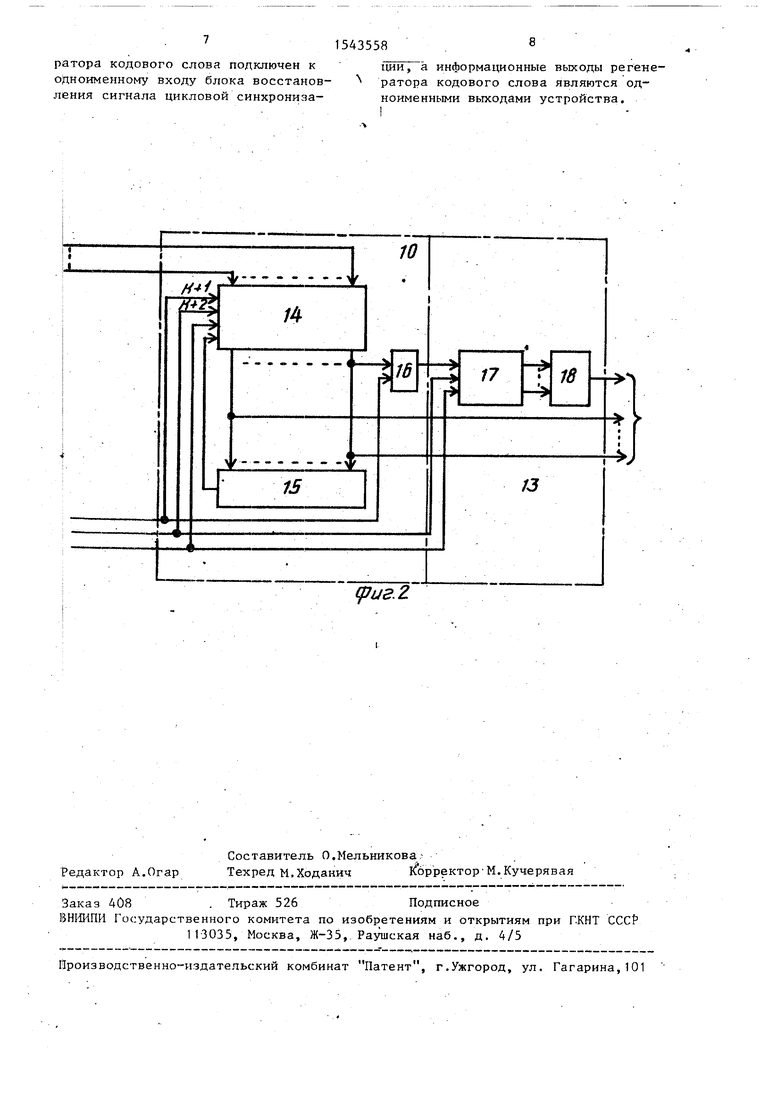

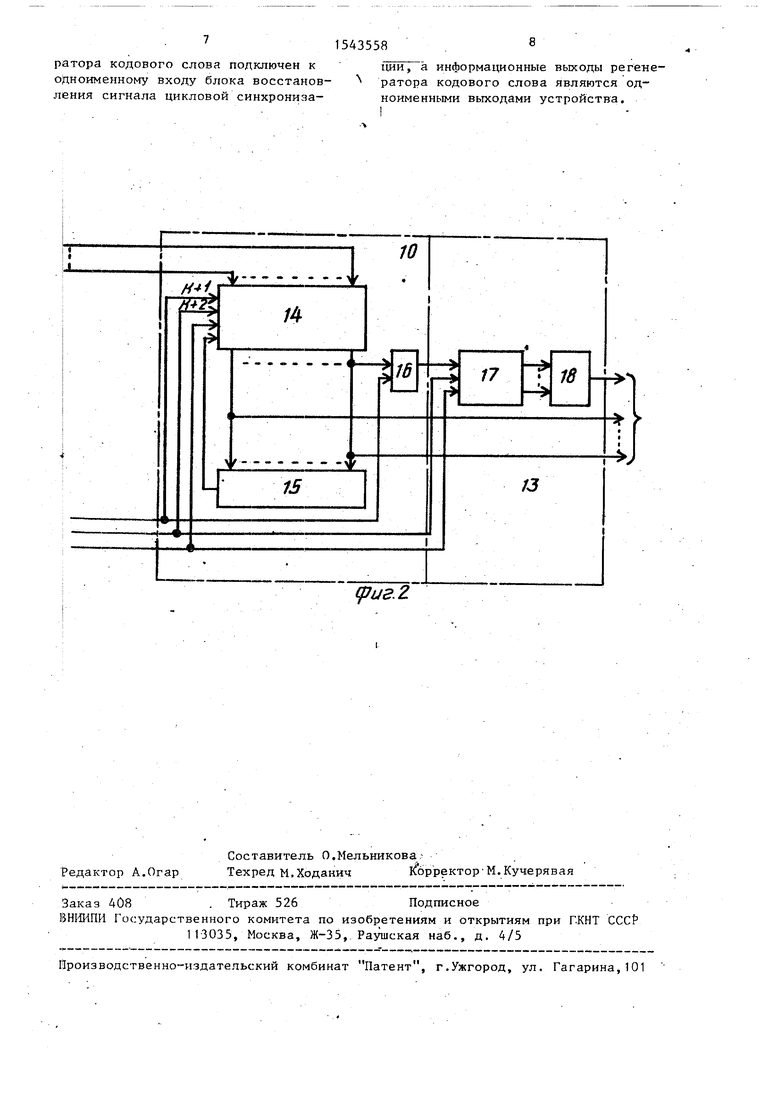

На фиг. 1 представлена структурная схема устройства синхронизации для передачи двоичной адресной информации} на фиг. 2 - структурные схемы регенератора кодового слова )и блока 13 восстановления сигнала Цикловой синхронизации.

Устройство синхронизации для пере- ачи двоичной адресной информации со- ;ержит на передающей стороне кодер

генератор 2 тактовых импульсов, лок 3 параллельного объединения, енератор 4 М-последовательности и 1скретный канал 5 связи, а на прием- шй стороне - генератор 6 тактовых импульсов, первый регистр 7 сдвига, Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, второй регистр 9 сдвига, регенератор 10 кодового слова, обнаружитель 11 безоши- 0очного участка, формирователь 12 управляющих сигналов и блок 13 вое- Становления сигнала цикловой синхронизации.

Регенератор 10 кодового слова образуют регистр 1Д, элемент ИСКЛЮЧАЮ- llj(EE ИЛИ 15 и элемент И 16.

Блок 13 восстановления сигнала цикловой синхронизации содержит регистр 17 с обратными связями и эле- ьЦент 18 совпадения.

Устройство синхронизации для передачи двоичной адресной информации работает следующим,образом.

Адресную информацию через первые входы записывают в кодер 1, одновременно на второй вход кодера 1 подают управляющий сигнал от источника адресной информации, а на третий вход - тактовые импульсы с выхода генератора 2. Затем адресную информацию циклически кодируют и последовательность периодически повторяемых информационных и проверочных двоичных символов циклического (n, k + га)-кода подают н|а первый вход блока 3, на второй вход которого синхронно подают периодически повторяемую М-последователь- нюсть с выхода генератора 4. Полученную таким образом кодовую последе-

0

5

0

5

0

5

0

5

0

5

вательность с выхода блока 3 подают на вход дискретного канала 5 связи, с выхода которого кодовую последовательность подают на вход регистра 7 и на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8. В регистре 7 кодовую последовательность записывают со скоростью, в N раз превышающей скорость ее передачи, под действием тактовых импульсов, которые поступают с выхода генератора 6 на второй вход формирователя 12 и с первого выхода последнего - на второй вход регистра 7. Это позволяет при отсутствии тактовой синхронизации с принимаемой кодовой последовательностью получать N отсчетов за длительность одного кодового символа и соответственно N отсчетов участка кодовой последовательности, которые параллельно подают на первые входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, с выхода которого инверсные двоичные символы синдрома последовательно записывают через первый вход в регистр 9, с выходов которого полученную инверсию синдрома подают на входы обнаружителя 11. Если участок кодовой последовательности, записанный после очередного сдвига в регистр 7, не содержит ошибок, то в регистре 9 будут записаны только двоичные единицы. Присутствие 1 одновременно на всех входах обнаружителя 11 приводит к изменению из О в 1 логического уровня на его выходе, откуда указанный перепад поступает па первый управляющий вход формирователи 12, при этом запрещается подача тактовых импульсов с выхода формирователя 12 на тактовые входы регистров 7 и 9 сдвига. Изменение логического уровня на выходе обнаружителя 11 разрешает подачу тактовых импульсов -с тактового входа формирователя 12 на его второй тактовый выход. При этом с первого управляющего выхода формирователя 12 на (К+1)-й вход регистра 14 регенератора tO поступает управляющий сигнал) и в указанный регистр с выходов регистра 7 переписывают безошибочный . участок кодового слова адресной информации и затем сдвигают под действием тактовых импульсов, которые подают с второго тактового выхода формирователя 12 на (К+2)-й вход регистра 14 и на второй вход регистра 17, при этом с К-го выхода регистра 17 кодовая последовательность поступает

10

15

25

51543558

на первый вход элемента И 16. При дер, этом в блоке 13 кодовая последовательность поступает с выхода элемента И 1ё на первый вход регистра 17, ас вы- . ходов последнего - на входы элемента 18 совпадения. После п сдвигов на выходах регистра 17 получают набор двоичных символов, который соответствует циклической задержке информационных символов в обнаруженном безошибочном участке кодовой последовательности, и на управляющий вход элемента И с второго управляющего выхода формирователя 12 подают сигнал, запрещающий поступление двоичных символов с К-го выхода регистра 14 на Л первый вход регистра 17. Затем содержимое регистров 14 и 17 сдвигают синхронно п, п раз, пока двоичный набор из К символов на выходах регистра 17 не совпадает с известным на приемной cTopd&e набором такой же длины, при этом происходит изменение логического уровня из О в 1 на выходе элемента 18 и принятая адресная информация с выходов регистра 14 поступает к получателю адресной информации. Указанный сигнал также поступает через второй управляющий вход формирователя 12, при этом с третьего управляющего выхода формирователя 12 на управляющие входы регистров 7 и 9 поступает сигнал, который переводит содержимое их ячеек в состояние О.

Уровень О с выходов указанных регистров поступает в обнаружитель 11, затем через последний проходит на первый управляющий вход формирователя 12 и с второго управляющего выхода формирователя 12 на объединенные управляющие входы регистра 14 и ре- гистра 17 поступает сигнал, который переводит содержимое ячеек указанных регистров в состояние О. При этом на выходе элемента 18 совпадения происходит изменение логического уровня из 1 в О, в результате чего формирователь 12 переводит устройст- 50 во в исходное состояние.

тактовые входы двух последних объединены и подключены к выходу ГШ; объединенные управляющие входы генератора М-последовательности и кодера являются управляющим входом устройства, другие входы кодера являются адресными входами устройства, а на приемной стороне - последовательно соединенные ГТИ и формирователь управляющих сигналов, а также блок восстановления сигнала цикловой синхронизации, управляющий выход которого является одноименным выходом устройству и объединен с первым управляющим входом формирователя управляющих сигналов, отличающееся тем, что, с целью сокращения времени синхронизации для передачи двоичной 2Q адресной информации, на передающей стороне введена схема параллельного объединения, входы и выход которой подключены соответственно к выходам генератора М-последовательности и кодера и к входу дискретного канала связи, а на приемной стороне введены последовательно соединеные первый

регистр сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй регистр сдвига, обнаружитель безошибочного участка и регенератор родового слова. К входов, которого объединены с соответствующими К выходами первого регистра сдвига, информационный вход которого объединен с одноименным входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и подключен к выходу дискретного канала связи, тактовый и управляющий входы первого регистра сдвига объединены, с одноименными входами второго регистра сдвига и подключены к первым тактовому и управляющему входам формирователя управляющих сигналов, второй управляющий вход которого подключен к одноименному выходу обнаружителя безошибочного участка, второй тактовый, второй и третий управляющие выходы формирователя управляющих сигналов подключены соответственно

к объединенным (К+2)-му и тактовому входам регенератора кодового слова и блока восстановления сигнала цикловой синхронизации, к (К+1)-му входу

Устройство синхронизации для пере- 55 Регенератора кодового слова и к дачи двоичной адресной информации, объединенным управляющим входам ре- содержащее на передающей стороне ге- генератора кодового слова и блока нератор тактовых импульсов (ГТИ), восстановления сигнала цикловой синх- генератор М-последовательности и ко- ронизации, сигнальный выход регене30

35

40

45

ормула изобретения

10

2Q

15

2Q

25

2Q

30

35

50

40

50

45

ратора кодового слова подключен к одноименному входу блока восстановления сигнала цикловой синхронизации, а информационные выходы регенератора кодового слова являются одноименными выходами устройства.

фиг. 2

| Патент США К 4001693, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-02-15—Публикация

1987-08-13—Подача