(21)4435312/24-24

(22)01.06.88

(46) 23.04.90. Бюл. К 15

(72) А.В. Ткаченко, О.И. Бондарь

и С.Ю. Мукатин

(53)681.3(088.8)

(56)Авторское свидетельство СССР № 1363188, кл. G 06 F 7/49, 1986.

Авторское свидетельство СССР № 1427573, кл. Н 03 М 7/30, 25.03.87.

(54)КОМБИНАЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ФОРМ КОДА

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано в гибких АСУ

и ЭВМ для преобразования минимальной формы t -системы счисления в двоичный ряд чисел. Изобретение позволяет расширить область применения за счет преобразования минимальной формы t -системы счисления в двоичную систему счисления. Преобразователь содержит входы , три элемента И 2{-2э, четыре элемента ИЛИ ., шесть сумматоров 3/-3g по модулю два и выходы преобразователя. При подаче сигнала на входы 1 «-l К°Д минимальной формы посредством элементов И и сумматоров по модулю цва преобразуется в двоичный код на выходах 5t-5q.. 1 ил., 1 табл.

с SS

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодовых форм | 1988 |

|

SU1545329A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Накапливающий сумматор | 1986 |

|

SU1401453A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДОВ | 1991 |

|

RU2023347C1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в гибких АСУ и ЭВМ для преобразования минимальной формы T1-системы счисления в двоичный ряд чисел. Изобретение позволяет расширить область применения за счет преобразования минимальной формы T1-системы счисления в двоичную систему счисления. Преобразователь содержит входы 11 - 17, три элемента И 21 - 23, четыре элемента ИЛИ 41 - 44, шесть сумматоров 31 - 36 по модулю два и выходы 51 - 54 преобразователя. При подаче сигнала на входы 11 - 17 код минимальной формы посредством элементов И и сумматоров по модулю два преобразуется в двоичный код на выходах 51 - 54. 1 ил., 1 табл.

ел

СП

СО 4Ь

00

315

Изобретение относится к автоматике и вычислительной технике и может быть использовано в гибких вычислительных машинах и АСУ для перевода натуральных чисел, представленных в минимальной форме t,-системы счисления в двоичную систему.

Цель изобретения - расширение области применения за счет преобразова- ния чисел из минимальной формы tt-системы счисления в двоичную систему счисления.

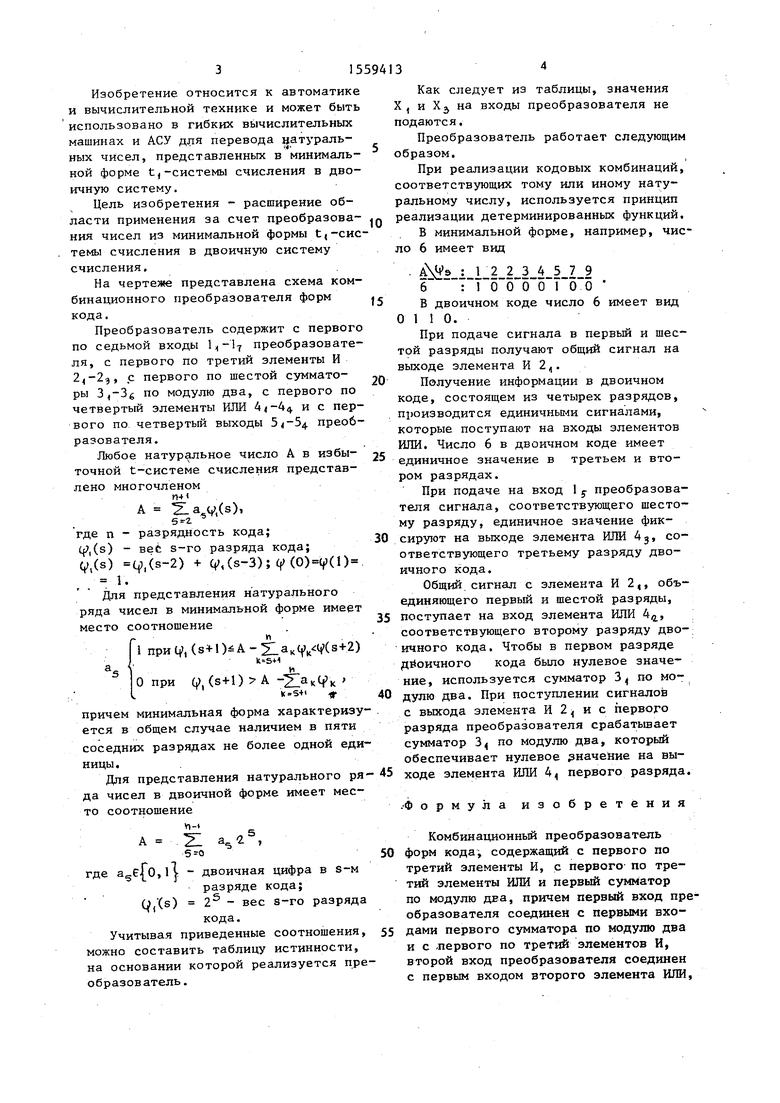

На чертеже представлена схема комбинационного преобразователя форм кода.

Преобразователь содержит с первого по седьмой входы преобразователя, с первого по третий элементы И 2t-2-)t с первого по шестой суммато- ры 3,-3 по модулю два, с первого по четвертый элементы ИЛИ и с первого по четвертый выходы преобразователя.

Любое натуральное число А в избы- точной t-системе счисления представлено многочленом

и-н А Ха u(s),

ъ где п - разрядность кода;

C,(s) - set s-ro разряда кода;

V,(s) -q,(s-2) + q;,(s-3); f(0)v(l)

i.

Для представления натурального ряда чисел в минимальной форме имеет

место соотношение

п I приЦ,(з+1)ЈА-21акик(з+2)

К«5И 5 1

О при у, (s+1) А .

причем минимальная форма характеризуется в общем случае наличием в пяти соседних разрядах не более одной единицы.

Для представления натурального ря- да чисел в двоичной форме имеет место соотношение

Vl-t

А

,

где a5eЈo,ll- - двоичная цифра в S-M

разряде кода; Q,(s) 25 - вес s-ro разряда

кода.

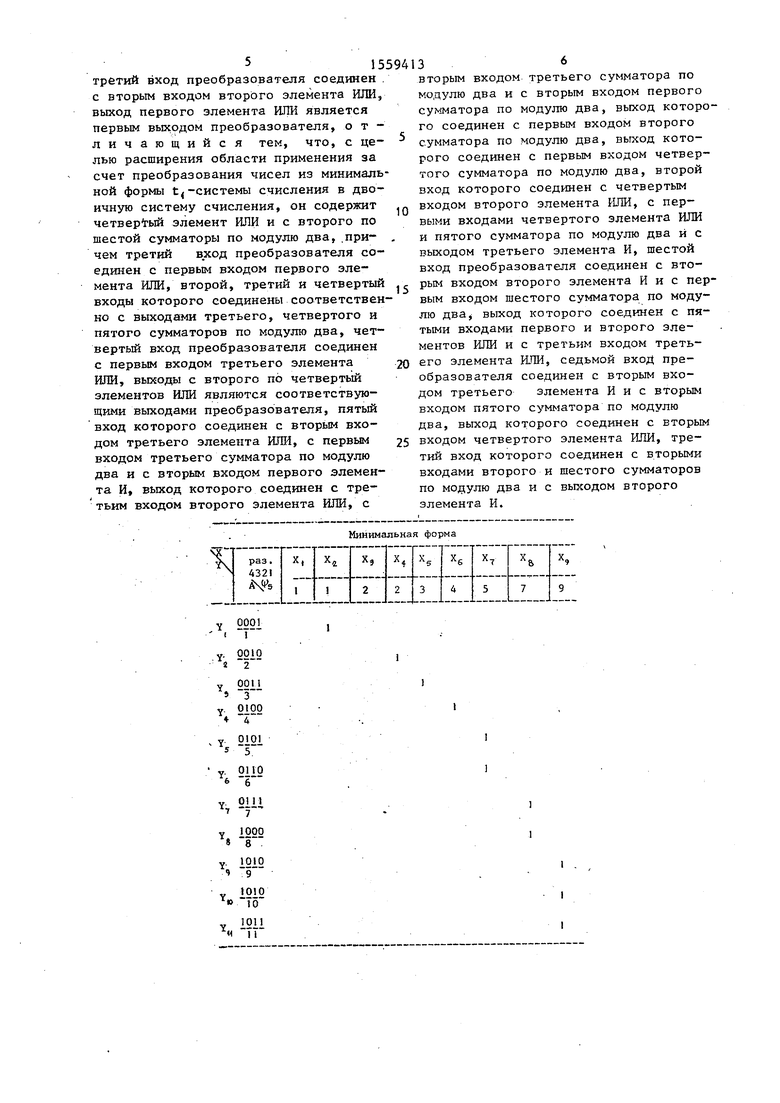

Учитывая приведенные соотношения, 55 можно составить таблицу истинности, на основании которой реализуется преобразователь.

94

Q

5

40

45

0

35

50

55

134

Как следует из таблицы, значения X, и Х3 на входы преобразователя не подаются,

Преобразователь работает следующим образом.

При реализации кодовых комбинаций, соответствующих тому или иному натуральному числу, используется принцип реализации детерминированных функций.

В минимальной форме, например, число 6 имеет вид

: 1 2234579

6

В двоичном коде число 6 имеет вид 0110.

При подаче сигнала в первый и шестой разряды получают общий сигнал на выходе элемента И 2,.

Получение информации в двоичном коде, состоящем из четырех разрядов, производится единичными сигналами, которые поступают на входы элементов ИЛИ. Число 6 в двоичном коде имеет единичное значение в третьем и втором разрядах.

При подаче на вход 1 у преобразователя сигнала, соответствующего шестому разряду, единичное значение фиксируют на выходе элемента ИЛИ 43, соответствующего третьему разряду двоичного кода.

Общий сигнал с элемента И 2,, объединяющего первый и шестой разряды, поступает на вход элемента ИЛИ 44, соответствующего второму разряду двоичного кода. Чтобы в первом разряде дйоичного кода было нулевое значение, используется сумматор 3 по модулю два. При поступлении сигналов с выхода элемента И 2 и с первого разряда преобразователя срабатывает сумматор 3 по модулю два, который обеспечивает нулевое значение на выходе элемента ИЛИ 44 первого разряда.

-Формула изобретения

Комбинационный преобразователь форм кода, содержащий с первого по третий элементы И, с первого по третий элементы ИЛИ и первый сумматор по модулю дна, причем первый вход преобразователя соединен с первыми входами первого сумматора по модулю два и с -первого по третий элементов И, второй вход преобразователя соединен с первым входом второго элемента ИЛИ,

515

третий вход преобразователя соединен с вторым входом второго элемента ИЛИ, выход первого элемента ИЛИ является первым выходом преобразователя, отличающийся тем, что, с це- лью расширения области применения за счет преобразования чисел из минимальной формы tj-системы счисления в двоичную систему счисления, он содержит четвертый элемент ИЛИ и с второго по шестой сумматоры по модулю два,.при- чем третий вход преобразователя соединен с первым входом первого элемента ИЛИ, второй, третий и четвертый входы которого соединены соответственно с выходами третьего, четвертого и пятого сумматоров по модулю два, четвертый вход преобразователя соединен с первым входом третьего элемента ИЛИ, выходы с второго по четвертый элементов ИЛИ являются соответствующими выходами преобразователя, пятый вход которого соединен с вторым входом третьего элемента ИЛИ, с первым входом третьего сумматора по модулю два и с вторым входом первого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, с

Y0001

Y.0010

vООН

Y0100

4Т

Y010

5-5™

YОНО

,5Р

Y1000

8-g-

Y1010

5Т

v1010

v1011

94

- . 0 15

0

5

136

вторым входом третьего сумматора по модулю два и с вторым входом первого сумматора по модулю два, выход которого соединен с первым входом второго сумматора по модулю два, выход которого соединен с первым входом четвертого сумматора по модулю два, второй вход которого соединен с четвертым входом второго элемента ИЛИ, с первыми входами четвертого элемента ИЛИ и пятого сумматора по модулю два и с выходом третьего элемента И, шестой вход преобразователя соединен с вторым входом второго элемента И и с первым входом шестого сумматора по модулю два, выход которого соединен с пятыми входами первого и второго элементов ИЛИ и с третьим входом третьего элемента ИЛИ, седьмой вход преобразователя соединен с вторым входом третьего элемента И и с вторым входом пятого сумматора по модулю два, выход которого соединен с вторым входом четвертого элемента ИЛИ, третий вход которого соединен с вторыми входами второго и шестого сумматоров по модулю два и с выходом второго элемента И.

Минимальная форма

Авторы

Даты

1990-04-23—Публикация

1988-06-01—Подача