Изобретение относится к вычислительной технике и может использоваться в системах обработки цифровой информации .

Целью изобретения является расширение области применения за счет увеличения разрядности устройства.

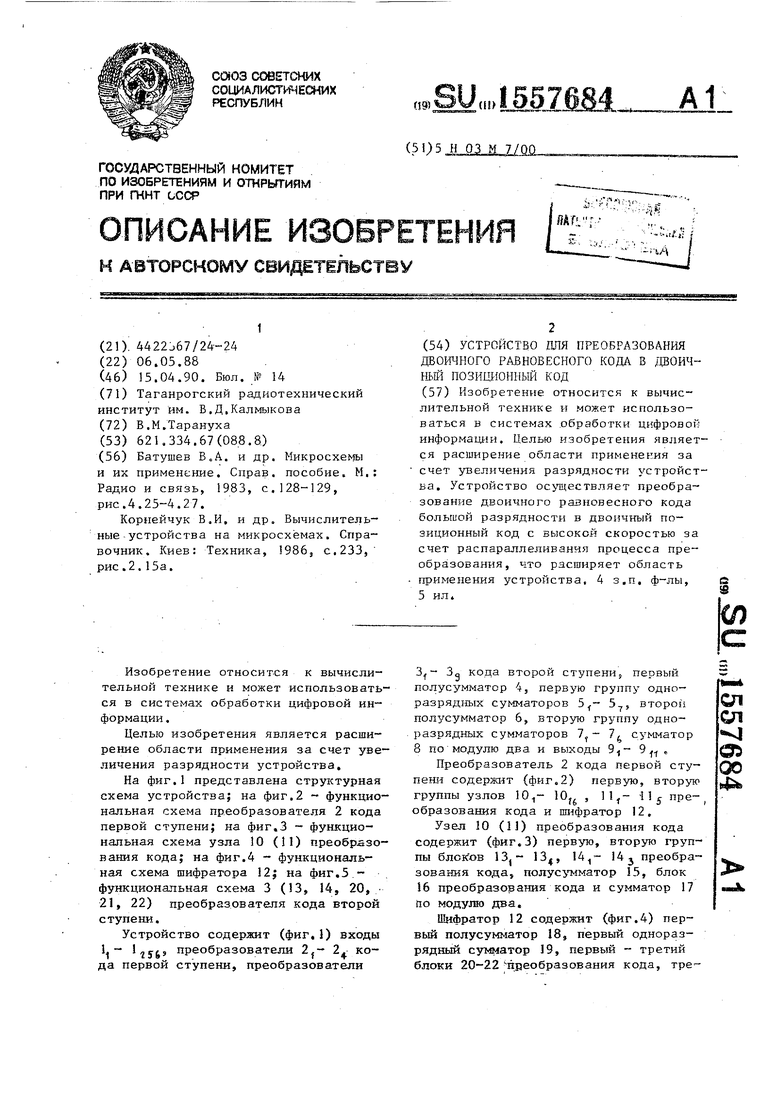

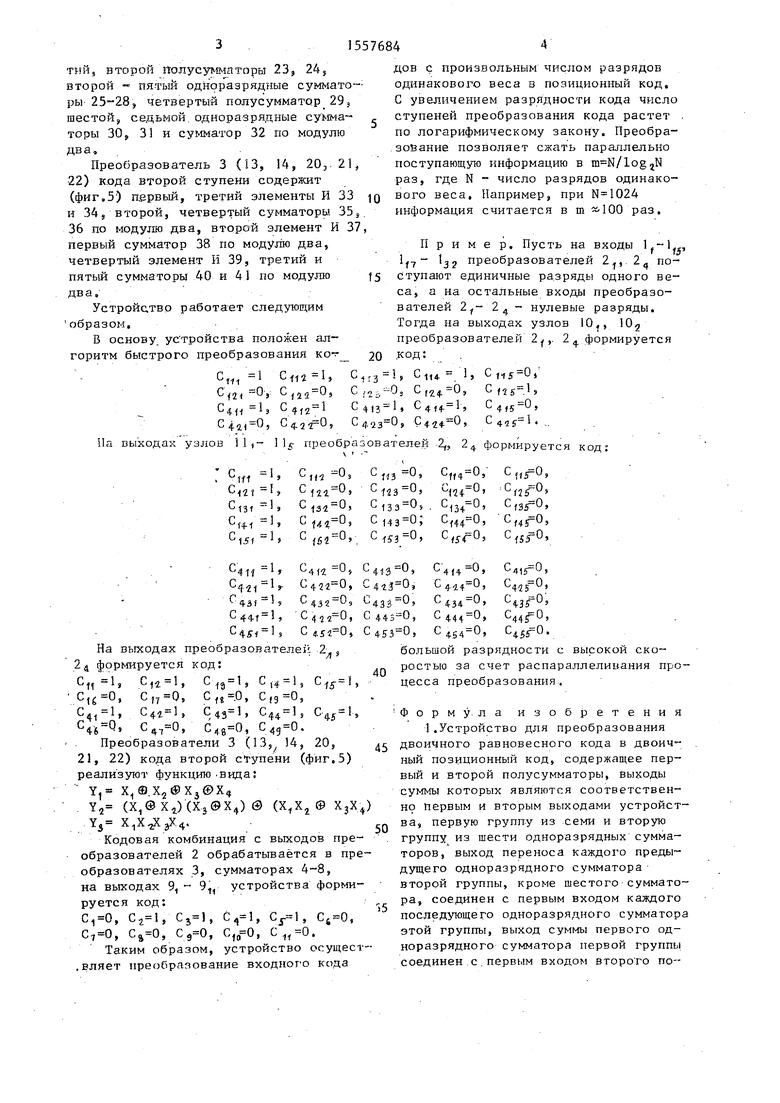

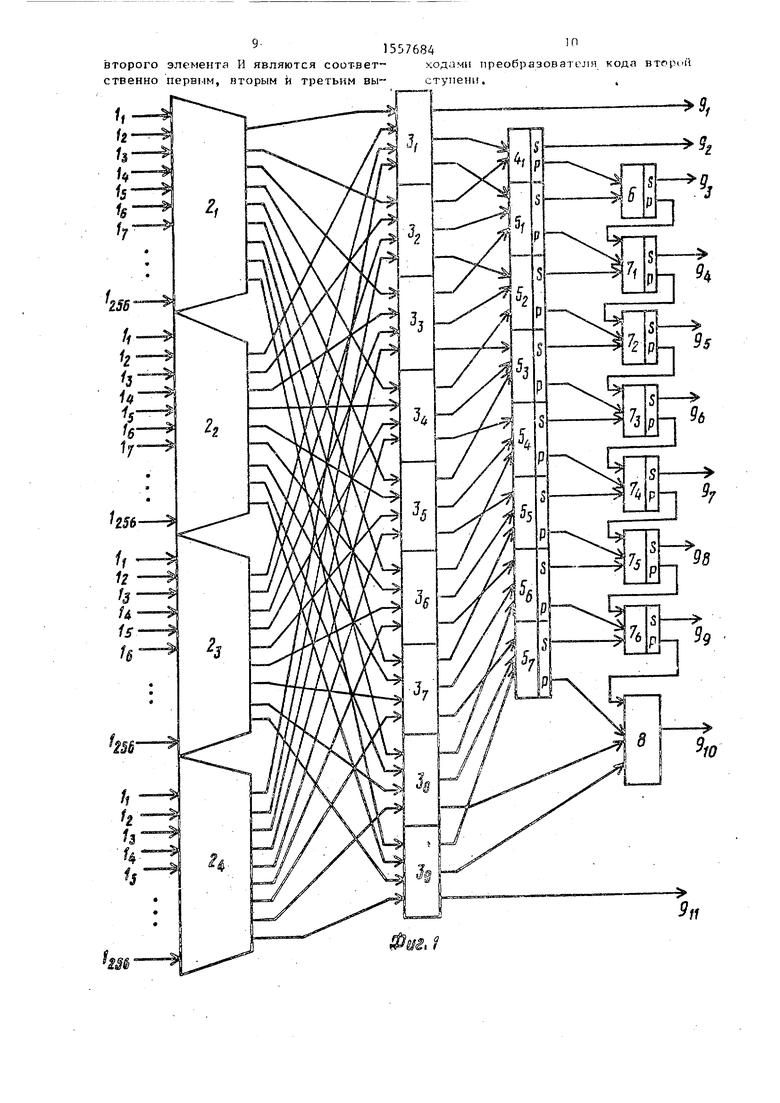

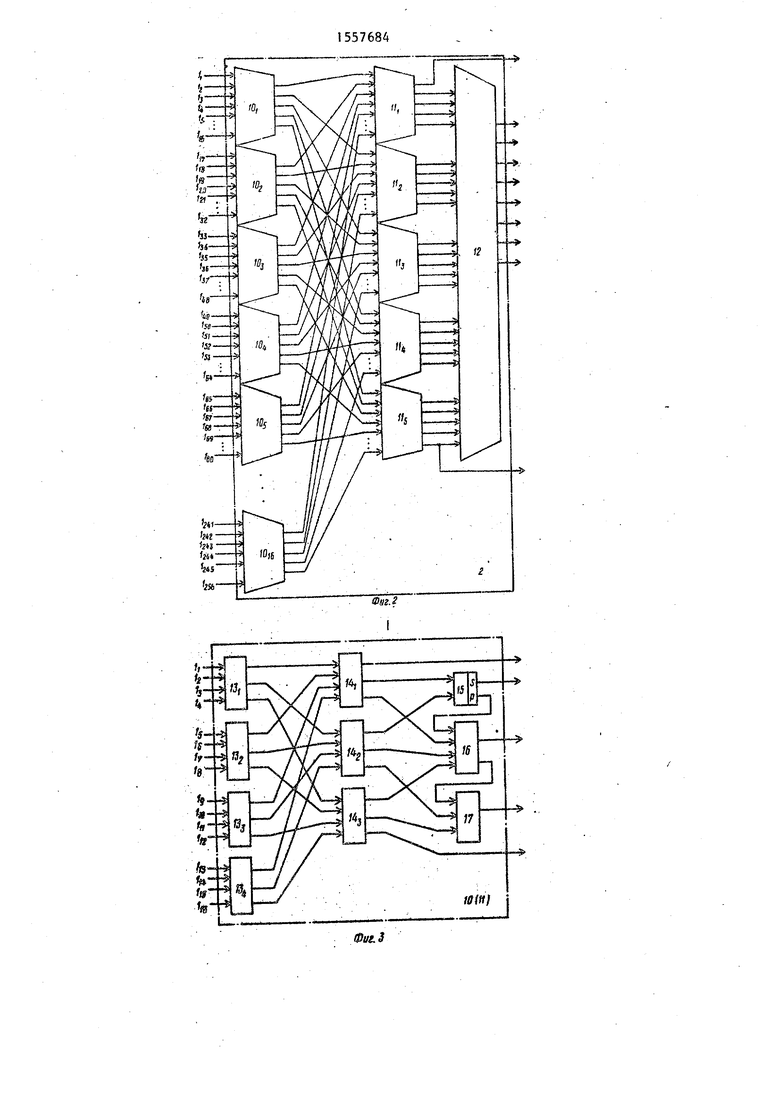

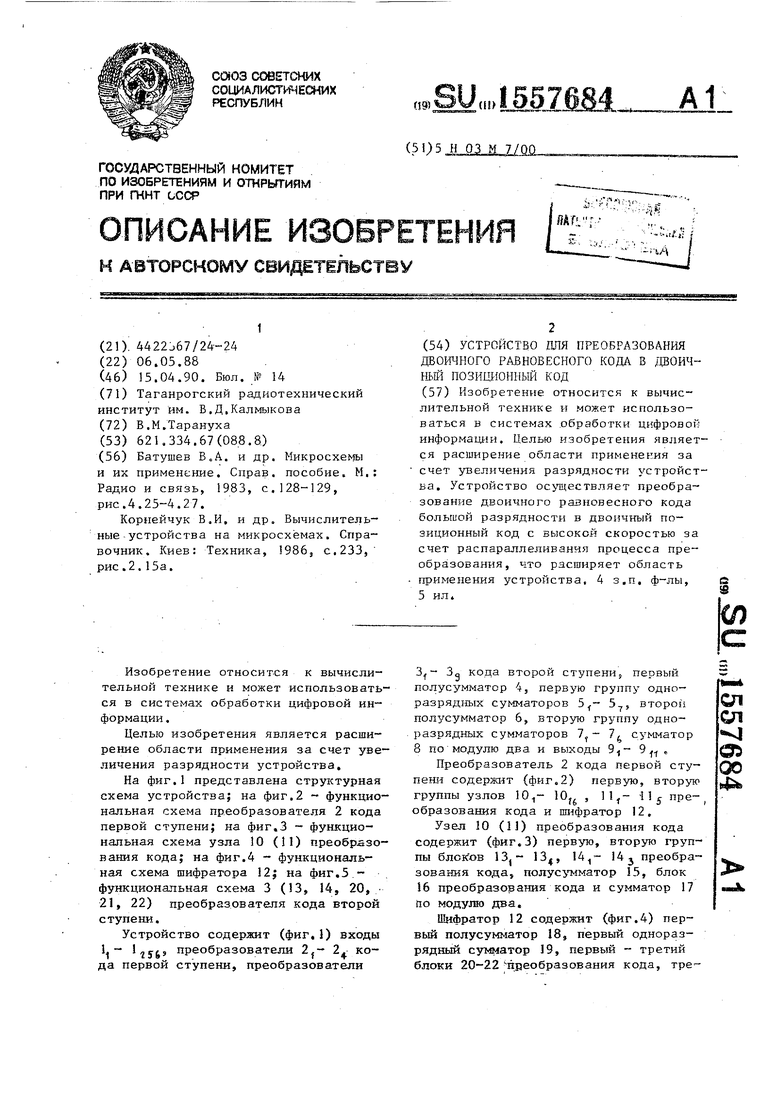

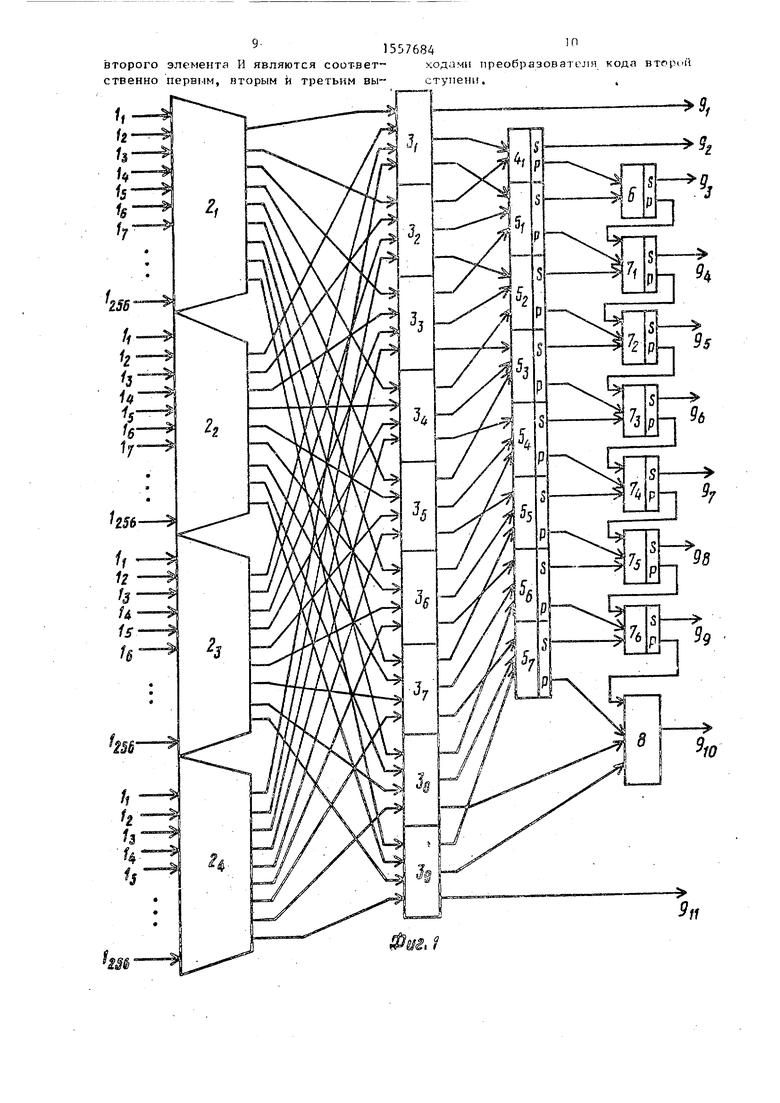

На фиг.1 представлена структурная схема устройства; на фиг.2 - функциональная схема преобразователя 2 кода первой ступени; на фиг.З - функциональная схема узла 10 (11) преобразования кода; на фиг.4 - функциональная схема шифратора 12} на фиг.З - функциональная схема 3 (13, 14, 20, 21, 22) преобразователя кода второй ступени.

Устройство содержит (фиг.1) входы 1 - преобразователи 2{- 2 кода первой ступени, преобразователи

3f - 3g кода второй ступени,

пеовыи

полусумматор ч, первую группу одноразрядных сумматоров 5f 57$ второй полусумматор 6, вторую группу одноразрядных сумматоров 7Т- 7 сумматор 8 по модулю два и выходы 91- 9 .

Преобразователь 2 кода первой ступени содержит (фиг.2) первую, вторую группы узлов 10,- 10, , llf- 115 пре- ( образования кода и шифратор 12.

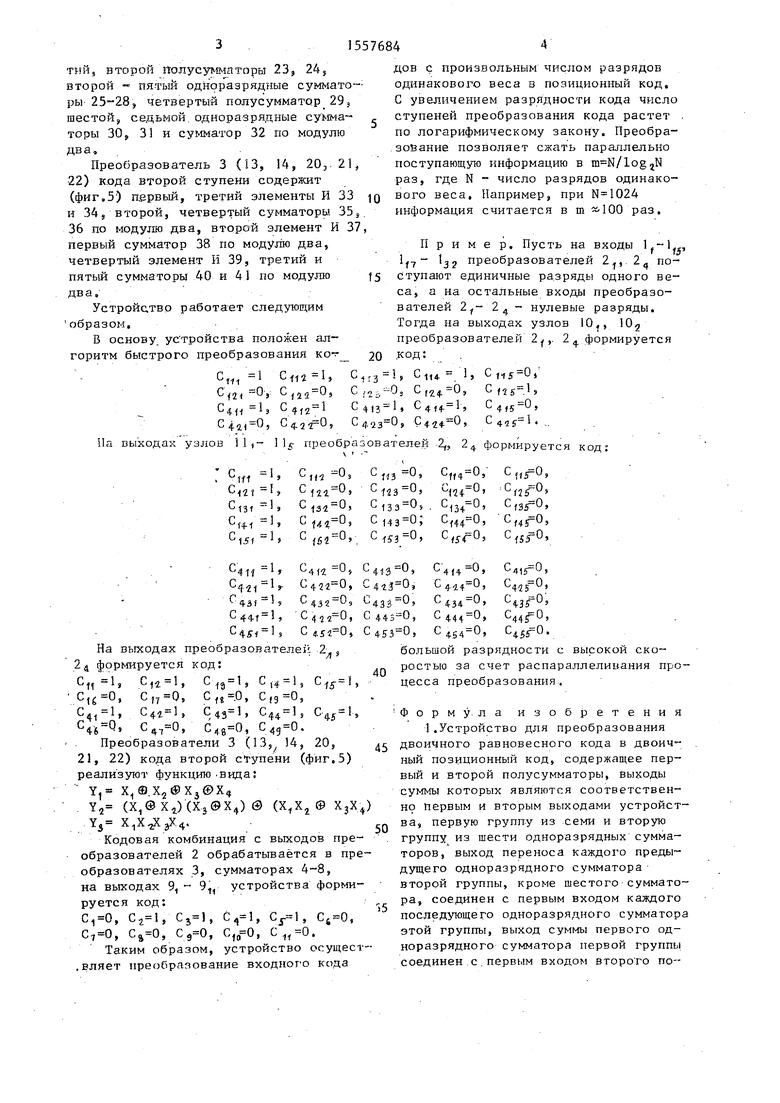

Узел 10 (11) преобразования кода содержит (фиг.З) первую, вторую группы блоков 13,- 134, 14,- 14 з преобразования кода, полусумматор 15, блок S6 преобразования кода и сумматор 17 по модулю два.

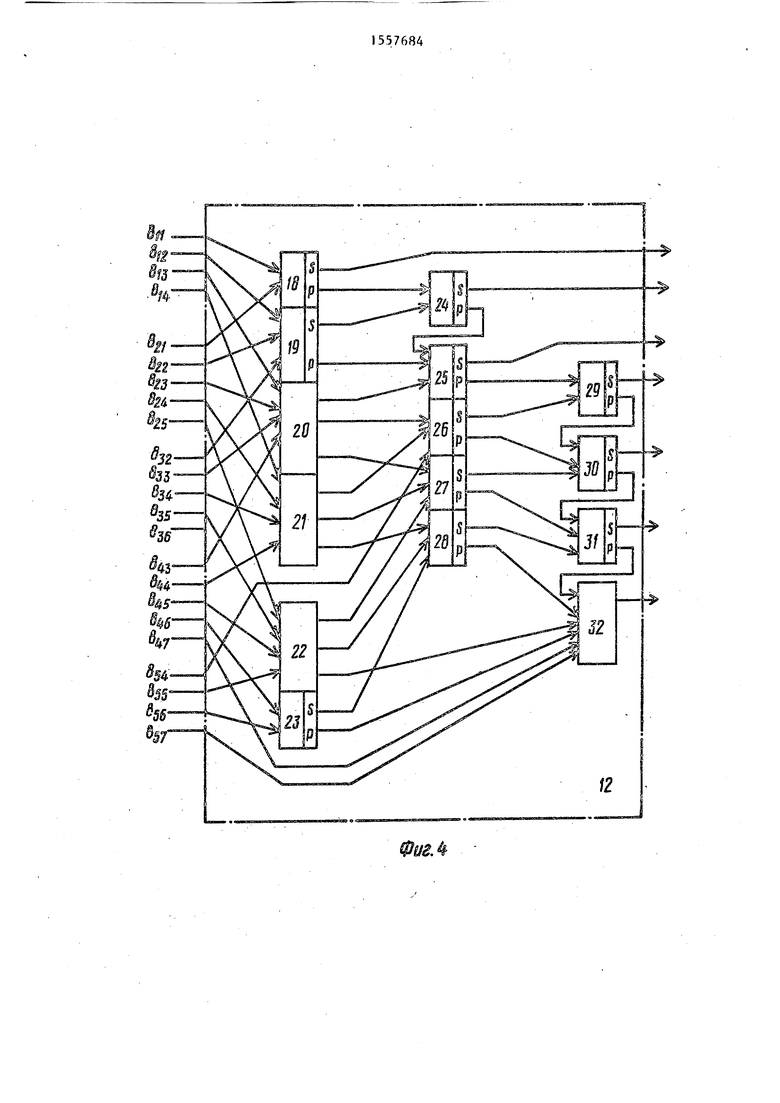

Шифратор 12 содержит (фиг.4) первый полусумматор 18, первый одноразрядный сумматор 19, первый - третий блоки 20-22 -преобразования кода, тре01

ел

О)

оо

тий, второй полусумматоры 23, 24 5 второй - пятый одноразрядные сумматоры 25-28, четвертый полусумматор 29 шестой, седьмой одноразрядные сумматоры 30, 31 и сумматор 32 по модулю два.

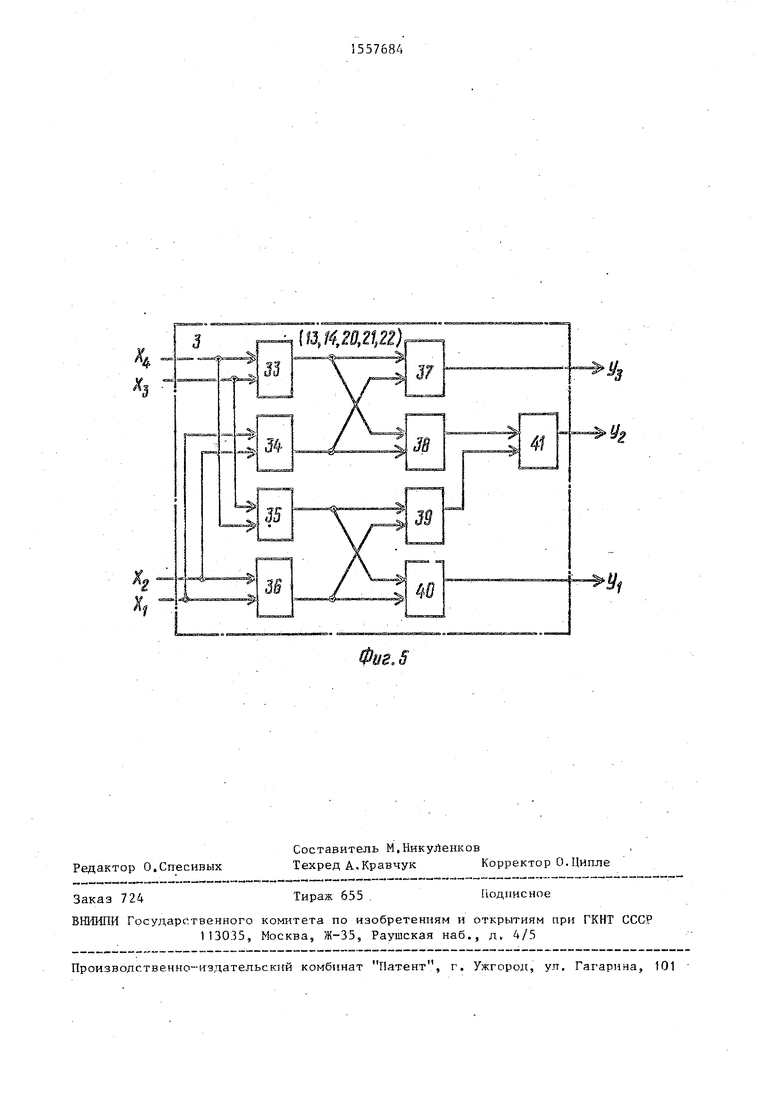

Преобразователь 3 (13, 14, 20э 21, 22) кода второй ступени содержит (фиг,5) первый, третий элементы И 33 и 34 s второй, четвертый сумматоры 35} 36 по модулю два, второй элемент И 37 первый сумматор 38 по модулю два, четвертый элемент И 39, третий и пятый сумматоры 40 и 41 по модулю два.

Устройство работает следующим 1 образом,

В основу устройства положен алгоритм быстрого преобразования ко-

lС-И2 I}

0,

1,С

0,,

г п

f11 U5

М2

дов с произвольным числом разрядов одинакового веса в позиционный код, С увеличением разрядности кода число ступеней преобразования кода растет по логарифмическому закону. Преобразование позволяет сжать параллельно поступающую информацию в m N/logjN раз, где N - число разрядов одинакового веса. Например, при информация считается в m 100 раз.

П

р и м е р. Пусть на входы , 132 преобразователей 2f, 2,, поступают единичные разряды одного веса, а на остальные входы преобразо f7

2

нулевые разряды.

0

3 1,

вателей 2f

Тогда на выходах узлов 10,, 102

преобразователей 2f, 2 формируется

код:

0,

„-о5

fJ - 1

11

С Г2.4 5 С С+2+.0,

И 5 М5 45

1,

0,

1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1292187A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1982 |

|

SU1097995A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691844A1 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

| Устройство для преобразования двоичного кода в код системы счисления с отрицательным основанием /его варианты/ | 1982 |

|

SU1097994A1 |

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771659A1 |

Изобретение относится к вычислительной технике и может использоваться в системах обработки цифровой информации. Целью изобретения является расширение области применения за счет увеличения разрядности устройства. Устройство осуществляет преобразование двоичного равновесного кода большой разрядности в двоичный позиционный код с высокой скоростью за счет распараллеливания процесса преобразования, что расширяет область применения устройства. 4 з.п. ф-лы, 5 ил.

На

выходах узлов 11,- 11 преобразователей 2,, 24 формируется код:

, C,

44-1 43-, C44-ls , , , .

C1S-0, C,7 С

C«.

Преобразователи 3 (13S/ 14, 20,

21, 22) кода второй ступени (фиг,5) реализуют функцию вида; Y, X,,® Х2й Х3©Х4

Y2 (Х1©Х1)(Х3©Х4) & (XfXt@ X3X4) Y3 Х1ХгК3Х4.

Кодовая комбинация с выходов преобразователей 2 обрабатывается в преобразователях 3, сумматорах 4-8, на выходах 9, - 9 устройства формируется код: С,0, , , С,1, , С4«0, , , , , .

Таким образом, устройство огущест-- .вляет преобразование входного кода

5

Q

с

Формула изобретения

I.Устройство для преобразования двоичного равновесного кода в двоичный позиционный код, содержащее первый и второй полусумматоры, выходы суммы которых являются соответственно первым и вторым выходами устройства, первую группу из семи и вторую группу из шести одноразрядных сумматоров, выход переноса каждого предыдущего одноразрядного сумматора второй группы, кроме шестого сумматора, соединен с первым входом каждого последующего одноразрядного сумматора этой группы, выход суммы первого одноразрядного сумматора первой группы соединен с первым входом второго по-515

лусумматора, выход переноса которого соединен с первым входом первого одно разрядного сумматора второй группы, выходы суммы второго - шестого одноразрядных сумматоров первой группы соединены с вторыми входами соответственно первого - пятого одноразрядных сумматоров второй группы, выходы суммы пятого и шестого одноразрядных сумматоров второй группы являются соответственно третьим и четвертым выходами устройства, о тлич а-ю - щ е е с я тем, что, с целью расширения области применения за счет увеличения разрядности устройства, в него введены сумматор по модулю два, преобразователи кода первой ступени, преобразователи кода второй ступени, вчоцы преобразователей кода первой ступени являются входами устройства, первые - девятые выходы первого - четвертого преобразователей кода соединены с соответствующими первыми - четвертыми входами рдно- именных первого - девятого преобразователей кода второй ступени, первые выходы первого - седьмого преобразователей кода второй ступени соединены с первыми входами одноименных одноразрядных сумматоров первой группы, первые выходы восьмого и девятого преобразователей кода второ.й ступени соединены соответственно с первым и вторым входами сумматора по модулю два, вторые выходы второго- восьмого преобразователей кода второй ступени соединены с вторыми входами соответствующих первого - седьмого одноразрядных сумматоров первой группы, второй выход девятого преобразователя кода второй ступени соединен с третьим входом седьмого одноразрядного сумматора первой группы, выходы переноса и суммы которого соединены соответственно с третьим входом -сумматора по модулю два и вторым входом шестого одноразрядного сумматора, выход переноса которого соединен с четвертым входом сумматора по модулю два, третьи выходы третьего - восьмого преобразователей кода второй ступени соединены с третьими входами соответствующих первого - шестого одноразрядных сумматоров вой группы, выходы переноса которых соединены с третьими входами соответствующих первого - шестого одноразрядных сумматоров второй группы, второй

76846

выход первого блока преобразовсгння кода и третий выход второго преобразователя кода второй ступени соединены соответственно с первым и вторым входами первого полусумматора, выход переноса которого соединен с вторым входом второго полусумматора, третие выходы первого, девятого преобразоваIQ тгля кода второй ступениf выходы суммы первого - четвертого одноразрядных сумматоров второй группы и выход сумметора но модулю два являются соответственно пятьи-, - одиннадцаJ5 тым- выходами устройства.

г входами полусумматора, блока преобразования кода и первым входом сумматора по модулю два, третьи выходы соответственно соединены с третьим входом блока преобразования кода, вторым

35

входом сумматора по модулю два и являются пятым выходом узла преобразовали кода, выход переноса полусумматора соединен с четвертым входом блока преобразования кода, входы блоков преобразования кодй первой группы являются входами узла преобразования кода, выход суммы полусумматора, первый выход блока преобразо- вания кода и ьыход сумматора по модулю два являются соответственно вто-. i рым - четвертым выходами узла преобразования коца, второй выход блока преобразования кода соединен с

третьим входом сумматора по модулю два.

одноразрядных сумматоров соединены с вторыми входами соответственно четвертого полусумматора, шестого и седьмого одноразрядных сумматоров, выход переноса четвертого полусумматора соединен с третьим входом шестого одноразрядного сумматора, выход переноса которого соединен с третьим входом седьмого одноразрядного сумматора, выход переноса которого соединен с четвертым входом сумматора по модулю два, первые и вторые входы первого и третьего полусумматоров, первые, вторые и третьи входы первого9 второго и третьего блоков преобразования кода, третий вход третьего одноразрядного сумматора, пятый и шестой входы сумматора по модулю два являются входами шифратора, выходы суммы первого, второго и третьего полусумматоров, второго, шестого и седьмого одноразрядных сумматоров и сумматора по модулю два являются выходами шифратора.

5«Устройство по пп.1, 3 и 4, отличающееся тем, что преобразователь кода второй ступени содержит элементы И и сумматоры по модулю два, выход первого элемента И соединен с первыми входами второго элемента И и первого сумматора по модулю два, выход третьего элемента И соединен с вторыми входами второго элемента И и первого сумматора по модулю два, выход второго сумматора по модулю два соединен с первыми входами четвертого элемента И и третьего сумматора по модулю два, выход четвертого сумматора по модулю два соединен с вторыми входами третьего сумматора по модулю два и четвертого элемента И, выход которого и выход первого сумматора по модулю два соединены соответственно с первым и вторым входами пятого сумматора по модулю два, одноименные первые и вторые входы четвертого сумматора по модулю два и третьего элемента И объединены соответственно и являются соответственно первым и вторым входами преобразователя кода второй ступени, одноименные первые и вторые входы первого элемента И и второго сумматора по модулю два объединены соответственно и являются соответственно третьим и четвертым входами преобарзователя кода второй ступени, выходы третьего и пятого сумматоров по модулю два и

9 п

гГФга

g ЗГffSTs--r г s- ffg-r r r T Г «г Г ТТ4 4 j/4 J/ 4 Ф w tr4f Jf 4/. y if 4/ 4; 4/ w уу.уфф У. Ф. 4 4 w 4/

Редактор О.Спесивых

Составитель М.Никуленков

Техред А.КравчукКорректор О.Ципле

Заказ 724

Тираж 655

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, утт. Гагарина, 101

Подписное

| Батушев В.А | |||

| и др | |||

| Микросхемы и их применение | |||

| Справ, пособие | |||

| М.: Радио и связь, 1983, с | |||

| Сепаратор-центрофуга с периодическим выпуском продуктов | 1922 |

|

SU128A1 |

| Корнейчук В.И, и др | |||

| Вычислительные устройства на микросхемах | |||

| Справочник | |||

| Киев: Техника, 1986, с.233, рис.2.15а. | |||

Авторы

Даты

1990-04-15—Публикация

1988-05-06—Подача