ления), две группы элементов И 2/- 2 и j, две группы элементов ИЛИ 4| и 5, два дополнительных бистабильных элемента 6,7, десять элементов И 8 - 17, четыре элемента ИЛИ 18-21, два элемента И-НЕ 22,23, шесть элементов НЕ 24- 29, четыре элемента НЕ с увеличенной задержкой 30-33 и два элемента

1

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах.

Цель изобретения - повышение точ- ности сложения и вычитания длительностей импульсов.

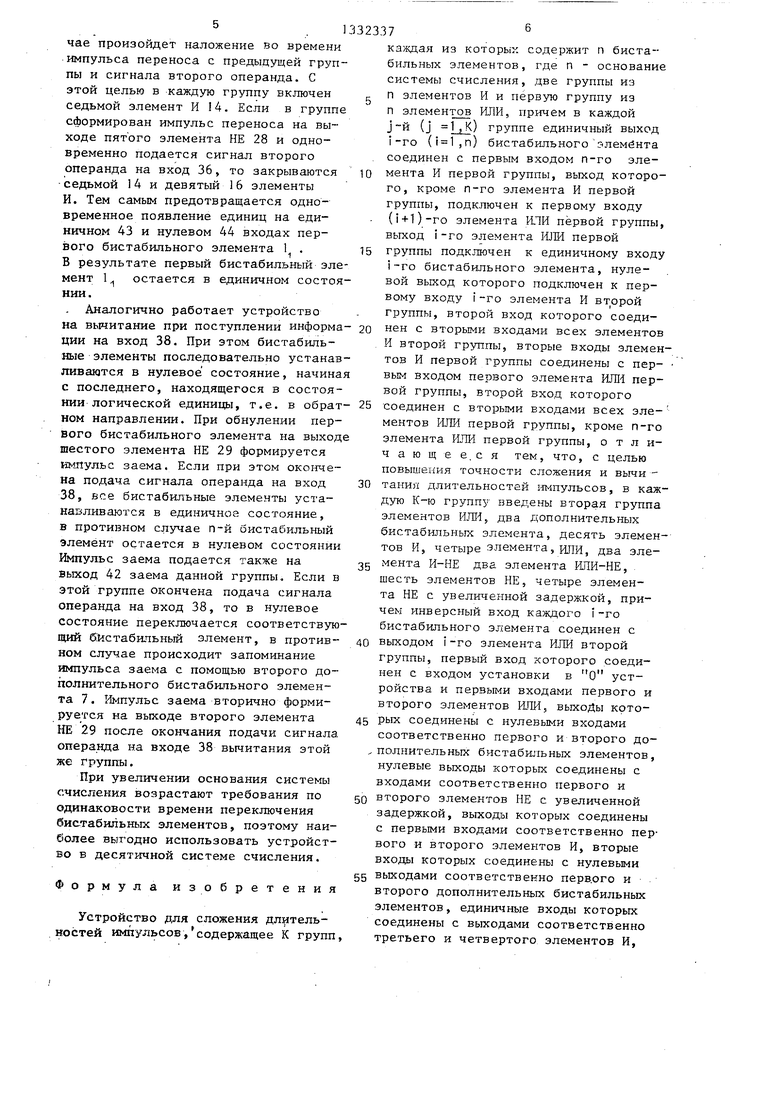

На чертеже представлена схема одной группы устройства для сложения длительностей импульсов.

Каждая группа устройства содержит бистабильные элементы 1(1,..., 1ц), две группы элементов И 2 (2 ,.,.,2) и 3 (3,...,3j, две группы элементов ИЛИ 4 (4,...,4|) и 5 (5 ,. . . ,5 f,) , дополнительные бистабильные элементы 6 и 7, элемен- -ты ИВ - 17, элементы ИЛИ 18 - 21, элементы И-НЕ °22 и 23, элементы НЕ 24-29, элементы НЕ 30 - 33 с увеличенной задержкой и элементы ИЛИ-НЕ 34 и 35, Кроме того, обозначены вход 36 операндов при вьшолне- нии сложения, вход 37 установки в , ноль устройства, вход 38 операндов при выполнении вычитания, вход 39 переноса из предьщущей группы устройства, вход 40 заема из предыдущей группы устройства, выход 41 переноса в следующую группу устройства, выход 42 42 заема в следующую группу устройства, единичный 43 и нулевой 44 входы бистабильных элементов, выходы 45 и 46 бистабильных элементов.

Рассмотрим алгоритм сложения двух длительностей импульсов. С этой целью целью предварительно введем следующие обозначения:

А.,,,.а„а, - первое

k k-1 г

слагаемое;

1332337

ИЛИ-НЕ 34,35. В каждом разряде имеются входные шины сложения 36 и вычитания 38. Сложение длительностей импульсов осуществляется последовательным переключением бистабильных элементов в единичное состояние, а вычитание - переключением бистабильных элементов в нулевое состояние . I ил.

0

5

25 OQ

40

k 1с-1 г 1 второе

слагаемое;

{( У слагаемых А и В;

Р,- - перенос из i-го в ( + 1)-й разряд.

Сложение происходит согласно следующему алгоритму.

В начале на входы сумматора подается первый операнд А. Если считать, что сумматор предварительно обнулен, то после окончания подачи операнда А в каждой группе (разряде) получают сумм,у el. а + 0. Лосколь- ку а п (п - основание системы счисления), поэтому с.п мР- 0, т.е. переноса в старший (1+1)-й разряд нет.

этого на входы сумматора подается второй операнд В, При этом возможны два случая:

с(. а. + Ь. : п, Р; 0;

а + Ь, л, Р 1 .

При первом случае переноса в старший разряд не происходит, поэтому отдельные разряды (группы ) сумматора функционируют самостоятельно.

Когда с(( 7/ п и PJ 1 , имеют два подслучая: .

Ь,-м Ь. ;

Ь i b i .

При первом подслучае импульс переноса Р из разряда i непосредственно подается на вход переноса (1+1)-го разряда и прибавляется к сумме Ь;.

При втором подслучае импульс переноса Р- из разярда i подается на вход переноса (i+1)-ro разряда в то время, когда еще не окончена на входе суммирования подача

разряда b

) + (

второго операнда. При

этом происходит наложение сигнала операнда Ь. и переноса Р; , что вызывает потери последнего. Чтобы исключить это, необходимо запомнить переносы Р,- на промежуточных элементах памяти и выдать на вход переноса (i+l)-ro разряда после окончания сигнала Ь,- .

Устройство работает следующим |Образом.

Устройство оперирует как аналоговыми (заданных длительностью импульсов) , так и цифровыми сигналами (заданных количеством импульсов).

Рассмотрим функционирование устройства с аналоговыми сигналами. До начала процесса суммирования высокий потенциал подается на вход 37 установки в ноль и, пройдя через злемен10

Таким образом, при поступлении первого операнда А количество переключенных бистабильных элементов всегда меньше п (п - основание системы счисления ).

С подачей второго операнда В продолжается переключение бистабильных элементов 1. Последний бистабильный

элемент I,

при установке в состояние логической 1 дает разрешение 15 на формирование импульса переноса. Импульс переноса формируется с помощью третьего элемента НЕ 32 с увеличенной задержкой, первого элемента И-НЕ 22 и пятого элемента 20 НЕ 28. При появлении единицы на выходе последнего элемента И 2 первой группы на выходе первого элемента И-НЕ 22 устанавливается низкий потенциал, а на выходе пятого элеменвторой группы и первый 25 та НЕ 28 - высокий потенциал, который подается на вторые входы всех элементов 5,,- 5, кроме первого 5 , второй группы. Продолжительность импульса определяется временем за30 держки третьего элемента НЕ 32 с

увеличенной задержкой. Импульс с выхода пятого элемента НЕ 28 обнуляет все бистабильные элементы, кроме первого. Первьш бистабильный элемент

35 1 обнуляется в том случае, если при этом на вход 46 суммирования данной группы подача сигнала второго операнда окончена. Импульс переноса подается также на выход 41 переноса ..

40 данной группы. При этом,если подача сигнала второго операнда на вход 36 следующей группы окончена импульс переноса через пятый элемент И 12 и третий элемент ИЛИ 20 перебрасьгоает

45 один из бистабильных элементов 1 следующей группы в единичное состояние, в противном случае через третий элемент И 10 перебрасывает первый дополнительный бистабильный элемент

50 6 в единичное состояние, где происходит его запоминание. После окончания сигнала второго операнда следующей группы на выходе первого элемента И 8 снова формируется этот им55 пульс переноса, который переключает соответствующий бистабильный элемент 1 этой группы;

Запоминание импульса переноса необходимо, поскольку в противном слуты или 5|

18 и второй 19 элементы ИЛИ, все бистабильные элементы 1 и дополнительные бистабильные элементы 6 и 7 всех групп переводит в нулевое состояние.

При поступлении информации (единичного сигнала) на вход 36 низкий сигнал с выхода первого элемента ИЛИ-НЕ 34 поступает на первый вход седьмого элемента И 14 и закрывает его. Одновременно этот сигнал, пройдя третий элемент НЕ 26, открьшает девятый элемент И 16 (при этом на второй вход девятого элемента И 16 с выхода первого элемента И-НЕ 22 подается высокий потенциал). Высокий потенциал с выхода девятого элемента И 16 через первый элемент ИЛИ 4 первой группы переключает первый бистабильный элемент 1 в единичное состояние, и на выходе 45 этого элемента появляется высокий потенциал. Высокий потенциал с выхода 45 первого бистабильного элемента 1 через первый элемент И 2 (который в это время в открытом состоянии) первой группы и через второй элемент ИЛИ 4„ первой группы подается на единичный вход 43 второго бистабильного элемента h , переключая его в единичное состояние и т.д. Переход в единичное состояние бистабильных элементов 1 заканчивается после прекращения входного сигнала. Ко

личество переключенных бистабильных элементов в группе соответствует длительности входного сигнала.

Таким образом, при поступлении первого операнда А количество переключенных бистабильных элементов всегда меньше п (п - основание системы счисления ).

С подачей второго операнда В продолжается переключение бистабильных элементов 1. Последний бистабильный

элемент I,

при установке в состояние логической 1 дает разрешение на формирование импульса переноса. Импульс переноса формируется с помощью третьего элемента НЕ 32 с увеличенной задержкой, первого элемента И-НЕ 22 и пятого элемента НЕ 28. При появлении единицы на выходе последнего элемента И 2 первой группы на выходе первого элемента И-НЕ 22 устанавливается низкий потенциал, а на выходе пятого элеменкаждая из которых содержит п биста- бильных элементов, где п - основание системы счисления, две группы из

,- п элементов И и первую группу из о

П элементов ИЛИ, причем в каждой

j й (j ) группе единичный выход i-го (i 1,n) бистабильного элемента , соединен с первым входом п-го эле- 10 мента И первой группы, выход которого, кроме п-го элемента И первой группы, подключен к первому входу (i+l)-ro элемента ИЛИ первой группы, выход i -го элемента ШЖ первой 15 группы подключен к единичному входу i-го бистабильного элемента, нулевой выход которого подключен к первому входу i-го элемента И второй группы, второй вход которого соеди- на вьнитание при поступлении информа- 20 нен с вторыми входами всех элементов ции на вход 38. При этом бистабиль- . И второй группы, вторые входы злемен- Ные элементы последовательно устанав- тов И первой группы соединены с пер- ливаются в нулевое состояние, начиная вым входом первого элемента MJlIi пер- с последнего, находящегося в состоя- вой группы, второй вход которого НИИ логической единицы, т.е. в обрат- 25 соединен с вторыми входами всех эле- ном направлении. При обнулении пер- ментов ИЛИ первой группы, кроме п-го

чае произойдет наложение во времени импульса переноса с предыдущей группы и сигнала второго операнда. С этой целью в каждую группу включен седьмой элемент И 14. Если в группе сформирован импульс переноса на выходе пятого элемента НЕ 28 и одновременно подается сигнал второго операнда на вход 36, то закрываются седьмой 14 и девятый 16 элементы И. Тем самым предотвращается одновременное появление единиц на единичном 43 и нулевом 44 входах первого бистабильного элемента 1 . В результате первый бистабильный элемент 1 остается в единичном состоянии .

Аналогично работает устройство

Вого бистабильного элемента на выход шестого элемента НЕ 29 формируется кмпульс заема. Если при этом окончена подача сигнала операнда на вход 38, все бистабилъные элементы уста- наззливаются в единичное состояние, в противном случае п-й бистабильный элемент остается в нулевом состоянии Импульс заема подается также на Выход 42 заема данной группы. Если в этой группе окончена подача сигнала операнда на вход 38, то в нулевое состояние переключается соответствующий бйстабильньш элемент, в противном случае происходит запоминание импульса заема с помощью второго дополнительного бистабильного элемента 7. Импульс заема вторично формируется на выходе второго элемента НЕ 29 после окончания подачи сигнала операнда на входе 38 вьиитания этой же группы.

При увеличении основания системы счисления возрастают требования по одинаковости времени переключения бистабильных элементов, поэтому наиболее вьггодно использовать устройство в десятичной системе счисления.

Формула изобретения

Устройство для сложения длительностей импульсов, содержащее К групп

элемента ИЛИ первой группы, о т л и- ч а ю щ в е,с я тем, что, с целью повышения точности сложения и вычи -

тания длительностей г мпульсов, в каждую К-ю группу введены вторая группа элементов ИЛИ, два дополнительных бистабильных элемента, десять элементов И, четыре элемента, ИЛИ, два элемента И-НЕ два элемента ИЛИ-НЕ, , шесть элементов НЕ, четыре элемента НЕ с увеличенной задержкой, причем инверсный вход каждого i-го бистабильного элемента соединен с

выходом i-го элемента ИЛИ второй группы, первый вход Гтсоторого соединен с входом установки в О устройства и первыми входами первого и второго элементов ИЛИ, выходы котоРых соединены с нулевыми входами

соответственно первого и второго до- полнительных бистабильных элементов, нулевые выходы которых соединены с входами соответственно первого и

второго элементов НЕ с увеличенной задержкой, выходы которых соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены с нулевыми

выходами соответственно перв.ого и второго дополнительных бистабильных элементов, единичные входы которых соединены с выходами соответственно третьего и четвертого элементов И,

первый вход третьего элемента И соединен с входом операндов при выполнении сложения, первым входом первого элемента ИЛИ-НЕ и входом первого элемента НЕ, выход которого соединен с первым входом пятого элемента И и вторым входом первого элемента ИЛИ, первый вход четвертого элемента И соединен с входом oneрандов при выполнении вычитания, первым входом второго элемента ИЛИ-НЕ и входом второго элемента НЕ, выход которого соединен с первым входом шестого элемента И и вторым входом второго элемента ИЛИ, выходы пятого и шестого элементов И соединены с первыми входами соответственно третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходами соответственно первого и второго элементов И,выходы третьего и четвертого элементов ИЛИ соединены с вторыми входами соответственно первого и второго элементов ИЛИ- НЕ, выход первого элемента ИЛИ- НЕ соединен с первым входом седьмого элемента И, входом третьего элемента НЕ, выход второго элемента ИЛИ-НЕ соединен с первым входом восьмого элемента И и входом четвертого элемента НЕ, выходы третьего и четвертого элементов НЕ соединены с первыми входами соответстрен- но девятого и десятого элементов И, вторые входы которых соединены с выходами соответственно первого и второго элементов И-НЕ, первые входы которых соединены с выходами соответственно третьего и четвертого элементов НЕ с увеличенной задержкой, входы которых соединены с выходами соответственно последнего элеСоставитель М.Есенина Редактор И.Николайчук Техред Л,Сердюкова Корректор С.Шекмар

Заказ 3834/45 . Тираж 672Подписное

ВНИИГТИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

2337,

мента И первой группы и первого элемента И второй группы, выходы кото- . рых соединены с вторыми входами соответственно первого и второго элементов И-НЕ, выходы которых соединены с входами соответственно пятого и шестого элементов НЕ, выход пятого элемента НЕ соединен с вторыми входа- 10 ми всех элементов ИПИ второй группы, кроме первого элемента ИЛИ второй L

группы, с вторым входом седьмого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ

второй группы, выход шестого элемента НЕ соединен с вторыми входами всех элементов ИЛИ первой группы, кроме п-го элемента ШШ первой группы восьмого элемента И, выход которого соединен с вторым входом п-го элемента ИЛИ первой группы, выход девятого элемента И соединен с вторым входом п-го элемента И первой группы, выход десятого элемента И

соединен с вторым входом первого элемента И второй группб и третьим входом п-го элемента ИЛИ второй группы, третий вход каждого i-го элемента ИЛИ второй, группы, кроме

п-го элемента ИЛИ второй группы, соединен с выходом (+1)-го элемента И второй группы, выход пятого элемента НЕ j-й группы соединен с выходом переноса в Ci + l)io группу, вход переноса j-й группы устройства соединен с вторыми входами третьего ипятого элементов Иj-й группы, выход шестого эле- мента НЕ j-й группы соединен с выходом заема (3+1)-й группы, вход заема

й группы устройства, соединен с

вторыми входами четвертого и шестого элементов И j-й группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения длительностей импульсов | 1988 |

|

SU1608702A1 |

| Устройство для сложения длительностей импульсов | 1987 |

|

SU1548796A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для сложения длительностей импульсов | 1980 |

|

SU951330A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Оптоэлектронный счетчик импульсов | 1985 |

|

SU1267606A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

| Устройство для сложения в двоичной и в двоично-десятичной системе счисления | 1985 |

|

SU1273919A1 |

| Устройство для суммирования длительностей импульсов | 1987 |

|

SU1430970A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение точности сложения и вычи- тания длительности импульсов. Устройство позволяет осуществить суммирование и вычитание как аналоговых (длительностей импульсов), так и дифровых (ко личество импульсов) величин. Каждый разряд устройства содержит п бистабильных элементов 1 - 1 f (где п - основание системы счис (Л

Авторы

Даты

1987-08-23—Публикация

1986-04-29—Подача