(5) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ДЛИТЕЛЬНОСТЕЙ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования длительностей импульсов | 1987 |

|

SU1430970A1 |

| Устройство для сложения длительностей импульсов | 1988 |

|

SU1608702A1 |

| Устройство для сложения длительностей импульсов | 1987 |

|

SU1548796A1 |

| Устройство для сложения длительностей импульсов | 1986 |

|

SU1332337A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство задержки импульсов | 1978 |

|

SU790205A1 |

| Устройство для вычитания и сложения импульсов | 1980 |

|

SU928629A1 |

1

Изобретение относится к вычислительной технике и ножет быть использовано в цифровых вычислитель-, ных машинах.

Известно устройство с представлением информации в виде количества последовательно сработавших бистабильных элементов, в котором каждый предыдущей элемент дает разрешение на переключение последующего СП.

Недостатками известного устройства являются сложность управления и ограниченные функциональные возможности (невозможность выполнения сложения и вычитания аналоговых величин) .

Наиболее близким по технической сущности является оптоэлектронный модуль, содержа1чий группу десятиразрядных модулей, образующих сумматор, который позволяет производить сложение либо цифровых (в виде количества импульсов), либо аналоговых (в виде длительности импульса) величин. Модуль состоит из цепочки бистабильных элементов (квантронов) с одинаковым временем срабатывания. При подаче сигнала на вход модуля последовательно возбуждаются разряды цепочки, а при заполнении всех девяти разрядов формируется импульс переноса в следующую (страшную) цепочку сумматора.

10

Недостатком данного устройства является отсутствие возможности непосредственно вычитания, поступающих на вход сигналов.

Цель изобретения - расширение об15ласти применения устройства путем организации и вычитания.

Поставленная цель достигается тем, что устройство для сложения длительностей импульсов , содержащее К групп

20 каждая из .которых содержитп- истабильных элементов, дополнительно содержит в каждой j-ой группе ( , 2,.,.,К) элементы запрета, скормирователи импульсов, элементы И и ИЛИ, причем в каждой j-ой г|5уппе еди ничный выход i-ro бистабильного элемента (,2,,..n) подключен к первому входу первого элемента И, выход которого подключен к перёому входу первого элемента ИЛИ, выход которого подключен к единичному входу (1+1)-г бистабильного элемента, нулевой выход которого подключен к первому вхо ду второго элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого подключен к нулевому входу 1-го бистабильного элемента (,3,.. .п), шина ело жения устройства подключена к первому входу первого элемента запрета j-ой Группы, выход которого подключен к второму входу первого элемента И, первый вход которого подключен к единичному выходу i-ro бистабильного элемента, выход первого эле мента запрета j-ой группы подключен к первому входу первого элемента ИЛИ выход которого подключен к единичному входу первого бистабильного эле мента единичный выход бистабиль ного элемента подключен к первому входу первого элемента И, выход которого подключен к входу первого фор мирователя импульсод, выход которого подключен к второму входу второго элемента ИЛИ, выход котсрого подключен к нулевому входу т-го бистабильного элемента (,2,...п-1) выход первого формирователя импульсов подключен к первому входу второго элемента ИЛИ, выход которого подключен к Нулевому входу п-го бистабильного элемента, выход первого формировател импульсов подключен к второму входу первого элемента запрета j-ой группы и к шине переноса в (j+1)-yю группу устройства, шина вычитания которого подключена к первому входу второго элемента запрета j-ой группы, выход которого подключен ко второму входу второго элемента И, первый вход которого подключен к нулевому выходу i-ro бистабильного элемента, выход второго элемента запрета j-ой группы гюдключен к второму входу второго элемента ИЛИ, выход которого подключен к нулевому входу п-го бистабильного элемента, вход второго формирователя подключен к выходу второго элемента И, первый вход которого подключен к нулевому выходу первого бистабильного элемента, выход вто9

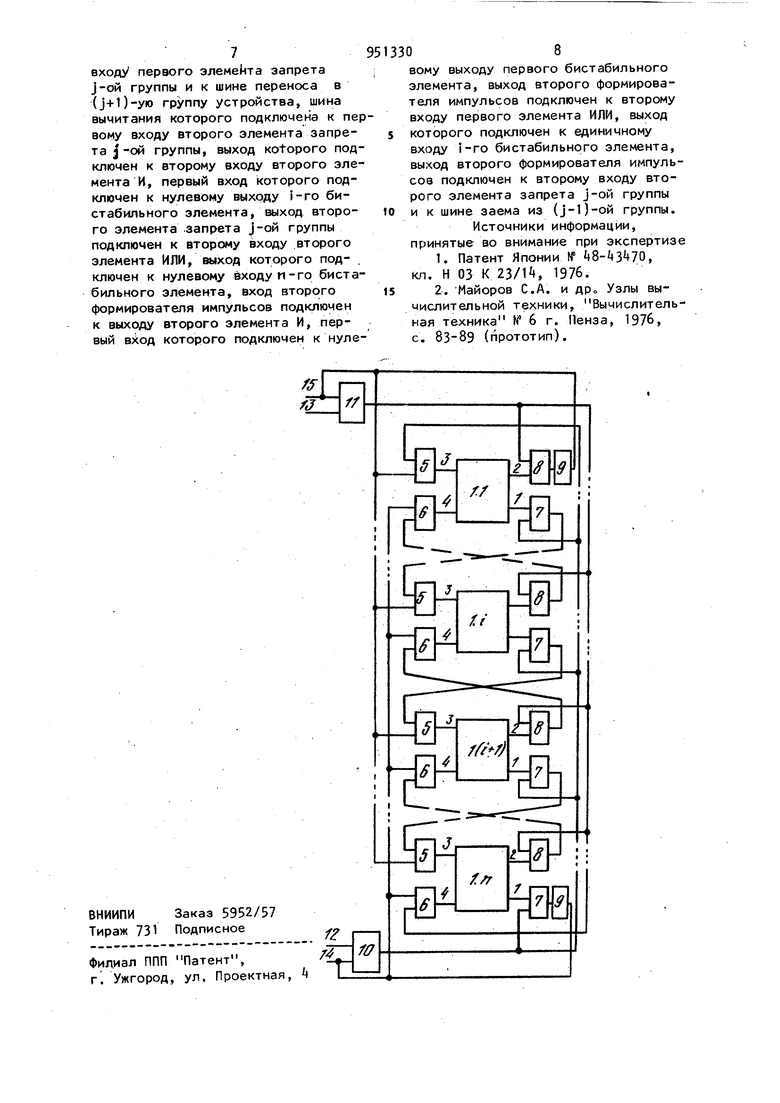

Аналогично работает устройство на вычитание при поступлении информации на шину вычитания 13. При этом 4 рого формирователя импульсов подключен к второму входу первого элемента ИЛИ, выход которого подключен к единичному входу I-го бистабильного элемента, выход второго формирователя импульсов подключен к второму входу второго элемента запрета j-ой группы и к шине заема из (j-1)-oй группы На чертеже представлена блокгсхема устройства сложения (вычитания) длительностей импульсов. Устройство содержит бистабильные элементы 1, (1,...,1п) в каждом i-ом Р-ззряде ( 1,2,... ,п) с единичным выходом 1, нулевым выходом 2, входом 3 установки в единичное состояние и входом k установки в нулевое состояние элемент ИЛИ 5, элемент ИЛИ , элемент И 7, элемент И 8, а также формирователи 9-j, Эп импульсов элементы 10 и 11 запрета, шину 12 сложения, шину 13 вычитания, шину 14 переноса, шину 15 заема. Устройство работает следующим образом. При поступлении информации на шину 12 сложения, сигнал с выхода элемента 10 запрета через элемент ИЛИ 5 поступает на вход 3 установки в единичное состояние бистабильного элемента 1.1, вызывая его установку в состояние логической 1, которая появляется на единичном выходе 1, давая разрешение на переключение следущего бистабильного элемента и т.д. Последний бистабильный элемент 1,п при установке в состояние логической 1 дает разрешение на формирование импульса переноса с выхода схемы первого формирователя 9 импульсов. Этим же импульсом все бистабильные элементы устанавливаются в состояние логического О воздействием на входы k установки в нулевое состояние через элементы ИЛИ 6, при этом длительность импульса определяется максимальным временем переключения бистабильных элементов. На время установки бистабильных элементов в состояние логического Q этот же импульс по входу Ik закрывает элемент 10 запрета, запрещая тем самым прохождение информации на входы установки в единичное состояние бистабильных элементов. бистабильные элементы последовательно устанавливаются в состояние логического О, начиная с последнего находящегося в состоянии логической 1, т.е. в обратном направлении. При обнулении первого разряда формируется импульс заема, а все бистабильные элементы устанавливаются в состояни логической Функц|1онирование устройства при оперировании с аналоговыми сигнала ми (заданных длительностью импульсо определяются следующими временными характеристиками бистабильных элементовi(N-f)r + (N-r)/iC Nr-N/if; откуда где М - основание системы счисле ния ); Т - усредненное время переклю чения бистабильных элементов; Т - допуск по времени переклю чения бистабильных элементов. Таким образом, при увеличении основания системы счисления возраст ют требования по одинаковости времени переключения бистабильных элементов. Наиболее выгодно использовать устройство в десятичной системе счисления. В этом случаа4Т 1/1 т.е разброс по времени переключени должен быть не более 5. При оперировании с цифровыми си(- налами (заданным количеством импуль сов) требования по времени переклю чения определяются формулой ,Х. ВХОДНОГО импул длительность са. - Отсюда Т 1/3Т и допустимый разброс по времени переключения составляет более 30%. Таким образом, предлагаемое устройство позволяет осуществлять сложение длительностей, заданных аналоговыми и цифровыми сигналами. Предлагаемое устройство выгодно отличается от известных, так как позволяет производить непосредственное вычисление аналоговых и цифровых сигналов. При этом нет необходимости замены операции вычитания операцией сложения в дополнительных либо обратных кодах. Формула изобретения Устройство для сложения длительностей импульсов, содержащее К групп, каждая из которых содержит п бистабильных элементов, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения вычитания длительностей импульсов, устройство дополнительно содержит в каждой j-ой группе (,2,...K) элементы запрета, формирователи импульсов, элементы И и ИЛИ, причем в каждойj -ой группе единичный выход i-ro бйстабильного элемента :(,2,...,п) подключен к первому входу первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, выход которого подключен к единичному входу (i+1)-ro бйстабильного элемента, нулевой выход которого подключен к первому входу второго элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого подключен к нулевому входу 1-го бйстабильного элемента (,3,...,п), шина сложения устройства подключена к первому входу первого элемента запрета j -ой группы, выход которого подключен к второму входу первого элемента И, первый вход которого подключен к единичному выходу 1-го бйстабильного элемента,выход первого элемента запрета j-ой группы подключен к первому входу первого элемента ИЛИ, выход которого подключен к единичному входу первого бйстабильного элемента, единичный выход п-го бйстабильного элемента подключен к первому входу первого элемента И, выход которого подключен к входу первого формирователя импульсов, выход которого подключен к второму входу второго элементна ИЛИ, выход которого подключен к нулевому входу т-го бйстабильного элемента (,2,...п-1), выход первого формирователя импульсов подключен к первому входу второго элемента ИЛИ, выход которого подключен к нулевому входу п-го бйстабильного элемента, выход первого формирователя импульсов подключен к второму входУ первого элемейта запрета j-ой группы и к шине переноса в (j+1)-yio группу устройства, шина вычитания которого подключена к пе вому входу второго элемента запрета j -ой группы, выход Kotoporo под ключен к второму входу второго эле мента и, первый вход которого подключен к нулевому выходу i-ro бистабильного элемента, выход второго элемента .запрета j-ой группы подключен к второму входу второго элемента ИЛИ, выход которого подключен к нулевому входу и-го биста бильного элемента, вход второго формирователя импульсов подключен к выходу второго элемента И, первый вХод которого подключен к нуле 08 вому выходу первого бистабильного элемента, выход второго формирователя импульсов подключен к второму входу первого элемента ИЛИ, выход которого подключен к единичному входу 1-го бистабильного элемента, выход второго формирователя импульсов подключен к второму входу второго элемента запрета j-ой группы и к шине заема из (j-l)-oй группы. Источники информации, принятые во внимание при экспертизе 1. Патент Японии № , кл, Н 03 К 23/1, 1976. 2. Майоров С.А. и др Узлы вычислительной техники, Вычислительная техника К 6 г. Пенза, 1976, 83-89 (прототип).

Авторы

Даты

1982-08-15—Публикация

1980-05-12—Подача