Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ и устройствах обработки цифровой информации о

Цель изобретения - расширение функциональных возможностей за счет организации процесса операции суммирования/вычитания с возможностью смены выполняемой операции в одном цикле вычисления результата

На чертеже изображена схема последовательного сумматора вычитателЯо

Последовательный сумматор-вычита- тель содержит шесть элементов И 1-6, три элемента ИЛИ 7,8 и 9, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10, 11, первый и второй триггеры 12 и 13, прямой и инверсный входы 14 и 15 первого операнда, прямой и инверсный входы 16 и 17 второго операнда, прямой и инверсный выходы 18 и 19 переноса из предыдущего разряда, прямой и инверсный выходы 20 и 21 заема из предыдущего разряда, вход 22 управления сложением, вход 23 управления вычислением, вход 24 тактирования, вход 25 установки и выход 26 результата сумматора-вычитателя,

. Последовательный сумматор-вычита- тель -по своей сущности является синхонным автоматом МурНо

Первый - шестой элементы 0 1-6, ервый и второй элементы ИЛИ 7 и 8 образуют комбинационную схему, котоая формирует текущую функцию возбуждения для элементов памяти (первого и второго триггера 12,13) в зависимости от входных сигналов и текущего состояния сумматора вычитате- я. Причем эта комбинационная схема организована таким образом, что в роцессе, вычисления одного выходного числа возможна смена выполнений одной операции на другую (сложение на вычитание и наоборот.

Первый и второй элементы ИСКЛЮЧАЩЕЕ ИЛИ 10, 11 и третий элемент ЛИ 9 образуют комбинационную схему, формирующую текущие значения выходного бита, в зависимости от состояния первого и второго операндов, которые поступают на первый и второй прямые входы 14 и 16 первого и второго операнда и текущего внутреннего состояния, определяемые первым и вторым триггерами 12 и 13

Последовательный сумматор-вычита- тель работает следующим образом.

В начале каждого цикла вычисле- ния производится обнуление первого и второго триггеров 12 и 13 импульсным сигналом, поступаюищм со входа 25 установки

Затем по прямому и инверсному входам 14,15 первого операнда и прямому и инверсному входам 16,17 второго операнда начинают последовательно поступать биты чисел соответственно первого с тагаемого (уменьшаемого) и второго слагаемого (вычитаемого) Поступление каждого бита операндов сопровождается тактовыми сигналами, поступшощими по входу 24 тактирования. При этом число тактовых импульсов, поступающих по входу 24 такти зо- ва1шя, равняется разрядности операн дов.

Для наглядности описания положим, что в начале цикла вычисления выполгняется операция сложения В этом

случае на вход 22 поступает единичный потенциал, а на вход 23 - нулевой потенциал. После прихода очередных бит о перандов в зависимости от

их значения и значения сигнала на

выходе 18, который поступает с прямо- го выхода первого триггера 12, на выходе второго элемента ИС1ШЮЧАЩЕЕ ИЛИ 11 формируется выходной бит суммы. Комбинационная схема, образованная первым-третьим элементами 1-3 - и первым элементом ИЛИ 7, формирует функцию возбуждения (сигнал лог. О или лог о 1) для первого триггера 12 с приходом тактового импульса по входу 2 тактирования значение сигнала с выхода первого элемента ИЛИ 7 переписывается в первый триггер 12 и будет определять внутреннее

состояние устройства в следующем такте вычнсл-енияо На выходе второго элемента ИЛИ 8 во время выполнения операции сложения будет присутствовать сигнал лог , так как четвер-

тый и пятый элементы И 4,5 блокируются сигнало)м лоГо О входа 23 вычитания, а шестой элемент И 6 закрыт нулевым потенциалом с прямого выхода второго триггера 13о

После смены выполняемой операции, что определяется появлением сигнала лог,О на входе 22 и сигнала лог, 1 на входе 23, на выходе первого элемента ИЛИ 7 генерируется сигнал

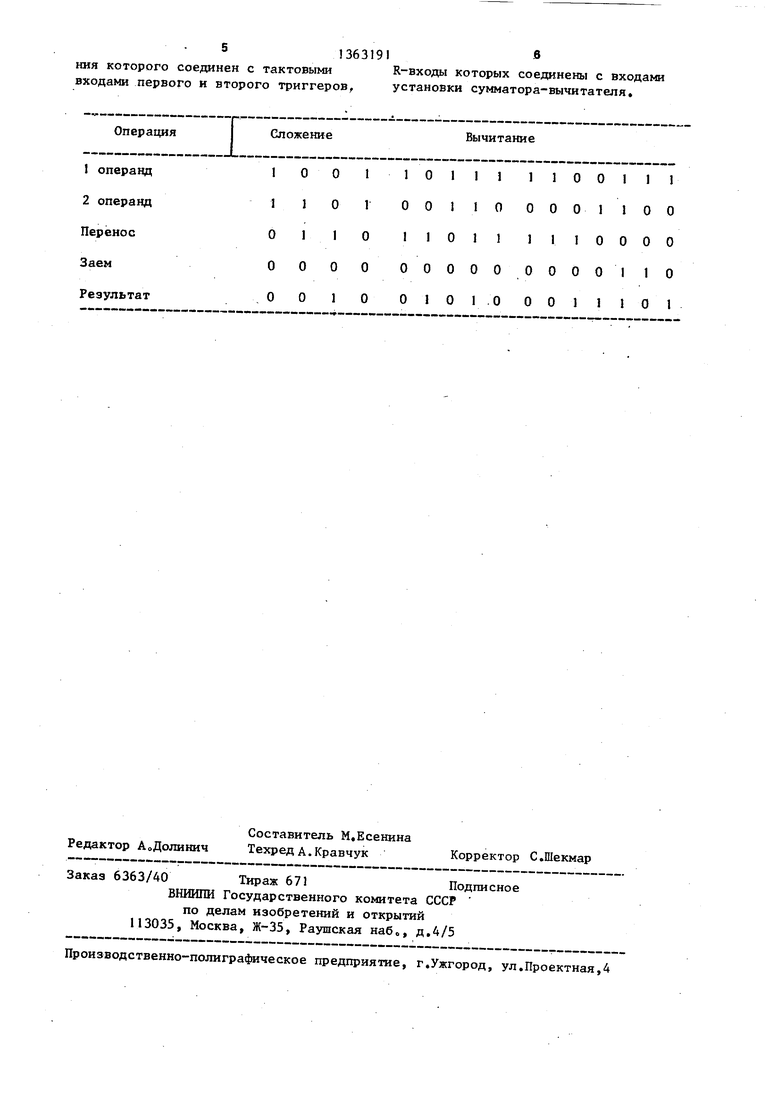

лог. 1 функции возбуждения 1 триггера 12 до тех пор, пока по прямому входу 14 первого операнда поступают единичные биты уменьшаемого, а первый триггер 12 находится в единичном состоянии о Если же хотя бы одно из указанных условий не выполняется или поступает единичный бит вычитаемого по прямому входу 16 второго операнда, то на выходе первого элемента ИЛИ 7 до конца цикла вычисления будет генерироваться сигнал лог. О, На выходе второго элемента ИЛИ 8 сигнал функции возбуждения второго триггера 13 первый раз принимает еди шчное значение в случае единичного бита на прямом входе 16 второго операнда при нулевых значениях на прямом входе 14 первого операн да и прямом выходе первого триггера 12. После этого цикл вычисления продолжается с генерацией сигналов на шине 20 заема. В таблице приведен пример вычисления, при котором про- изводится сложение чисел 11011001 и 11001011 и вычитание чисел 11100111 и 0011111, которое выполняется в одном цикле вычисления

Работа последовательного сумматора-вычитателя, в случае когда сначала выполняется операция вычитания, полностью аналогична описанному. Устройство в зависимости от выполняемой задачи позволяет менять тип выполняемой операции произвольное количество раз в течение одного цикла вычисления. Формула изобретения

Последовательный сумматор-вычи- татель, содержащий шесть элементов И и два элемента ИЛИ, причем прямой вход первого операнда (слагаемое- уменьшаемое) подключен к первым входа первого и второго элемента И, инверсный вход первого операнда соединен с первыми входами.третьего и четвертого элементов И, прямой вход второго операнда: (слагаемое - вычи- таемое) подключен к вторым входам первого, пятого, третьего и шестого элементов И, инверсный вход второго операнда соединен с вторым входом

четвертого элемента И, прямой вход переноса из предыдуш,его разряда подключен к третьим входам пятого и второго элементов И, инверсный вход переноса из предыдуш;его разряда соеQg о 5

0

5 Q

5

0

5

динен с третьим входом третьего элемента И, вход управлеш-1я сложением подключен к третьему входу первого элемента И, выходы первого, пятого и третьего элементов И соединены соответственно с первым, вторым, третьим входами первого элемента ИЛИ, а выходы третьего, шестого и четвертого эл.ементов И подключены к первому, второму, .третьему входам второго элемента ИЛИ соответственно, отличающийся тем, что, с целью расширения функциональных возможностей за счет организации процесса суммирования - вычитания с возможностью смены выполняемой операции в одном цикле вычисления результата, в него введены третий элемент ИЛИ, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и первый и второй триггеры, причем инверсный вход второго операнда подключен к вт орому входу второго элемента И, прямой вход заема из предыдущего разряда соединен с третьими входами пятого и четвертого элементов И и первым входом третьего элемента ИЛИ, второй вход которого подключен к прямому входу переноса из предыдущего разряда, инверсный вход заема из предьщущего ра;зряда соединен с четвертым входом первого элемента И, вход управления сложением подключен к первому входу пятого элемента И, вход управления вычитанием соедине}: с четвертым вхо-. дом третьего элемента И и первым входом шестого элемнта И, выход пёр- . вого элемента ИЛИ соединен с о6„- входом первого триггера, прямой и инверсный выходы которого подключены соответственно к второму входу третьего элемента ИЛИ и третьему входу третьего элемента И, выход вто- рого элемента ИЛИ соединен с D-BXO- дом второго триггера, прямой и инверсный выходы которого подключены соответственно к первому входу третьего элемента РШИ и к четвертому входу первого элемента И, первый и второй входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с прямыми входами соответственно первого и второго операндов, а выход подключен к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом третьего элемента ИЛИ, а выход является выходом суммы сумматора-вычитателя, вход тактировавходами первого и второго триггеров,

Операция

I

Сложение

I 00 110111 1 1 О 1 00110 0110 11011 0000 00000 0010 01010

установки сумматора-вычитателя.

Вычитание

100111 001 100 110000 0001 10 0 1 101

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный сумматор-вычитатель | 1986 |

|

SU1424009A1 |

| Устройство для сложения-вычитания | 1981 |

|

SU1005037A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Устройство для выполнения базовой операции быстрого преобразования Хартли-Фурье вещественных последовательностей | 1990 |

|

SU1718229A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для вычисления квадратного корня | 1988 |

|

SU1501051A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

Изобретение относится к вычислительной техника и может быть использовано в арифметических устройствах ЭВМ и устройствах цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей за счет организации процесса сложения (вычитания) с возможностью смены выполняемой операции .в одном цикле вычисления результата. Последовательный сумматор-вычитатель содержит шесть элементов И 1-6, три элемента ИЛИ 7-9, два элемента ИСЮТЮЧАЮЩЕЕ ИЛИ 10,11, два триггера 12,13. 1 Ш1. (С (Л S -о оэ О) со со

| Сумматор последовательного действия | 1980 |

|

SU920710A1 |

| Каган Б,М | |||

| и Каневский МвМ, Цифровые вычислительные системы М.: Энергия, 1974, с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

| . | |||

Авторы

Даты

1987-12-30—Публикация

1986-07-18—Подача