Изобретение относится к вычислительной технике и может использоваться для сопряжения микроЭВМ с периферийными устройствами.

Целью изобретения является повышение производительности.

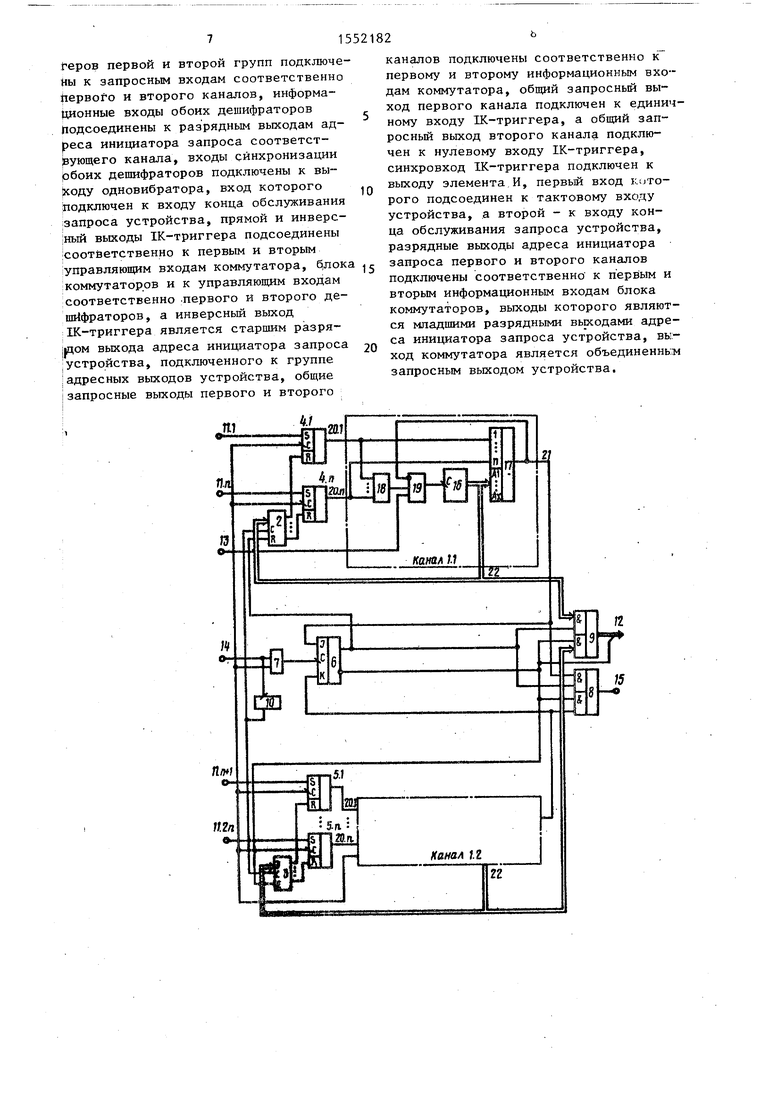

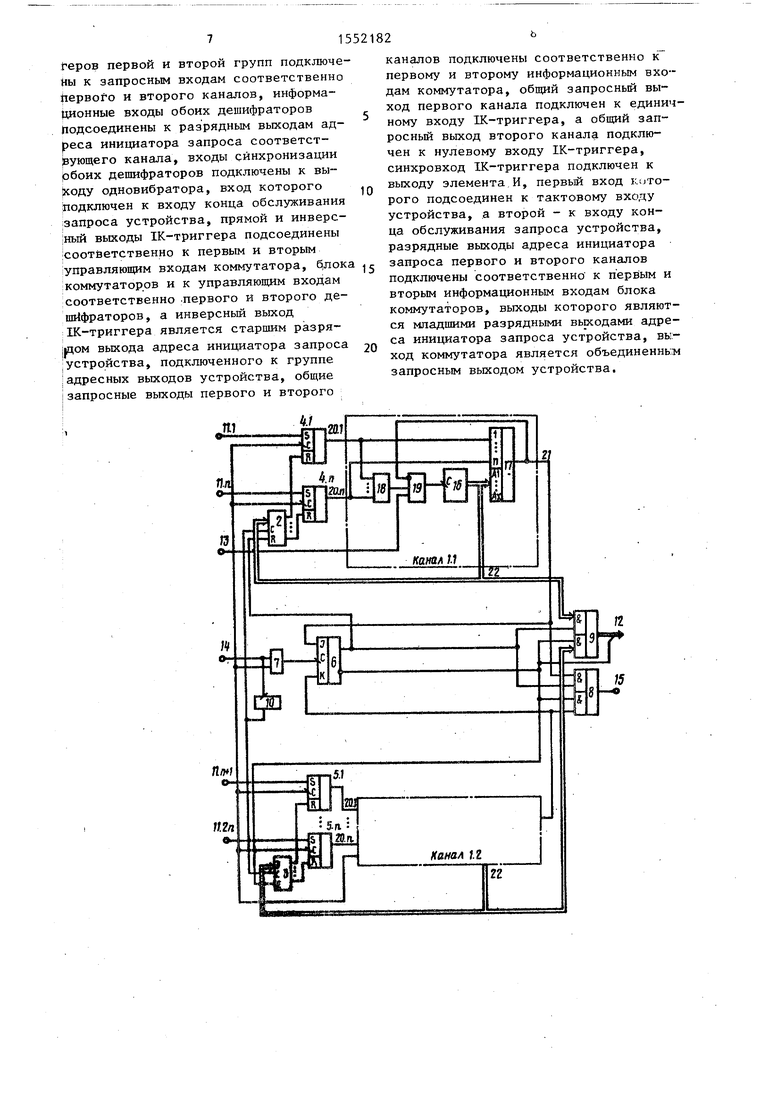

На чертеже приведена схема устройства.

Устройство содержит каналы 1.1 и 1.2 формирования адреса инициатора

запроса, дешифраторы 2 и 3, группы триггеров 4 и 5, IK-триггеров 6, элемент И 7, коммутатор 8, блок 9 коммутаторов, одновибратор 10, запросные входы 11, выход 12 адреса инициатора запроса, тактовый вход 13, выход 14 конца обслуживания запроса, объединенный запросный выход .Каждый канал 1.1 и 1.2 содержит счетчик 16, мультиплексор 17, элемент ИЛИ 18,

эпемент И 19, группу 20 запросных входов, общий запросный выход 21, разрядные адресные выходы 22 канала,

Устройство работает следующим об- разом.

В исходном состоянии запросы на входы 11 не поступают. Триггеры групп 4 и 5, счетчики 16 находятся в О, элементы И 19 закрыты О, поступающими с выходов элементов ИЛИ 18, и запрещают прохождение тактовых импульсов с входа 13 на входы счетчиков 16. На выходах мультиплексоров 17 действуют нулевые сигналы, что свидетельствует об отсутствии запросов, и, следовательно, на выходе 15 будет О. IK-триггер находится в произвольном состоянии. С входа 14 на оход элемента И 7 поступает единичный сигнал, извещающий устройство о том, что внешнее устройство управления свободно и готово к обслуживанию запросов.

Каждый канал 1.1 и 1.2 может функ Йионироватъ в активном или пассивном режиме. При работе в активном режиме в канале осуществляется формирование адреса инициатора запроса и выдача этого адреса на адресные выходы 12 устройства одновременно с выдачей на объединенный запросный выход 15 устройства единичного сигнала запроса. При работе в пассивном режиме в канале осуществляется формирование адреса инициатора запроса, но он так же, как и запрос, с выхода канала на выход устройства не передается. Режимы каналов определяются состоянием 1К-триггера 6. Если он находится в единичном состоянии, то канал 1.1 является активным, а канал 1.2 - пассивным. Если этот триггер находится в нулевом состоянии, то наоборот.

При поступлении запросов на один или несколько запросных входов 1 устройства устанавливаются в единичное состояние соответствующие триггеры первой 4 и второй 5 групп. Первый поступивший запрос в каждом канале 1.1 и 1.2 либо в одном из каналов через элемент ИЛИ 18 поступает на вход элемента И 19 и открывает его для прохождения тактовых импульсов с тактового входа 13 устройства на счетны вход С счетчика 16.

Счетчики 16 одного или обоих каналов начинают подсчет числа импульсов. Текущий двоичный код с выхода

0

g

5

5

0

5

0

45

0

счетчика 16 поступает на управляющие входы мультиплексора 17 соответствующего канала. При этом к выходу мультиплексора 17 последовательно подключаются выходы триггеров группы 4 длг первого канала или выходы триггеров группы 5 для второго канала. Когда двоичный код на выходе счетчика 6 совпадает с адресом источника, записавшего сигнал запроса в один из триггеров первой 4 либо второй 5 группы, на выходе соответствующего мультиплексора 17 возникает единичный сигнал, означающий, что адрес инициатора запроса сформирован. Этот сигнал, поступая на инверсный вход элемента И 19, запирает его, счетчи останавливается, и в нем будет записан код адреса инициатора запроса, который через адресные выходы 22 соответствующего канала поступает на информационные входы блока 9 коммутаторов. Одновременно единичный сигнал в качестве обобщенного запро-- ного сигнала с выхода 21 канала поступает на информационные входы коммутатора 8. I

Предположим, что первым сформирован адрес инициатора запроса в первом канале 1.1. Тогда, если IK-триггер b находится в единичном состоянии, единичный сигнал с запросного выхода 21.1, поступая на 1-вход IK-триггера, оставляет его в том же состоянии. Если IK-триггер находится в нулевом состоянии, то через открытый сигналам с входа 14 устройства элемент И 7 синхроимпульс с тактового входа 13 поступает На С-вход IK-триггера и своим задним фронтом устанавливает его в единичное состояние, делая первый из каналов активным. При этом сигнал запроса и код адреса инициатэ- ра запроса с выхода канала 1.1 прохэ- дят, соответственно, через коммутатор 8 на объединенный запросный выход 15 и через блок 9 коммутаторов на адресную выходную шину 12. При этом в старший разрядный выход шины 12 с инверсного выхода триггера 6 передается нулевой сигнал. После приема запросного сигнала с выхода 15 внешнее управляющее устройство начинает его обслуживание и снимает с входа 14 устройства единичный сигнал, что запрещает работу элемента Л 1 и, следовательно, делает переключе

ние триггера 6 невозможным. Режим каналов меняться не может.

После окончания обслуживания данного запроса внешнее управляющее устройство устанавливает на входе 14 единичный сигнал. Передним фронтом этого сигнала запускается одновиб- ратор 10. С выхода одновибратора 10 импульс, длительность которого достаточна для гарантированного сброса триггеров групп 4 и 5, поступает на синхровходы дешифраторов 2 и 3. Но единичный сигнал появляется на одном из выходов только одного дешифратора так как единичный сигнал с прямого или инверсного выхода триггера 6 поступает на управляющий вход одного из дешифраторов. Для рассматриваемого случая открыт дешифратор 2. На информационные входы дешифратора 2 поступает при этом со счетчика 16 код адреса источника обслуженного запроса. Следовательно, в момент срабатывания одновибратора 10 дешифратор 2 выдает импульс сброса того триггера 4, в котором был задисан обслуженный запрос, После этого на выхде 21 канала появляется нулевой сигнал и с выхода 15 устройства снимается общий сигнал запроса. Канал 11 может приступать к формированию адреса очередного источника запроса,если к этому времени запрос записался в один из триггеров группы 4.

Если к моменту окончания обслуживания запроса в канале 1.1, в канале 1.2 сформирован адрес источника нового запроса, то на выходе 21 канала 1.2 наблюдается единичный сигнал, который поступает на К-вход 1К-триг- гера. После появления единичного сигнала на входе 14 устройства, а его появление предусмотрено только в паузах между тактовыми импульсами, по заднему фронту первого же синхроимпульса триггер 6 переключается в нулевое состояние. Единичный сигнал с инверсного выхода триггера 6 открывает вторые половины коммутатора 8 и блока 9 коммутаторов, и обобщенный запрос и адрес инициатора запроса с выходов 21 и 22 соответственно канала 1.2 поступает на выходы 15 и 12 устройства. Канал 1.2 становится ак

тивным, а канал 1.1 - пассивным. Общий обслуживающий орган принимает к обслуживанию запрос канала 1.2. В это время канал 1.1 может продолжать

10

15 521826

формировать адрес инициатора очередного запроса.

Если в определенный момент времени оба канала одновременно сформируют адреса инициаторов, то единичные сигналы с выходов 21 каналов 1.1 и 1.2 одновременно поступают на I- и К-входы триггера 6. В этом случае триггер переходит в инверсное состояние, и устройство подключает к об- . служивающему органу сначала один запрос, затем другой. Формула изобретения

Устройство для обслуживания запросов, содержащее два дешифратора, две группы из п триггеров каждая (где п - N/2, N - количество запросов источников запросов) и первый канал формирования адреса инициатора запроса, включающий счетчик, мультиплексор, элемент И и элемент ИЛИ, при этом счетный вход счетчика соединен с выходом элемента И, прямой вход которого соединен с тактовым входом устройства, выход мультиплексора является общим запросным выходом канала и подсоединен к инверсному входу элемента И, второй прямой вход которого подсоединен к выходу элемента ИЛИ, п входов элемента ИЛИ являются запросными входами канала и подсоединены к соответствующим информационным

входам мультиплексора, К разрядных выходов счетчика (где К Iog2n - число разрядов двоичного кода числа, подключаемых к каналу источников запросов) подключены к соответствующим управляющим входам мультиплексора и являются разрядными выходами адреса инициатора запроса канала, запросные входы устройства с первого по n-й и с (п+1)-го по N-й соединены соответственно с S-входами соответствующих триггеров первой и второй групп, R-входы которых соединены с соответствующими выходами соответственно первого и второго дешифраторов,

отличающееся тем, что, с

целью повышения производительности, в него дополнительно введены второй канал формирования адреса инициатора запроса, IK-триггер, коммутатор, блок коммутаторов, элемент И и одновибра- тор, при этом С-входы триггеров пер- - вой и второй групп подключены к тактовому входу устройства и к первому входу элемента И, прямые выходы тригJH

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Устройство динамического приоритета | 1987 |

|

SU1495793A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1474646A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1476465A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения микро-ЭВМ с периферийными устройствами. Цель изобретения - повышение производительности. Устройство содержит два канала формирования адреса инициатора запроса, два дешифратора, две группы триггеров, J K-триггер, элемент И, коммутатор, блок коммутаторов. Каждый канал формирования адреса инициатора запроса содержит счетчик, мультиплексор, элемент ИЛИ и элемент И. В устройстве уменьшается время определения адреса инициатора запроса за счет сокращения разрядности счетчика, происходит параллельное определения адресов инициаторов запросов, если два запроса поступили одновременно в оба канала, обеспечивается переключение одного канала в активный, а другого - в пассивный режим. При этом активный канал определяет адрес инициатора запроса и передает его вместе с запросом на выход устройства, а пассивный только определяет адрес инициатора запроса и запоминает его для дальнейшей выдачи. Устройство позволяет запоминать факт прихода очередного запроса во время обслуживания текущего запроса и формировать адреса инициаторов запросов последовательно в зависимости от их значений и времени поступления от них запросов. 1 ил.

| Устройство для объединения запросов от каналов связи | 1970 |

|

SU716039A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для объединения запросов с формированием адреса инициатора запроса | 1982 |

|

SU1056195A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-23—Публикация

1988-07-05—Подача