1

Изобретение относится к автоматике и вычислительной технике, и может быть использовано при разработке устройств управления ЦВМ и вычислительных и управляющих систем.

Целью изобретения является увеличение глубины контроля устройства.

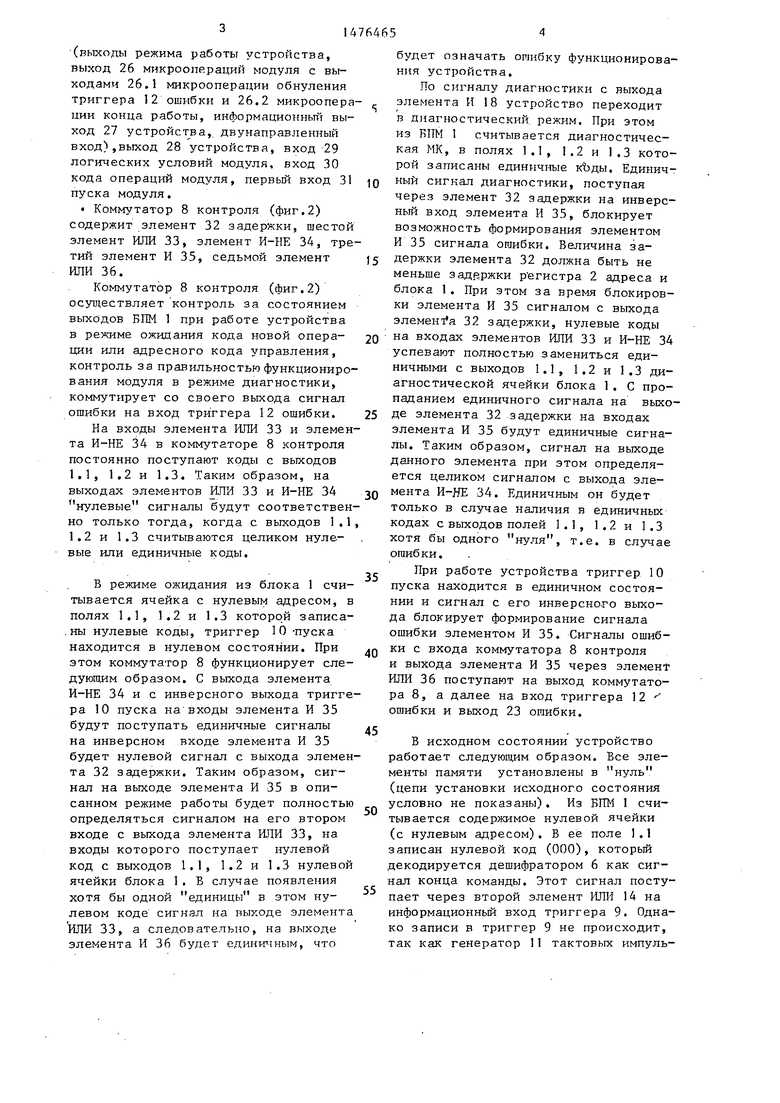

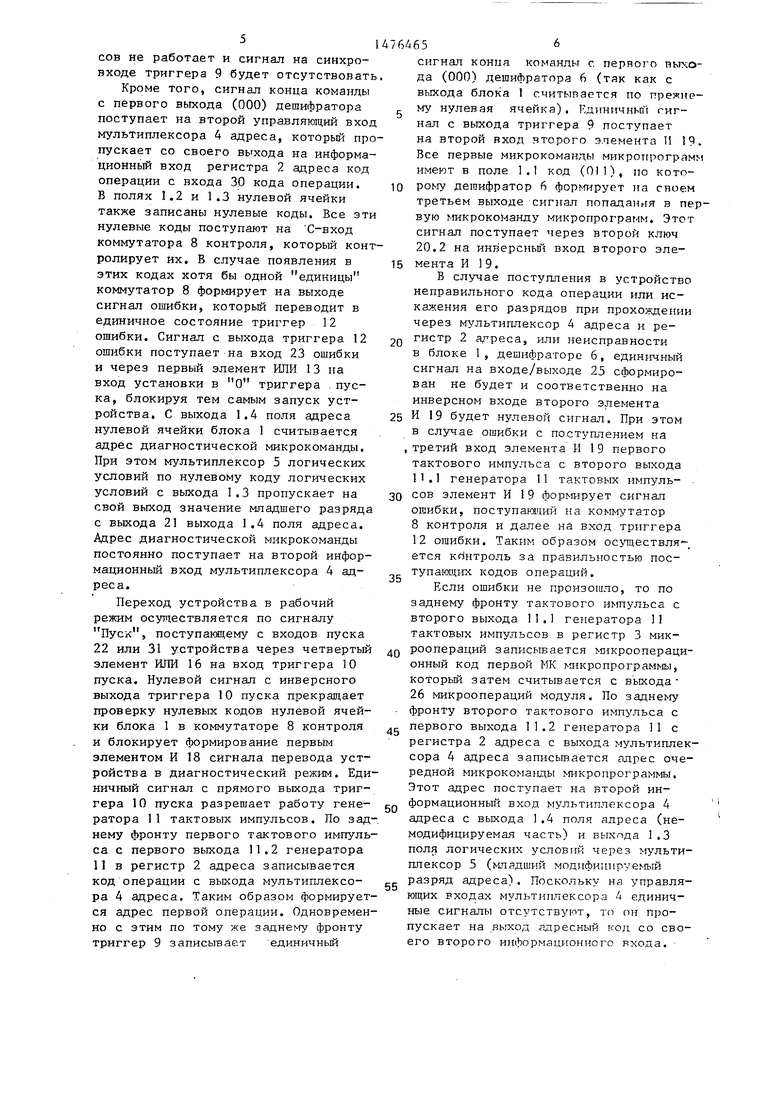

На фиг.1 приведена функциональная схема предлагаемого микропрограммного устройства управления; на фиг.2 - функциональная схема коммутатора контроля.

Устройство (фиг.1) содержит блок 1 памяти микрокоманд ( полями режима работы 1,1, кода микроопераций 1.2, кода логических условий 1-3 и адреса 1.4, регистры 2 адреса И 3

микроопераций, мультиплексоры 4 адреса И 5 логических условий, первый и второй дешифраторы 6 и 7, коммутатор 8 контроля, триггер 9, триггер 10 пуска, генератор 11 тактовых импульсов с первым 11.1 и вторым 11.2 выходами, триггер 12 ошибки, первый 13, второй 14, третий 15, четвертый 16 и пятый 17 элементы ИЛИ, первый 18 и второй 19 элементы И, первый 20.1, второй 20,2, ключи с тристабильным выходом, блок 20.3 ключей с тристабильным выходом, выход 21 младшего разряда поля адреса БПМ 1, вход 22 l-k-го сигналов пуска устройства, выход 23 ошибки устройства, первый 24 и второй 25 двунапрпвпенчые входы

4ь

05 Ј ОЭ

сл

314764

(выходы режима работы устройства, выход 26 микроопераций модуля с выходами 26,1 микрооперации обнуления триггера 12 ошибки и 26.2 микроопера- ции конца работы, информационный выход 27 устройства, двунаправленный вход),выход 28 устройства, вход 29 логических условий модуля, вход 30 кода операций модуля, первый вход 31 ю пуска модуля.

Коммутатор 8 контроля (фиг.2) содержит элемент 32 задержки, шестой элемент ИЛИ 33, элемент И-НЕ 34, третий элемент И 35, седьмой элемент ИЛИ 36.

Коммутатор 8 контроля (фиг.2) осуществляет контроль за состоянием выходов БПМ 1 при работе устройства в режиме ожидания кода новой опера- ции или адресного кода управления,

контроль за правильностью функционирования модуля в режиме диагностики, коммутирует со своего выхода сигнал ошибки на вход триггера 12 ошибки.

На входы элемента ИЛИ 33 и элемента И-НЕ 34 в коммутаторе 8 контроля постоянно поступают коды с выходов 1.1, 1.2 и 1.3. Таким образом, на выходах элементов ИЛИ 33 и И-НЕ 34 нулевые сигналы будут соответственно только тогда, когда с выходов 1.1 1.2 и 1.3 считываются целиком нулевые или единичные коды.

В режиме ожидания из блока 1 считывается ячейка с нулевым адресом, в полях 1.1, 1.2 и 1.3 которой записаны нулевые коды, триггер 10 -пуска находится в нулевом состоянии. При этом коммутатор 8 функционирует следующим образом. С выхода элемента И-НЕ 34 и с инверсного выхода триггера 10 пуска на входы элемента И 35 будут поступать единичные сигналы на инверсном входе элемента И 35 будет нулевой сигнал с выхода элемента 32 задержки. Таким образом, сигнал на выходе элемента И 35 в описанном режиме работы будет полностью определяться сигналом на его втором входе с выхода элемента ИЛИ 33, на входы которого поступает нулевой код с выходов 1.1, 1.2 и 1.3 нулевой ячейки блока 1. В случае появления хотя бы одной единицы в этом нулевом коде сигнал на выходе элемента ИЛИ 33, а следоватепьно, на выходе элемента И 36 будет единичным, что

5

0

0

с

0

0

5

будет означать ошибку функционирования устройства,

По сигналу диагностики с выхода элемента И 18 устройство переходит в диагностический режим. При этом из Б1ТМ 1 считывается диагностическая МК, в полях 1.1, 1.2 и 1.3 которой записаны единичные кЪды. Единичный сигнал диагностики, поступая через элемент 32 задержки на инверсный вход элемента И 35, блокирует возможность формирования элементом И 35 сигнала ошибки. Величина задержки элемента 32 должна быть не меньше задержки регистра 2 адреса и блока 1. При этом за время блокировки элемента И 35 сигналом с выхода элемента 32 задержки, нулевые коды на входах элементов ИЛИ 33 и И-НЕ 34 успевают полностью замениться единичными с выходов 1.1, 1.2 и 1.3 диагностической ячейки блока 1. С пропаданием единичного сигнала на выходе элемента 32 задержки на входах элемента И 35 будут единичные сигналы. Таким образом, сигнал на выходе данного элемента при этом определяется целиком сигналом с выхода элемента И-ЯЕ 34. Единичным он будет только в случае наличия в единичных кодах с выходов полей 1.1, 1.2 и 1.3 хотя бы одного нуля, т.е. в случае ошибки.

При работе устройства триггер 10 пуска находится в единичном состоянии и сигнал с его инверсного выхода блокирует формирование сигнала ошибки элементом И 35. Сигналы ошибки с входа коммутатора 8 контроля и выхода элемента И 35 через элемент ИЛИ 36 поступают на выход коммутатора 8, а далее на вход триггера 12 ошибки и выход 23 ошибки.

В исходном состоянии устройство работает следующим образом. Все элементы памяти установлены в нуль (цепи установки исходного состояния условно не показаны). Из БГГМ 1 считывается содержимое нулевой ячейки (с нулевым адресом). В ее поле 1.1 записан нулевой код (000), который декодируется дешифратором 6 как сигнал конца команды. Этот сигнал поступает через второй элемент ИЛИ 14 на информационный вход триггера 9. Однако записи в триггер 9 не происходит, так как генератор 11 тактовых импульсов не работает и сигнал на синхро- входе триггера 9 будет отсутствовать

Кроме того, сигнал конца команды с первого выхода (000) дешифратора поступает на второй управляющий вход мультиплексора 4 адреса, который про1 пускает со своего выхода на информационный вход регистра 2 адреса код операции с входа 30 кода операции. В полях 1.2 и 1.3 нулевой ячейки также записаны нулевые коды. Все эти нулевые коды поступают на С-вход коммутатора 8 контроля, который конт ролирует их. В случае появления в этих кодах хотя бы одной единицы коммутатор 8 формирует на выходе сигнал ошибки, который переводит в единичное состояние триггер 12 ошибки. Сигнал с выхода триггера 12 ошибки поступает на вход 23 ошибки и через первый элемент ИЛИ 13 на вход установки в О триггера пуска, блокируя тем самым запуск устройства. С выхода 1.4 поля адреса нулевой ячейки блока 1 считывается адрес диагностической микрокоманды. При этом мультиплексор 5 логических условий по нулевому коду логических условий с выхода 1.3 пропускает на свой выход значение младшего разряда с выхода 21 выхода 1.4 поля адреса. Адрес диагностической микрокоманды постоянно поступает на второй информационный вход мультиплексора 4 адреса.

Переход устройства в рабочий режим осуществляется по сигналу Пуск, поступающему с входов пуска 22 или 31 устройства через четвертый элемент ИЛИ 16 на вход триггера 10 пуска. Нулевой сигнал с инверсного выхода триггера 10 пуска прекращает проверку нулевых кодов нулевой ячейки блока 1 в коммутаторе 8 контроля и блокирует формирование первым элементом И 18 сигнала перевода устройства в диагностический режим. Еди- ничный сигнал с прямого выхода триггера 10 пуска разрешает работу генератора 11 тактовых импульсов. По зад- нему фронту первого тактового импульса с первого выхода 11.2 генератора 11 в регистр 2 адреса записывается код операции с выхода мультиплексора 4 адреса. Таким образом формирует- ся адрес первой операции. Одновременно с этим по тому же заднему фронту триггер 9 записывает единичный

764656

сигнал конца команды с. первого выхода (000) дешифратора 6 (тяк как с выхода блока 1 считывается но прежнр- му нулевая ячейка). Единичный гиг- нал с выхода триггера 9 поступает на второй вход второго эпемента И 19. Все первые микрокоманды микропрограмм имеют в поле 1.1 код (0)1), по котоЮ рому дешифратор 6 формирует на своем третьем выходе сигнал попадания в первую микрокоманду микропрограмм. Этот сигнал поступает через второй ключ 20.2 на инверсный вход второго эле15 мента И 19.

В случае поступления в устройство неправильного кода операции или искажения его разрядов при прохождении через мультиплексор 4 адреса и ре20 гистр 2 адреса, или неисправности в блоке 1, дешифраторе б, единичный сигнал на входе/выходе 25 сформирован не будет и соответственно на инверсном входе второго элемента

25 И 19 будет нулевой сигнал. При этом

в случае ошибки с поступлением на «третий вход элемента И 19 первого тактового импульса с второго выхода 11.1 генератора 11 тактовых импуль30 сов элемент И 19 формирует сигнал ошибки, поступающий на коммутатор 8 контроля и далее на вход триггера 12 ошибки. Таким образом осуществляв ется контроль за правильностью поступающих кодов операций.

Если ошибки не произошло, то по заднему фронту тактового импульса с второго выхода 11.1 генератора 1 тактовых импульсов в регистр 3 мик40 роопераций записывается микрооперационный код первой МК микропрограммы, который затем считывается с выхода 26 микроопераций модуля. По заднему фронту второго тактового импульса с

.,- первого выхода 11.2 генератора 11 с регистра 2 адреса с выхода мультиплексора 4 адреса записывается адрес очередной микрокоманды микропрограммы. Этот адрес поступает на второй информационный вход мультиплексора 4 адреса с выхода 1.4 поля адреса (немодифицируемая часть) и выхода 1.3 поля логических условий через мультиплексор 5 (младший модифицируемый разряд адреса). Поскольку на управляющих входах мультиплексора 4 единичные сигналы отсутствуют, то он пропускает на выход адресный код со своего второго информационного входа.

35

50

55

to

15

20

71476465

В микрокомандах ветвления младший разряд адреса формируется следующим образом. Код логических условий поступает с выхода 1.3 на адресный вход мультиплексора 5 логических условий. Мультиплексор 5 выделяет на свой выход в качестве младшего (модифицируемого) разряда адреса следующей МК значение нужного логического условия со входа 29 логических условий модуля. В линейных же микрокомандах в поле 1.3 записаны специальный код, по которому мультиплексор 5 осуществляет передачу на свой выход значения сигнала с выхода 21 младшего разряда выхода поля 1.4 адреса,

В поле 1.1 признака последних Ж микропрограмм записывается код (000), по которому дешифратор б Ж формирует на своем первом выходе единичный сигнал конца команды. По этому сигналу мультиплексор 4 адреса пропускает с входа 30 на информационный вход регистра 2 адреса очередной код операции.

Сигнал, поступающий с входа/выхода 24 на второй вход второго элемента И 18, если на первом входе первого элемента

нал, т.е. в отключенном состоянии устройства вызовет переход в диаг- ностическией режим. Сигнал диагностики с выхода первого элемента И 18 поступает на первый управляющий вход мультиплексора 4 адреса и В-вход коммутатора 8 контроля. Коммутатор 8 контроля согласно описанному алгоритму своей работы временно прекращает контролировать коды с выходов 1.1, 1.2 и 1.3. Мультиплексор 4 адреса по единичному сигналу на своем первом управляющем входе пропускает на свой выход адрес диагностической микрокоманды, который с выхода 1.4 нулевой ячейки блока 1 и выхода мультиплексора 5 логических условий в режиме ожидания постоянно поступает на третий информационный вход мультиплексора 4. Сигнал диагностики с выхода элемента И 18 поступает также через третий элемент ИЛИ 15 на синхровход регистра 2 адреса. По заднему фронту этого сигнала на синхро- входе регистра 2 адреса происходит запись адреса диагностической микрокоманды с выхода мультиплексора 4 адреса в регистр 2. По этому адресу из блока 1 считывается диэгностичес8

кая микрокоманда, в полях 1.1, 1.2 и 1.3 которой записаны единичные коды, а в поле 1.4 - адрес нулевой ячейки блока 1 (т.е. нулевой адрес). Коммутатор 8 контроля снова начинает контролировать правильность кодов, считываемых с выходов 1.1, 1.2 и 1.3. В случае появления на контролируемых выходах блока 1 хотя бы одного нуля, коммутатор 8 формирует сигнал ошибки, который записывается в триггер 12 ошибки, блокирует за-, пуск неисправного устройства и поступает на его выход 23 ошибки. По поступлению в шину 24 следующего сигнала диагностики происходит переход к нулевому адресу.

Формула изобретения

Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистры адреса и микроопераций, мультиплексоры адреса и 25 логических условий, триггер пуска, генератор тактовых импульсов, триггер ошибки, первый элемент ИЛИ, первый элемент И, причем прямой выход триггера пуска соединен с входом заИ 18 будет единичный сиг- 30 держки генератора тактовых импульсов,

первый выход которого соединен с входом синхронизации регистра микроопераций, вход кода операции устройства соединен с первым информационным входом мультиплексора адреса, выход поля старших разрядов адреса блока памяти микрокоманд и выход мультиплексора логических условий соединены соответственно со старшими и младшими разрядами второго информационного входа мультиплексора адреса, выход которого соединен с информационным входом регистра адреса, выход регистра адреса соединен с входом блока памяти микрокоманд, выходы поля микроопераций и поля кода логических условий которого соединены соответственно с информационным входом регистра микроопераций и адресным входом мультиплексора логических условий, вход логических условий устройства и выход младшего разряда поля адреса блока памяти микрокоманд соединены с информационным входом мультиплексора логических условий, выход регистра микроопераций соединен с выходом микроопераций устройства, выход триггера ошибки соединен с выходом ошибки устройства и первым

35

40

45

50

55

o

465

8

кая микрокоманда, в полях 1.1, 1.2 и 1.3 которой записаны единичные коды, а в поле 1.4 - адрес нулевой ячейки блока 1 (т.е. нулевой адрес). Коммутатор 8 контроля снова начинает контролировать правильность кодов, считываемых с выходов 1.1, 1.2 и 1.3. В случае появления на контролируемых выходах блока 1 хотя бы одного нуля, коммутатор 8 формирует сигнал ошибки, который записывается в триггер 12 ошибки, блокирует за-, пуск неисправного устройства и поступает на его выход 23 ошибки. По поступлению в шину 24 следующего сигнала диагностики происходит переход к нулевому адресу.

входом первого элемента ИЛИ, выход разряда микроопераций Конец работы регистра микроопераций соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом установки в О триггера пуска, о т- личающееся тем, что, с целью увеличения глубины контроля, оно содержит первый и второй дешифраторы, триггер, второй, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ, элемент И-НЕ, второй и третий элементы И, элемент задержки первый и второй ключи с тристабиль- ным выходом, причем выходы поля режима работы поля кода микроопераций и поля кода логических условий блока памяти микрокоманд объединены и соединены с входом шестого элемента И и элемента И-НЕ, выходы поля режима работы и поля кода логических условий блока памяти микрокоманд соединены соответственно с информационными входами первого и второго дешифраторов, выход поля микрооперации блока памяти микрокоманд соединен с информационным входом блока ключей с три- стабильным выходом, выход которого соединен с третьим информационным входом мультиплексора адреса и с информационным входом-выходом устройства, первый вход пуска устройства соединен с первым входом четвертого элемента ИЛИ, с второго по k-й входы пуска устройства соединены с (k-1) входами пятого элемента ИЛИ, выход которого соединен с управляющим входом блока ключей с тристабильным входом, с первым входом второго и с вторым входом четвертого элемента ИЛИ и с первым управляющим входом мультиплексора адреса, выход четвертого элемента ИЛИ соединен с входом установки в 1 триггера пуска, первый выход первого дешифратора соединен с вторым управляющим входом мультиплексора адреса и вторым входом второго элемента ИЛИ, выход которого соединен с информационным входом триггера, второй выход генератора тактовых импульсов соединен с первым входом третьего элемента ИЛИ и входом синхронизации триггера, выход которого соединен с первым входом второго элемента И, инверсный выход триггера пуска соединен с первым входом третьеj- го элемента И и с первым входом первого элемента И, выход которого соединен с входом элемента задержки, третьим управляющим входом мультиплексора адреса и вторым входом третьего

o элемента ИЛИ, выход которого соединен с входом синхронизации регистра адреса, второй выход первого депифрато- ра соединен с информационным и управляющим входами первого ключа с три5 стабильным входом, выход которого соединен с вторым входом первого элемента И и с первым двунаправленным входом-выходом режима работы устройства, выход второго ключа с тристабнльным

0 выходом соединен с вторым входом второго элемента И, с вторым разрядом информационного входа мультиплексора логических условий и с вторым двунаправленным входом-выходом режима рабо5 ты устройства, первый выход генератора тактовых импульсов соединен с третьим входом второго элемента И, выход которого соединен с первым входом седьмого элемента ИЛИ, третий

0 выход первого дешифратора соединен

с информационным и управляющим входами второго ключа с тристабильным входом, выход седьмого элемента ИЛИ и выход разряда микрооперации проверки

- работоспособности регистра микроопе раций соединены соответственно с входами установки 1 и в О триггера ошибки, четвертый выход первого дешифратора соединен информационным

0 входом регистра микроопераций, пятый выход первого дешифратора соединен с входом запрета записи регистра микроопераций и стробирующим входом мультиплексора логических условий,

5 со стробирующим входом второго дешифратора, выход которого соединен с информационным выходом устройства, выходы элемента И-НЕ, шестого элемента ИЛИ и элемента задержки соединены соответственно с вторым, третьим и

0

четвертым входами третьего элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ.

А 9 69 I

фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1365082A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1280629A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1376084A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1649539A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке ЭВМ и вычислительных и управляющих систем. Целью изобретения является увеличение глубины контроля устройства. Микропрограммное устройство управления содержит блок памяти микрокоманд с полями признака работы, кода микроопераций, кода логических условий и адреса, регистры адреса и микроопераций, мультиплексоры адреса и логических условий, первый и второй дешифраторы, триггер, триггер пуска, генератор тактовых импульсов, триггер ошибки, с первого по седьмой элементы ИЛИ, с первого по третий элементы И, первый и второй ключи с тристабильным выходом, блок ключей с тристабильным выходом, элемент И-НЕ, элемент задержки. В устройстве реализован режим диагностики в отключенном состоянии (триггер пуска в нулевом состоянии), что позволяет увеличить глубину контроля. 2 ил.

36

8

5J

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Авторское свидетельство СССР № 1110121, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-30—Публикация

1986-12-26—Подача