Ъ(пТ/т) -(пТ/т)

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный приемник сигналов данных | 1989 |

|

SU1672580A1 |

| Устройство преобразования сигналов для передачи данных по первичному сетевому тракту | 1989 |

|

SU1739503A1 |

| Устройство адаптивной коррекции межсимвольных искажений | 1987 |

|

SU1540010A1 |

| Адаптивное устройство для дуплексной передачи данных | 1989 |

|

SU1635269A1 |

| РАДИОМОДЕМ | 2010 |

|

RU2460215C1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ПОМОЩЬЮ ШУМОПОДОБНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2007 |

|

RU2362273C2 |

| ДВУХПРОВОДНАЯ ДУПЛЕКСНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ | 1991 |

|

RU2037966C1 |

| Автокорреляционный демодулятор псевдослучайных сигналов с относительной фазовой модуляцией второго порядка | 2017 |

|

RU2660594C1 |

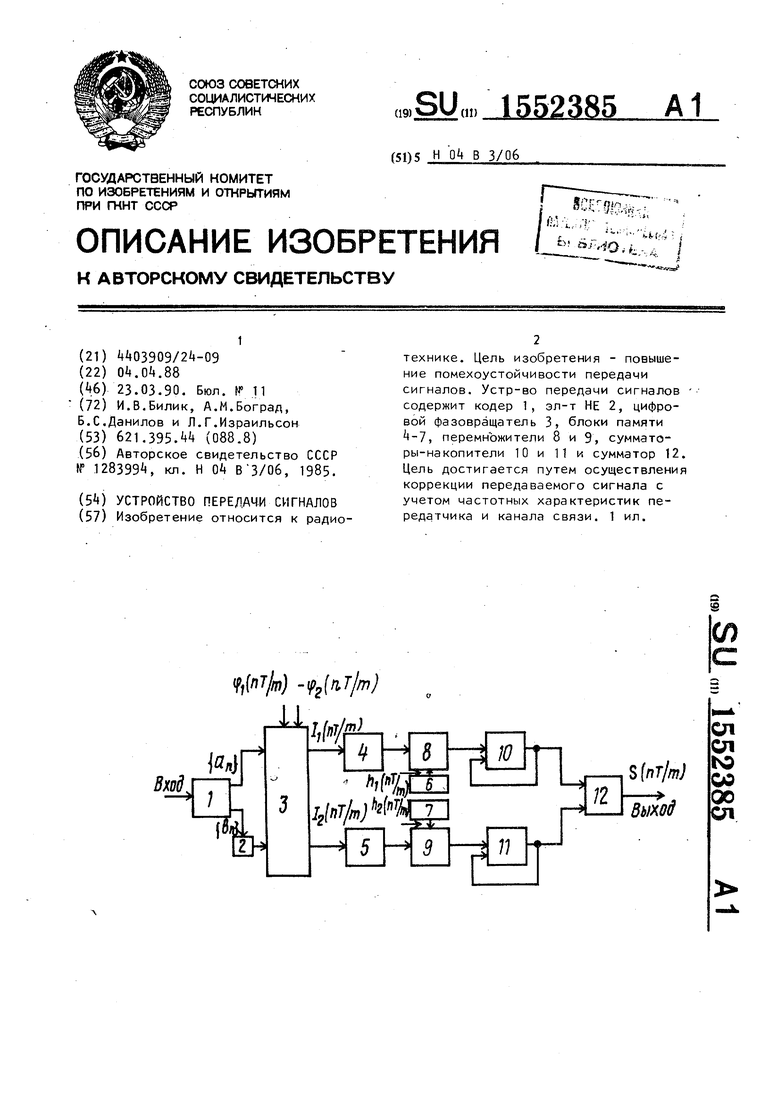

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости передачи сигналов. Устройство передачи сигналов содержит кодер 1, эл-т НЕ 2, цифровой фазовращатель 3, блоки памяти 4 - 7, перемножители 8 и 9, сумматоры-накопители 10 и 11 и сумматор 12. Цель достигается путем осуществления коррекции передаваемого сигнала с учетом частотных характеристик передатчика и канала связи. 1 ил.

S(nT/m) ВЫХ00

Изобретение относится к радиотехнике и связи и может быть использовано при формировании сигналов, передаваемых посредством многопозиционных методов модуляции.

Цель изобретения - повышение помехоустойчивости передачи сигналов путем коррекции передаваемого сигнала учетом частотных характеристик передатчика и канала связи.

На чертеже представлена структурная электрическая схема устройства передачи сигналов.

Устройство содержит кодер 1, элемент НЕ 2, цифровой фазовращатель 3, первый, второй, третий и четверты блоки k-7 памяти, первый и второй перемножители 8 и 9, первый и второй сумматоры-накопители 10 и 11 и сумматор 1 2.

Устройство работает следующим образом.

Отсчеты элементов информационных последовательностей Јa(nT/m,)|j, b(nT/m)T| с выходов кодера 1 поступают на цифровой фазовращатель 2, где Т - длительность единичного элемента модулированного сигнала; m - коэффициент интерполяции, отображающий число отсчетов; аппроксимирующих единичный элемент модулированного сигнала; п - порядковый номер передаваемого элемента сигнала. При этом информационная последовательность с второго выхода кодера 1 инвертируется элементом НЕ 2. В цифровом фазовращателе 3 отсчеты элементов информационных последовательностей а(пТ/п , ь(пТ/тЯ умножаются, на отсчеты элементов ортогональных колебаний Lp,(nT/n;, ерг(пТ/т; и затем записываются в первый и второй блоки k и 5 памяти. Сигналы T,(nT/mJ и I CnT/m,) на первом и втором выходах цифрового фазовращателя 3 формируются по правилу

I, (пТ:/т)а(пТ:/т) q, (пТ/тп;- -b(nT/m; Цг (nT/mj;

I2(nT/n; a(nT/m;Cf2 (nT/mj+

+b(nT/m) Cpi (nT/т) .

Посредством первого и второго перемножителей 8 и 9 и первого и второго сумматоров-накопителей 10 и 11 осуществляется свертка соответствующих последовательностей, поступаю

0

0

щих с выходов первого и второго блоков 4 и 5 памяти с последовательностями сигналов h,(nT/m;l|, h2(nT/rpj l, отображающих импульсные характеристики корректирующего четырехполюсника, частотная характеристика которого обратна эквивалентной частотной характеристике фильтрового оборудования передатчика и усредненной характеристике используемого канала, записанных в третьем и четвертом блоках 6 и 7 памяти.

Путем изменения импульсных харак- теристик h,(nT/m;, h Cnl/m) , записанных в третьем и четвертом блоках 6 и 7 памяти, компенсируются искажения, вносимые различным числом переприемов или транзитов используемого канала связи. Сигналы с выходов первого и второго сумматоров-накопителей 10 и 11 объединяются сумматором 12. Таким образом, сигнал на выходе сумматора 12 S(nT/m, определяется следующим образом:

5

40

30

S(nT/mj 5Lh,(kT/m;It(n-k;T/m + + Zl hг (kT/mU2 (n-kГГ/nt .

Формула

зобретения

0

5

5

0

5

Устройство передачи сигналов, содержащее кодер, первый, второй и третий блоки памяти, первый перемножитель, к первому входу которого подключен выход третьего блока памяти, а также сумматор и первый сумматор-накопитель, отличающееся тем, что, с целью повышения помехоустойчивости передачи сигналов путем его коррекции с учетом частотных характеристик передатчика и канала связи, введены элемент НЕ, второй перемножитель, четвертый блок памяти,, цифровой фазовращатель и второй сумматор-накопитель, выход которого подключен к входу сумматора, к другому входу которого подключен выход первого сумматора-накопителя, причем первый выход кодера соединен с первым входом цифрового фазовращателя, второй вход которого соединен с вторым выходом кодера через элемент НЕ, а первый и второй выходы цифрового фазовращателя через соответствующие последовательно соединенные первый и второй

515523856

блоки памяти и первый и второй перем- накопителей, при этом выход четверто- ножители подключены к входам соответ- го блока памяти подключен к другому ственно первого и второго сумматоров- входу второго перемножителя.

| Устройство для передачи сигналов данных | 1985 |

|

SU1283994A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-03-23—Публикация

1988-04-04—Подача