1

(21)4422057/24-09

(22)10.05.88

(46) 23.03.90. Бюл. № 11

(72) С.В.Васильев, С.А.Доронин,

J1.H.Дубовик иЛ.П.Котенко

(53)621.396.6(088.8)

(56)Хохлов Б.И. Декодирующие устройства цветных телевизоров. - М.: Радио и связь, 1987, с. 96, рис. 255.

(54)УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ЦИФРОВЫХ СИГНАЛОВ С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ

(57)Изобретение относится к радиотехнике. Цель изобретения - повышение

точности демодуляции. Устр-во содержит регистры 3 и 4 сдвига, блок 8 умножения на два, сумматор 9, блок 16 деления и декодирующий блок 17. Цель достигается введением управляемого ключа 1, АЦП 2, регистров 5 и 6 сдвига, генератора 7 импульсов,сумматора 10, блока 11 умножения на два, блоков 12 и 13 запрета, блока 14 определения модуля числа и цифрового компаратора 15, с помощью которых исключаются из дальнейшей обработки аномальные результаты демодуляции, возникающие при малых значениях суммы кодов, находящихся в регистрах 4 и 5. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР | 1991 |

|

RU2017340C1 |

| Устройство для измерения частоты гармонического сигнала | 1991 |

|

SU1809394A1 |

| Цифровой частотный детектор | 1990 |

|

SU1714530A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1524011A1 |

| Устройство для измерения частоты гармонического сигнала | 1988 |

|

SU1762254A1 |

| Устройство для измерения частоты гармонического сигнала | 1988 |

|

SU1705755A1 |

| СПОСОБ НАВИГАЦИИ ДЛЯ ПРИНТЕРА, ПРИНТЕР И МАЯК | 2020 |

|

RU2758714C2 |

| Стабилизатор постоянного напряжения | 1986 |

|

SU1379779A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1596270A2 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1758875A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение точности демодуляции. Устройство содержит регистры 3 и 4 сдвига, блок 8 умножения на два, сумматор 9, блок деления 16 и декодирующий блок 17. Цель достигается введением управляемого ключа 1, АЦП 2, регистров 5 и 6 сдвига, генератор 7 импульсов, сумматора 10, блока 11 умножения на два, блоков запрета 12 и 13, блока 14 определения модуля числа и цифрового компаратора 15, с помощью которых исключаются из дальнейшей обработки аномальные результаты демодуляции, возникающие при малых значениях суммы кодов, находящихся в регистрах 4 и 5. 1 ил.

ел ел to

со со 1

Изобретение относится к радиотехнике и может быть использовано в приемниках дискретной информации.

Цель изобретения -повышение точное ти демодуляции.

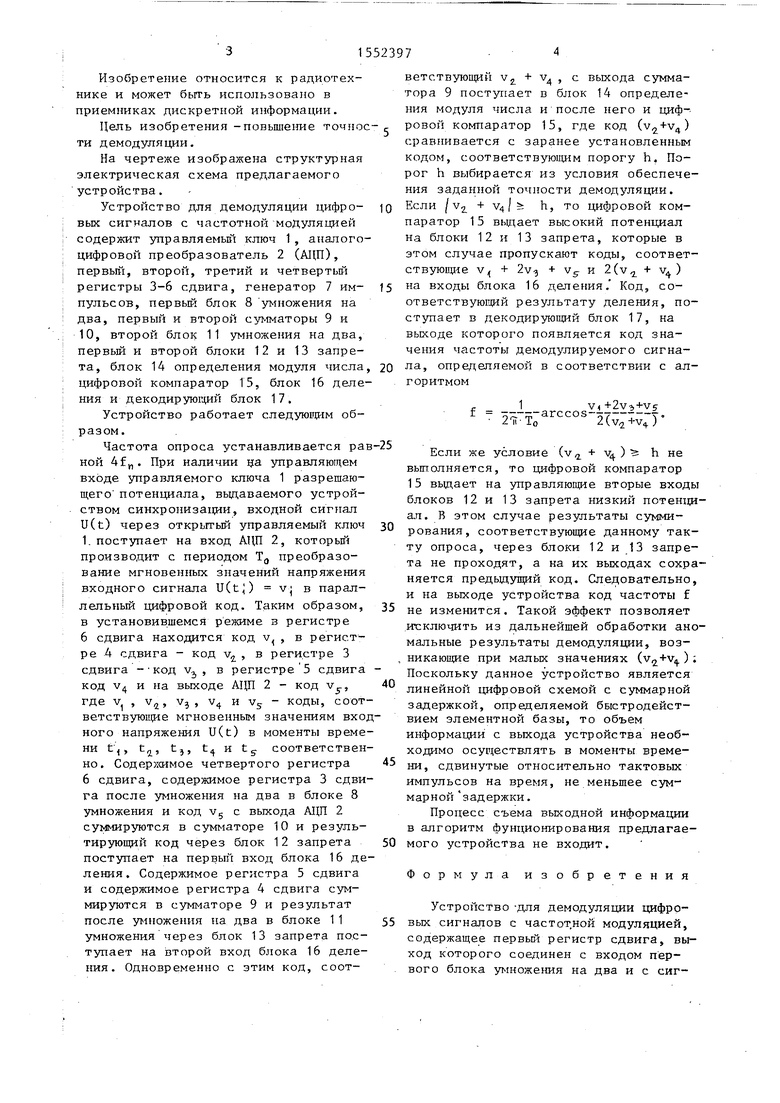

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для демодуляции цифро- вых сигналов с частотной модуляцией содержит управляемый ключ 1, аналого- цифровой преобразователь 2 (АЦП), первый, второй, третий и четвертый регистры 3-6 сдвига, генератор 7 им- пульсов, первый блок 8 умножения на два, первый и второй сумматоры 9 и 10, второй блок 11 умножения на два, первый и второй блоки 12 и 13 запрета, блок 14 определения модуля числа, цифровой компаратор 15, блок 16 деления и декодирующий блок 17.

Устройство работает следуюпим образом.

Частота опроса устанавливается рав ной AfM. При наличии на управляющем входе управляемого ключа 1 разрешающего потенциала, выдаваемого устройством синхронизации, входной сигнал U(t) через открытый управляемый ключ 1 поступает на вход АЦП 2, который производит с периодом Т0 преобразование мгновенных значений напряжения входного сигнала U(t;) v; в параллельный цифровой код. Таким образом, в установившемся режиме в регистре 6 сдвига находится код v , в регистре 4 сдвига - код v, в регистре 3 сдвига - код V.J , в регистре 5 сдвига код v4 и на выходе АЦП 2 - код v5,

где v , v4, v}, v4 и vs - коды, соответствующие мгновенным значениям входного напряжения U(t) в моменты времени t, ta, t}, t и ts соответственно. Содержимое четвертого регистра 6 сдвига, содержимое регистра 3 сдвига после умножения на два в блоке 8 умножения и код v5 с выхода АЦП 2 cyi-мируются в сумматоре 10 и результирующий код через блок 12 запрета поступает на первый вход блока 16 деления. Содержимое регистра 5 сдвига и содержимое регистра 4 сдвига суммируются в сумматоре 9 и результат после умножения на два в блоке 11

умножения через блок 13 запрета поступает на второй вход блока 16 деления. Одновременно с этим код, соответствующий vг + v4 , с выхода сумматора 9 поступает в блок 14 определения модуля числа и после него и цифровой компаратор 15, где код () сравнивается с заранее установленным кодом, соответствующим порогу h. Порог h выбирается из условия обеспечения заданной точности демодуляции. Кслн | vz + уц | h, то цифровой компаратор 15 выдает высокий потенциал на блоки 12 и 13 запрета, которые в этом случае пропускают коды, соответствующие v,, + 2v + v9 и 2(va + v) на входы блока 16 деления. Код, соответствующий результату деления, поступает в декодирующий блок 17, на выходе которого появляется код значения частоты демодулируемого сигнала, определяемой в соответствии с алгоритмом

г1Vt +2V-J+V5

f --п;-arc cos--7---т. i и Г0Av/2 +v4 )

Если же условие (v + v4 ) h не выполняется, то цифровой компаратор 15 выдает на управляющие вторые входы блоков 12 и 13 запрета низкий потенциал. В этом случае результаты суммирования, соответствующие данному такту опроса, через блоки 12 и 13 запрета не проходят, а на их выходах сохраняется предыдущий код. Следовательно, и на выходе устройства код частоты f не изменится. Такой эффект позволяет исключить из дальнейшей обработки аномальные результаты демодуляции, возникающие при малых значениях (). Поскольку данное устройство является линейной цифровой схемой с суммарной задержкой, определяемой быстродействием элементной базы, то объем информации с выхода устройства необходимо осуществлять в моменты времени, сдвинутые относительно тактовых импульсов на время, не меньшее суммарной задержки.

Процесс съема выходной информации в алгоритм фунционирования предлагаемого устройства не входит.

Формула изобретения

Устройство для демодуляции цифровых сигналов с частотной модуляцией, содержащее первый регистр сдвига, выход которого соединен с входом первого блока умножеагия на два и с сигнальным входом второго регистра сдвига, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к первому входу первого регистра сдвига, блок деления, выход которого подключен к входу декодирующего блока, отличающееся тем, что, с целью повышения точности демодуляции, введены два блока запрета, цифровой компаратор, блок определения модуля числа, второй блок умножения на два, второй сумматор, третий и четвертый регистры

сдвига, аналоге-цифровой преобраэова- 15 первый вход которого соединен с выхотель,генератор импульсов и управляемый ключ, выход которого соединен с первым входом аналого-цифрового преобразователя, выход которого соединен с первым входом третьего регистра сдвига и с первым входом второго сумматора, второй вход которого подключен к выходу первого блока умножения на два, выход третьего регистра сдвига соединен с первым входом первого регистра сдвига, второй вход которого соединен с выходом генератора импуль сов, с вторым входом аналого-цифрового преобразователя, с вторым входом третьего регистра сдвига, с вторым вхо-

дом четвертого регистра сдвига и с вторым входом второго регистра сдвига, выход которого подключен к первому входу четвертого регистра сдвига, выход которого подключен к первому входу четвертого регистра сдвига, выход которого подключен к третьему входу второго сумматора, выход которого соединен с первым входом первого блока запрета, выход которого подключен к первому входу блока деления, второй вход которого подключен к выходу второго блока запрета,

дом второго блока умножения на два вход которого подключен к выходу первого сумматора и к входу блока определения модуля числа, выход которого соединен с входом цифрового компаратора, выход которого соединен с вторыми входами первого и второго блоков запрета, при этом первый вход управляемого ключа является информа- ционным входом устройства, синхронизирующим входом которого является второй вход управляемого ключа, а выход декодирующего блока является выходом устройства.

Авторы

Даты

1990-03-23—Публикация

1988-05-10—Подача