Изобретение относится к радиотехнике.

Целью изобретения является повышение точности и обеспечение возможности детектирования сигнала с постоянной составляющей.

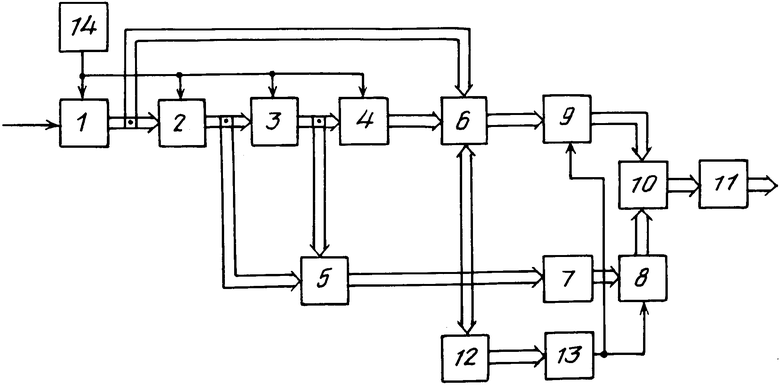

На чертеже изображена структурная электрическая схема предложенного цифрового частотного детектора.

Цифровой частотный детектор содержит аналого-цифровой преобразователь (АЦП) 1, первый, второй, третий регистры 2 3, 4 сдвига, первый, второй сумматоры 5, 6, умножитель 7 на два, первый, второй блоки 8, 9 запрета, блок 10 деления, декодирующий блок 11, блок 12 определения модуля числа, цифровой компаратор 13, генератор 14 импульсов.

Цифровой частотный детектор работает следующим образом.

Принимаемый сигнал S(t) поступает на информационный вход АЦП 1, который с периодом То = 1/fо производит преобразование мгновенных значений напряжения этого сигнала S(ti) = Si в параллельный цифровой код. Этот код последовательно заполняет регистры 2, 3, 4 сдвига. Таким образом, в установившемся режиме в регистре 4 сдвига находится код S1, в регистре 3 сдвига - код S2, в регистре 2 сдвига - код S3, на выходе АЦП 1 - код S4, где S1, S2, S3 и S4 - мгновенные значения напряжения входного в моменты времени t1, t2, t3 и t4 соответственно. Содержимое регистра 2 сдвига S3 поступает на первый вход сумматора 5, на второй вход которого (инверсный) с выхода регистра 3 сдвига поступает код S2. В результате на выходе сумматора 5 появляется код (S3 - S2), который после умножения на два в умножителе 7 поступает на информационный вход блока 8 запрета. Одновременно с этим код (S3-S2) поступает на вход блока 12 определения модуля числа и третий (инверсный) вход сумматора 6, на первый (инверсный) вход которого с выхода регистра 4 сдвига подается код S1, на второй вход с выхода АЦП 1 поступает код S4. В результате на выходе сумматора 6 образуется код (S4 + S2 - S3 - S1), который подается на информационный вход блока 9 запрета. Блок 12 определения модуля числа определяет модуль (S3 - S2), который поступает в цифровой компаратор 13, где код  S3 - S

S3 - S сравнивается с кодом, соответствующим порогу h. Если

сравнивается с кодом, соответствующим порогу h. Если  S3 - S2

S3 - S2 ≥ h, то цифровой компаратор 13 имеет высокий потенциал на управляющие входы блоков 8, 9 запрета, которые в этом случае пропускают коды, соответствующие 2(S3-S2) и (S4 + S2 - S3 - S1), на первый и второй входы блока 10 деления. Код, соответствующий результату деления

≥ h, то цифровой компаратор 13 имеет высокий потенциал на управляющие входы блоков 8, 9 запрета, которые в этом случае пропускают коды, соответствующие 2(S3-S2) и (S4 + S2 - S3 - S1), на первый и второй входы блока 10 деления. Код, соответствующий результату деления , поступает на декодирующий блок 11, на выходе которого появляется код значения частоты детектируемого сигнала, определяемого в соответствии с выражением

, поступает на декодирующий блок 11, на выходе которого появляется код значения частоты детектируемого сигнала, определяемого в соответствии с выражением =

=  arccos

arccos  .

.

Если же условие  S3 - S2

S3 - S2 ≥ h не выполняется, то цифровой компаратор 13 выдает на управляющие входы блоков 8 и 9 запрета низкий потенциал. В этом случае результаты суммирования, соответствующие данному такту опроса, через блоки 8 и 9 запрета не проходят, а на их выходах сохраняются коды предыдущего такта опроса. Следовательно, на выходе детектора код частоты

≥ h не выполняется, то цифровой компаратор 13 выдает на управляющие входы блоков 8 и 9 запрета низкий потенциал. В этом случае результаты суммирования, соответствующие данному такту опроса, через блоки 8 и 9 запрета не проходят, а на их выходах сохраняются коды предыдущего такта опроса. Следовательно, на выходе детектора код частоты  не изменится. Такой порядок работы детектора позволяет исключить из дальнейшей обработки аномальные результаты детектирования, возникающие при малых значениях (S3 - S2). В следующем такте опроса описанный выше порядок работы устройства повторяется и, если (S4 - S3) ≥ h, то оценка частоты вычисляется по формуле:

не изменится. Такой порядок работы детектора позволяет исключить из дальнейшей обработки аномальные результаты детектирования, возникающие при малых значениях (S3 - S2). В следующем такте опроса описанный выше порядок работы устройства повторяется и, если (S4 - S3) ≥ h, то оценка частоты вычисляется по формуле:

arccos

arccos .

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для демодуляции цифровых сигналов с частотной модуляцией | 1988 |

|

SU1552397A1 |

| Устройство для измерения частоты гармонического сигнала | 1988 |

|

SU1762254A1 |

| Цифровой частотный детектор | 1990 |

|

SU1714530A1 |

| Цифровой фазовый детектор | 2018 |

|

RU2723445C2 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2022 |

|

RU2786159C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1524011A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ С МИНИМАЛЬНОЙ УГЛОВОЙ МОДУЛЯЦИЕЙ | 2007 |

|

RU2358405C1 |

| Устройство для измерения частоты гармонического сигнала | 1991 |

|

SU1809394A1 |

| ЦИФРОВОЙ НЕКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННЫХ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2649782C1 |

Цифровой частотный детектор содержит аналого - цифровой преобразователь 1, регистры сдвига 2,3,4, сумматоры 5,6, умножитель на два 7, блоки запрета 8,9, блок деления 10, декодирующий блок 11, блок определения модуля числа 12, цифровой компаратор 13, генератор импульсов 14 1-2-3-4-6-9-10-11, 2-5-7-8-10, 14-1, 14-2, 14-3, 14-4, 3-5-6, 5-12-13-8, 1-6. 1 ил.

ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР, содержащий последовательно соединенные аналого-цифровой преобразователь и первый регистр сдвига, выход которого соединен с первым входом первого сумматора, выход которого через последовательно соединенные умножитель на два, первый блок запрета и блок деления подключен к входу декодирующего блока, выход которого является выходом цифрового частотного детектора, выход второго регистра сдвига соединен с входом третьего регистра сдвига, выход которого подключен к первому входу второго сумматора, второй вход которого соединен с выходом аналого-цифрового переобразователя, а выход подключен к информационному входу второго блока запрета, выход которого соединен с вторым входом блока деления, управляющий вход, соединенный с управляющим входом первого блока запрета, подключен к выходу цифрового компаратора, вход которого соединен с выходом блока определения модуля числа, вход которого подключен к выходу первого сумматора, второй вход которого соединен с выходом второго регистра сдвига, причем выход генератора импульсов подключен к тактовым входам первого, второго и третьего регистров сдвига и аналого-цифрового преобразователя, информационный вход которого является входом цифрового частотного детектора, отличающийся тем, что, с целью повышения точности и обеспечения возможности детектирования сигнала с постоянной составляющей, выход первого регистра сдвига соединен с информационным входом второго регистра сдвига, а выход первого сумматора подключен к третьему входу второго сумматора.

| Устройство для демодуляции цифровых сигналов с частотной модуляцией | 1988 |

|

SU1552397A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-07-30—Публикация

1991-05-12—Подача