Изобретение относится к измерительной технике и предназначено для измерения частоты гармонического сигнала за время, меньшее периода измеряемого сигнала,и является усовершенствованием известного устройства.

Цель изобретения - повышение точности и достоверности измерений.

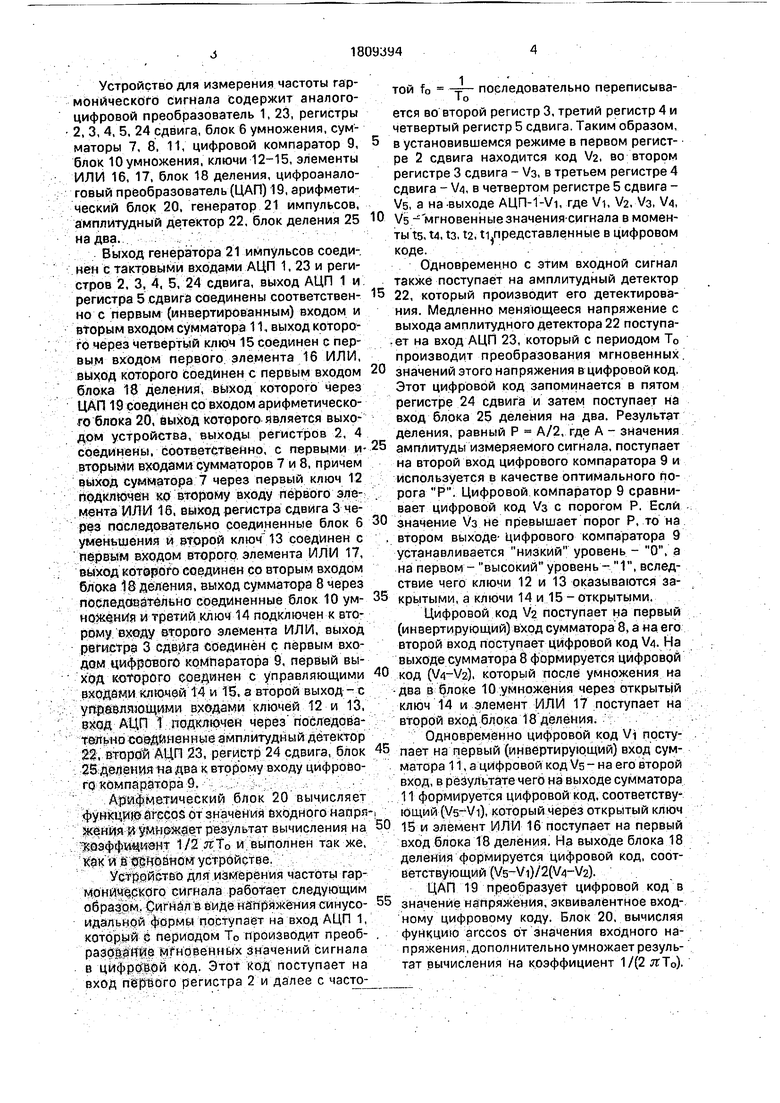

На фиг. 2 представлены эпюры входного сигнала устройства и обозначен оптимальный порог, выбранный из условия

Р 0,5 А,

0)

где А - амплитуда входного сигнала. При вычисление частоты производится по формуле

f -2 T7arccos 2 (V-VV2 ) (2)

при I Уз I Р - по формуле

1

2тгТ0

arccos

V4 +У2 2 V3

(3)

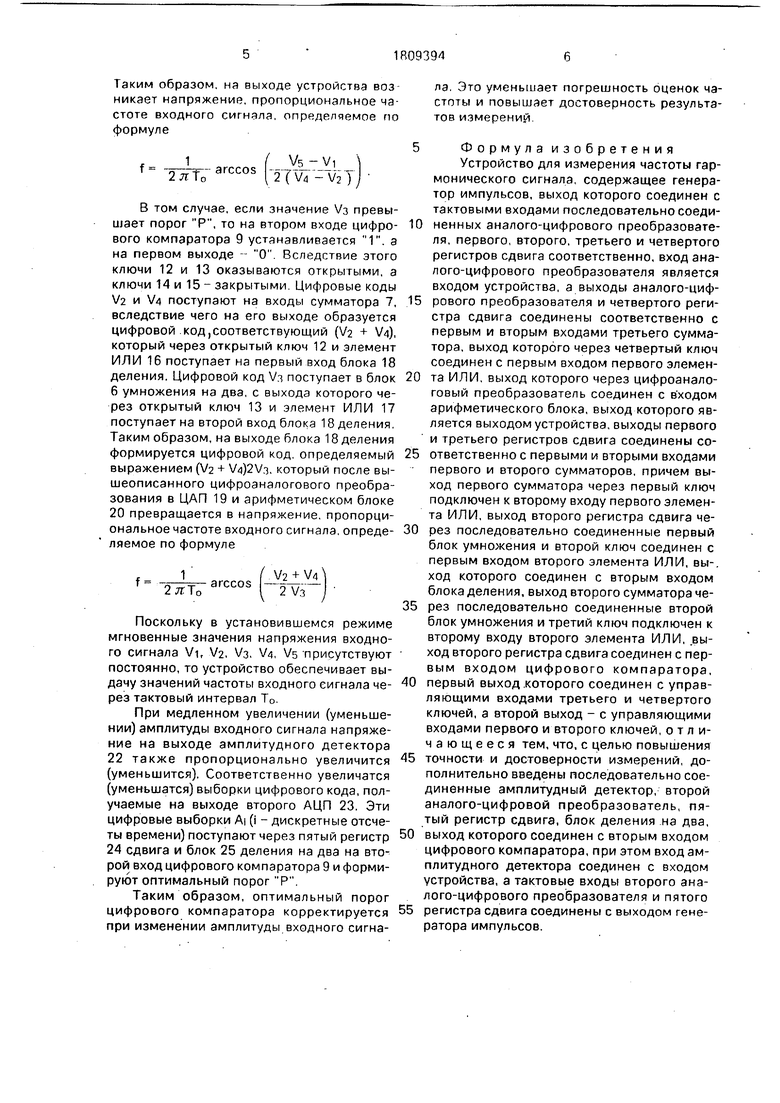

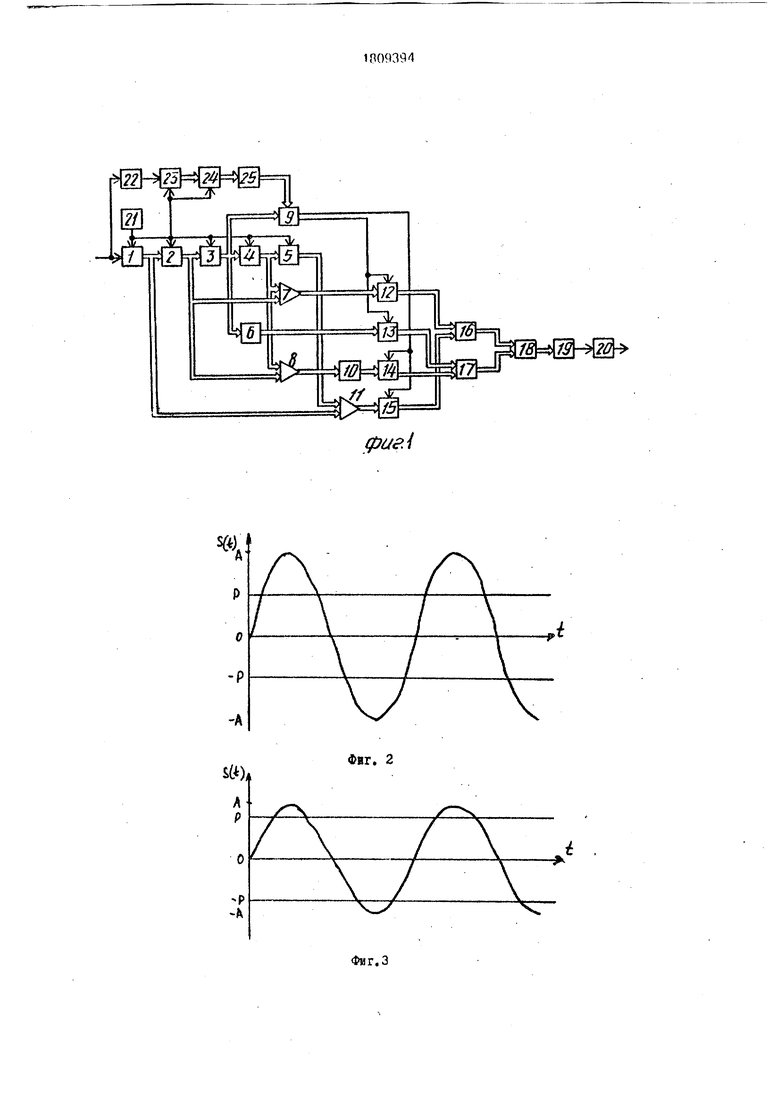

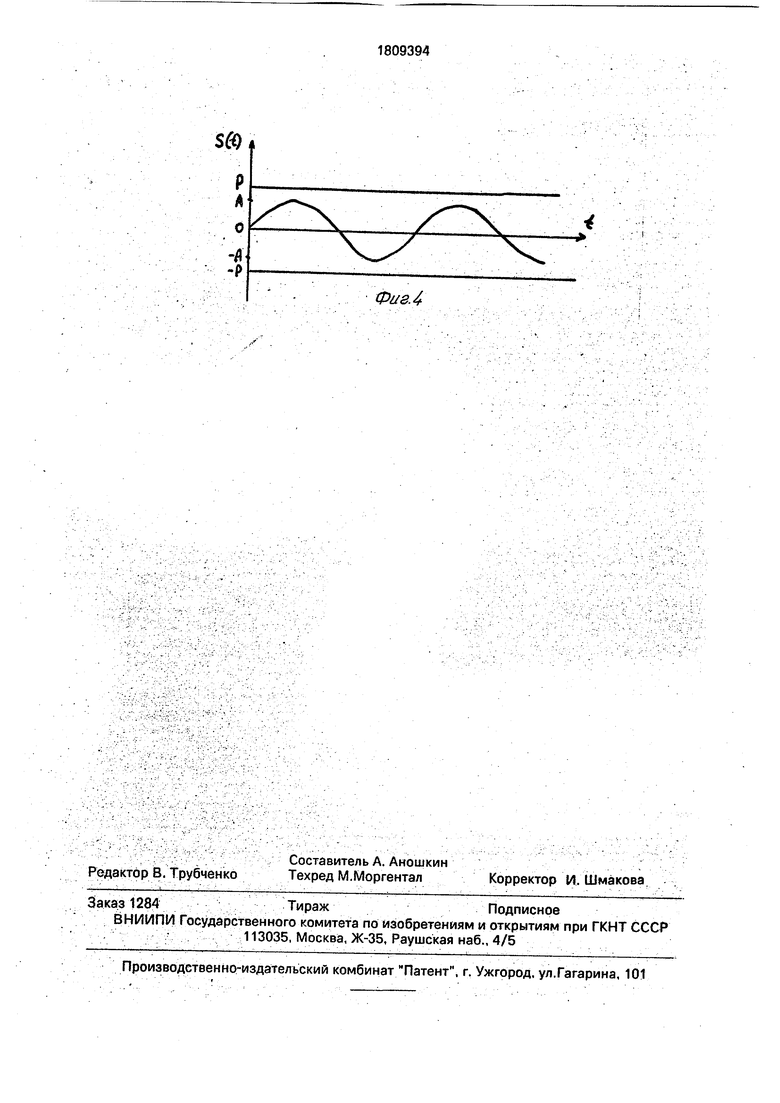

Представим теперь, что амплитуда входного сигнала изменяется, например уменьшается. При неизменном пороге (см. фиг. 3) вычисления по формуле (2) будут производиться чаще, при этом погрешность этих вычислений увеличится за счет нарушения условия (1). Если амплитуда еще уменьшится, то любая выборка независимо от ее фазы всегда будет находиться в подпорого- вой области (см. фиг. 4).,всегда будет выполняться условие I Уз Р и вычисления будут производиться только по формуле (2). В этом случае при IУз - А в работе устройства будут поступать сбои. Для исключения этих сбоев (см. фиг. 4) и уменьшения погрешности измерения частоты при относительно небольших изменениях амплитуды входного сигнала (см. фиг. 3) предлагается при помощи введенной цепи всегда поддерживать соотношение между амплитудой и порогом в соответствии с выражением (1).

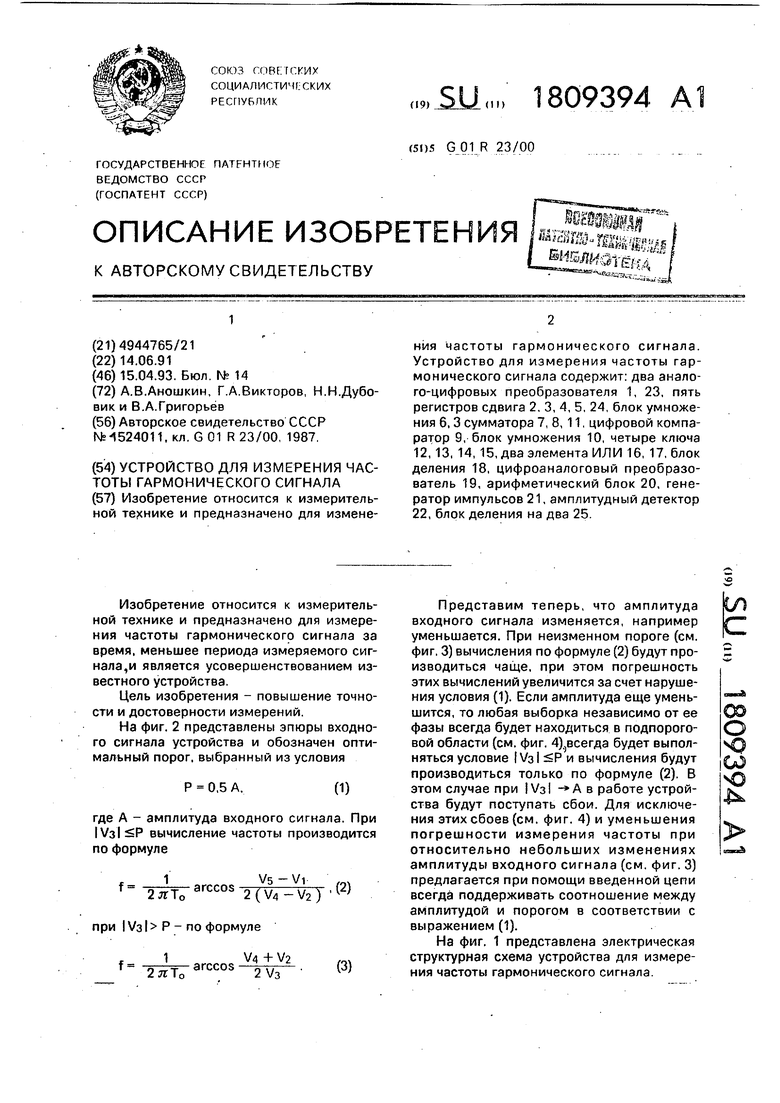

На фиг. 1 представлена электрическая структурная схема устройства для измерения частоты гармонического сигнала.

т

С

О

Устройство для измерения частоты гаронического сигнала содержит аналого- ифровой преобразователь 1, 23, регистры , 3, 4, 5, 24 сдвига, блок 6 умножения, суматоры 7, 8. 11, цифровой компаратор 9, 5 блок 10 умножения, ключи 12-15, элементы ЛИ 16, 17, блок 18 деления, цифроанало- говый преобразователь (ЦАП) 19, арифметиеский блок 20, генератор 21 импульсов, амплитудный детектор 22, блок деления 25 Ю на два.:.. -.- : : .,- .. .. : :. .

Выход генератора 21 импульсов соединен с тактовыми входами АЦП 1,23 и регитров 2. 3, 4, 5, 24 сдвига, выход АЦП 1 и регистра 5 сдвига соединены соответствен- 15 но с первым (инвертированным) входом и вторым входом сумматора 11, выход которого через четвёртый ключ 15 соединен с первым входом первого элемента 16 ИЛИ, выход которого соединен с первым входом 20 блока 18 деления, выход которого через ЦАП 19 соединен со входом арифметическоо блока 20, выход которого является выходом устройства, выходы регистров 2, 4 соединены, соответственно, с первыми и- 25 вторыми входами сумматоров 7 и 8, причем выход сумматора 7 через первый ключ 12 прдклфчен ко второму входу первого элемента ИШ 16, выход регистра сдвига 3 через последовательно соединенные блок 6 30 уменьшения и второй ключ 13 соединен с П08ЫМ входом второго, элемента ИЛИ 17, вьжод которого соединен со вторым входом блока 18 деления, выход сумматора 8 через последабйтёльно соединенные блок 10 ум- 35 и третий .ключ 14 подключен к второму входу второго элемента ИЛИ, выход регистра 3 сдвига соединён с первым входомцифрового компаратора 9, первый выход которого соединен с управляющими 40 входами ключей 1:4 и 15, а второй выход -с у равлшощдай входами ключей 12 и 13, дад АЦП 1 подкшчен через последовательно соединенные амплитудный детектор 2%, второй АЦП .23, регистр 24 сдвига, блок 45 2&деленмя на два к второму входу цифрового: коша атораЗ, -;.,,.::- -;-.;V--/: ,-. - I ...- : Аш метический блок 20 вычисляет .. уиЦцщ От значения входного напря-, Н ёН:ияWу/МН@:щет результат вычисления на 50 0эффвдиЈИт 1/2.яТо и/выполнен так же, Э1 в :ШЧйаномустройстве, V.: :

УстйайбтвО Для измерения частоты гар- MOHW«WKOrP сигнала работает следующим образам, fenf нал в виде на п1рйжёния сйнусо- 55 идальвой ррмы поступает на вход АЦП 1, который si периодом Т0 производит преоб- . разо|Щй Wновёйнбгх значений сигнала в цйфреШой код. Этот код поступает на вход первого регистра 2 и далее с частотой f0

1

То

последовательно переписывается во второй регистр 3, третий регистр 4 и четвертый регистр 5 сдвига. Таким образом, в установившемся режиме в первом регистре 2 сдвига находится код Va, во втором регистре 3 сдвига - /з, в третьем регистре 4 сдвига - /4, в четвертом регистре 5 сдвига - УБ, а на -выходе АЦП-1-Vi, где Vi, Va, Va, V, Vs - мгновенныезначения-сигнала в моменты ts, t4, t3, t2,11.представленные в цифровом коде.

Одновременно с этим входной сигнал также поступает на амплитудный детектор 22, который производит его детектирования. Медленно меняющееся напряжение с выхода амплитудного детектора 22 поступа ет на вход АЦП 23, который с периодом Т0 производит преобразования мгновенных значений этого напряжения в цифровой код. Этот цифровой код запоминается в пятом регистре 24 сдвига и затем поступает на вход блока 25 деления на два. Результат деления, равный Р А/2, где А - значения амплитуды измеряемого сигнала, поступает на второй вход цифрового компаратора 9 и используется в качестве оптимального порога Цифровой компаратор 9 сравнивает цифровой код Vs с порогом Р. Если значение Уз не превышает порог Р, то на втором выходе- Цифрового компаратора 9 устанавливается низкий уровень - О, а на первом - высокий уровень- 1, вследствие чего ключи 12 и 13 оказываются закрытыми, а ключи 14 и 15 - Открытыми.

Цифровой код V2 поступает на первый (инвертирующий) вход сумматора 8, а на его второй вход поступает Цифровой код V4. На выходе сумматора 8 формируется цифровой код (Уз-Уа). который после умножения на

два в блоке 10.умножения через открытый ключ 14 и элемент ИЛИ 17 поступает на второй вход блока 18 деления. :

Одновременно цифровой код Vi поступает на первый (инвертирующий) вход сумматора 1 Т, а цифровом код Vs- на его второй вход, в результате чего на выходе сумматора 11 формируется цифровой код. соответствую ющий (VsrVi), который через открытый ключ 15 и элемент ИЛИ 16 поступает на первый вход блока 18 деления. На выходе блока 18 деления формируется цифровой код, соответствующий (V5-Vl)/2(V4-V2).

ЦАП 19 преобразует цифровой код в значение напряжения, эквивалентное входному цифровому коду. Блок 20, вычисляя функцию arccos от значения входного напряжения, дополнительно умножает результат вычисления на коэффициент 1/(2 л:Т0).

Таким образом, на выходе устройства воз никает напряжение, пропорциональное частоте входного сигнала, определяемое по формуле

f

( V5-Vi

- arccos

i о 2 ( V4 - V2 )

В том случае, если значение Уз превышает порог Р, то на втором входе цифрового компаратора 9 устанавливается 1. а на первом выходе - О. Вследствие этого ключи 12 и 13 оказываются открытыми, а ключи 14 и 15 - закрытыми. Цифровые коды /2 и V4 поступают на входы сумматора 7, вследствие чего на его выходе образуется цифровой .код,соответствующий (Va + Уз), который через открытый ключ 12 и элемент ИЛИ 16 поступает на первый вход блока 18 деления. Цифровой код Уз поступает в блок 6 умножения на два, с выхода которого через открытый ключ 13 и элемент ИЛИ 17 поступает на второй вход блока 18 деления. Таким образом, на выходе блока 18 деления формируется цифровой код. определяемый выражением (V2 + Ул). который после вышеописанного цифроаналогового преобразования в ЦАП 19 и арифметическом блоке 20 превращается в напряжение, пропорциональное частоте входного сигнала, определяемое по формуле

1

2 л: То

arccos - -7-7Y -±Yi 2 Уз

Поскольку в установившемся режиме мгновенные значения напряжения входного сигнала Vi, V2, Уз. Уз, Уз присутствуют постоянно, то устройство обеспечивает выдачу значений частоты входного сигнала через тактовый интервал Т0.

При медленном увеличении (уменьшении) амплитуды входного сигнала напряжение на выходе амплитудного детектора 22 также пропорционально увеличится (уменьшится). Соответственно увеличатся (уменьшатся) выборки цифрового кода, получаемые на выходе второго АЦП 23. Эти цифровые выборки Ai (i - дискретные отсчеты времени) поступают через пятый регистр 24 сдвига и блок 25 деления на два на вто- рой вход цифрового компаратора 9 и формируют оптимальный порог Р.

Таким образом, оптимальный порог цифрового компаратора корректируется при изменении амплитуды входного сигнала. Это уменьшает погрешность оценок частоты и повышает достоверность результатов измерений.

5Формула изобретения

Устройство для измерения частоты гармонического сигнала, содержащее генератор импульсов, выход которого соединен с тактовыми входами последовательно соеди0 ненных аналого-цифрового преобразователя, первого, второго, третьего и четвертого регистров сдвига соответственно, вход аналого-цифрового преобразователя является входом устройства, а выходы аналого-циф5 рового преобразователя и четвертого регистра сдвига соединены соответственно с первым и вторым входами третьего сумматора, выход которого через четвертый ключ соединен с первым входом первого элемен0 та ИЛИ, выход которого через цифроанало- говый преобразователь соединен с входом арифметического блока, выход которого является выходом устройства, выходы первого и третьего регистров сдвига соединены со5 ответственно с первыми и вторыми входами первого и второго сумматоров, причем выход первого сумматора через первый ключ подключен к второму входу первого элемента ИЛИ, выход второго регистра сдвига че0 рез последовательно соединенные первый блок умножения и второй ключ соединен с первым входом второго элемента ИЛИ, вы-, ход которого соединен с вторым входом блока деления, выход второго сумматора че5 рез последовательно соединенные второй блок умножения и третий ключ подключен к второму входу второго элемента ИЛИ, .выход второго регистра сдвига соединен с первым входом цифрового компаратора,

0 первый выход .которого соединен с управляющими входами третьего и четвертого ключей, а второй выход - с управляющими входами первого и второго ключей, отличающееся тем, что, с целью повышения

5 точности и достоверности измерений, дополнительно введены последовательно соединенные амплитудный детектор, второй аналого-цифровой преобразователь, пятый регистр сдвига, блок деления на два,

0 выход которого соединен с вторым входом цифрового компаратора, при этом вход амплитудного детектора соединен с входом устройства, а тактовые входы второго аналого-цифрового преобразователя и пятого

5 регистра сдвига соединены с выходом генератора импульсов.

S&

p

A

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1524011A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ УГЛОВОЙ КООРДИНАТЫ СИСТЕМЫ ПОСАДКИ | 1990 |

|

SU1760868A1 |

| Устройство для демодуляции цифровых сигналов с частотной модуляцией | 1988 |

|

SU1552397A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ СВЕРТЫВАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2390792C2 |

| ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР | 1991 |

|

RU2017340C1 |

| Цифровой частотный детектор | 1990 |

|

SU1714530A1 |

| Измеритель электропроводности | 1989 |

|

SU1670623A1 |

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| Устройство для измерения среднеквадратического значения напряжения | 1989 |

|

SU1786443A1 |

| СЕЛЕКТИВНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОДНОФАЗНЫХ ЗАМЫКАНИЙ В КАБЕЛЬНЫХ ЛИНИЯХ | 1994 |

|

RU2079145C1 |

Изобретение относится к измерительной технике и предназначено для изменения частоты гармонического сигнала. Устройство для измерения частоты гармонического сигнала содержит: два анало- го-цифровых преобразователя 1, 23, пять регистров сдвига 2, 3, 4, 5, 24, блок умножения 6,3 сумматора 7, 8, 11, цифровой компаратор 9, блок умножения 10, четыре ключа 12,13, 14, 15, два элемента ИЛИ 16, 17, блок деления 18, цифроаналоговый преобразователь 19, арифметический блок 20, генератор импульсов 21, амплитудный детектор 22, блок деления на два 25.

-A

-P

Фиг. 4

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1524011A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-04-15—Публикация

1991-06-14—Подача