1

(21)4422462/24-09

(22)10.05.88

(46) 23.03.90. Бюл. № 11

(72) И.И.Булгаков и К.Д.Лазинцев

(53) 621.396.6(088.8)

(56)Спилкер Дж. Цифровые спутниковые связи. - М.: Связь, 1979, с. 292.

(54) ДЕТЕКТОР СИГНАЛОВ МАНИПУЛЯЦИИ С МИНИМАЛЬНЩ СДВИГОМ

(57)Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Детектор сигналов манипуляции с минимальным сдвигом содержит генератор 1, синхронизатор 2, преобразователь 3 аналог - код,

сумматор 4, блок 5 сравнения, регистры 6 и 9, триггер 7 и формирователь 8 управляющих сигналов. Для повышения помехоустойчивости детектора в сумматор 4 введен порог на максимально возможную величину А А |А; - А;+,| (где А ;4, и А,- - коды амплитуд входного сигнала в данный момент времени, а также полученный при предыдущем отсчете) путем ограничения разрядной сетки при вычислении &А. Это исключает погрешность вычислений при резких скачках значений ДА, вызванных действием помех на входной сигнал. Детектор по пп. 2 и 3 ф-лы отличается выполнением синхронизатора 2 и фор- с мирователя 8. 2 з.п. ф-лы, 3 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 2005 |

|

RU2279098C1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Цифровой демодулятор сигналов с двухуровневой амплитудно-фазовой манипуляцией и относительной оценкой амплитуды символа | 2022 |

|

RU2790140C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Преобразователь линейного перемещения в код | 1984 |

|

SU1274156A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| Устройство формирования точной оценки измеряемого параметра | 1983 |

|

SU1100594A1 |

| Измеритель отношения переменных напряжений | 1986 |

|

SU1357855A1 |

| Измеритель сдвига фаз | 1986 |

|

SU1366966A1 |

| Устройство для амплитудного анализа импульсов | 1980 |

|

SU938176A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Детектор сигналов манипуляции с минимальным сдвигом содержит генератор 1, синхронизатор 2, преобразователь 3 аналог - код, сумматор 4, блок сравнения 5, регистры 6 и 9, триггер 7 и формирователь 8 управляющих сигналов. Для повышения помехоустойчивости детектора в сумматор 4 введен порог на максимально возможную величину ΔА= @ A1 - AI+1 @ (где AI+1 и AI - коды амплитуд входного сигнала в данный момент времени, а также полученный при предыдущем отсчете) путем ограничения разрядной сетки при вычислении ΔА. Это исключает погрешность вычислений при резких скачках значений ΔА, вызванных действием помех на входной сигнал. Детектор по п.п. 2 и 3 ф-лы отличается выполнением синхронизатора 2 и формирователя 8. 2 з.п. ф-лы, 3 ил.

Сл СП

«

со

bo

%/«v

Изобретение относится к -электросвязи и может быть использовано п системах передачи данных.

Цель изобретения - повышение поме хоустойчипости.

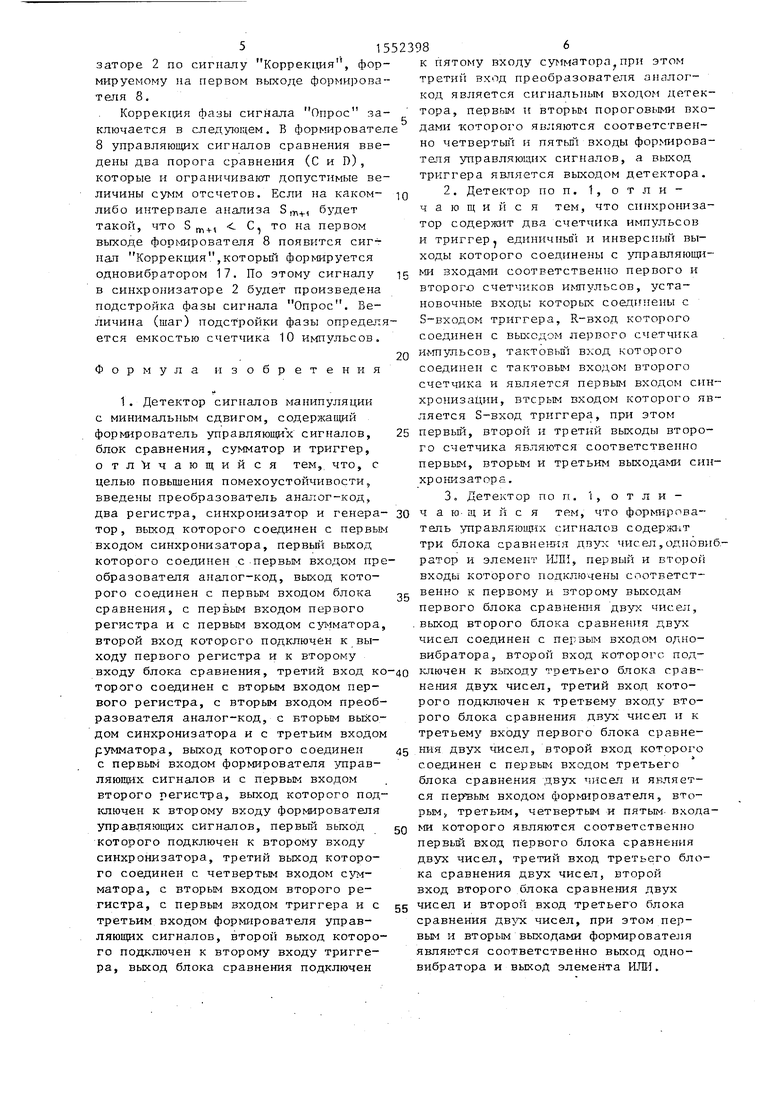

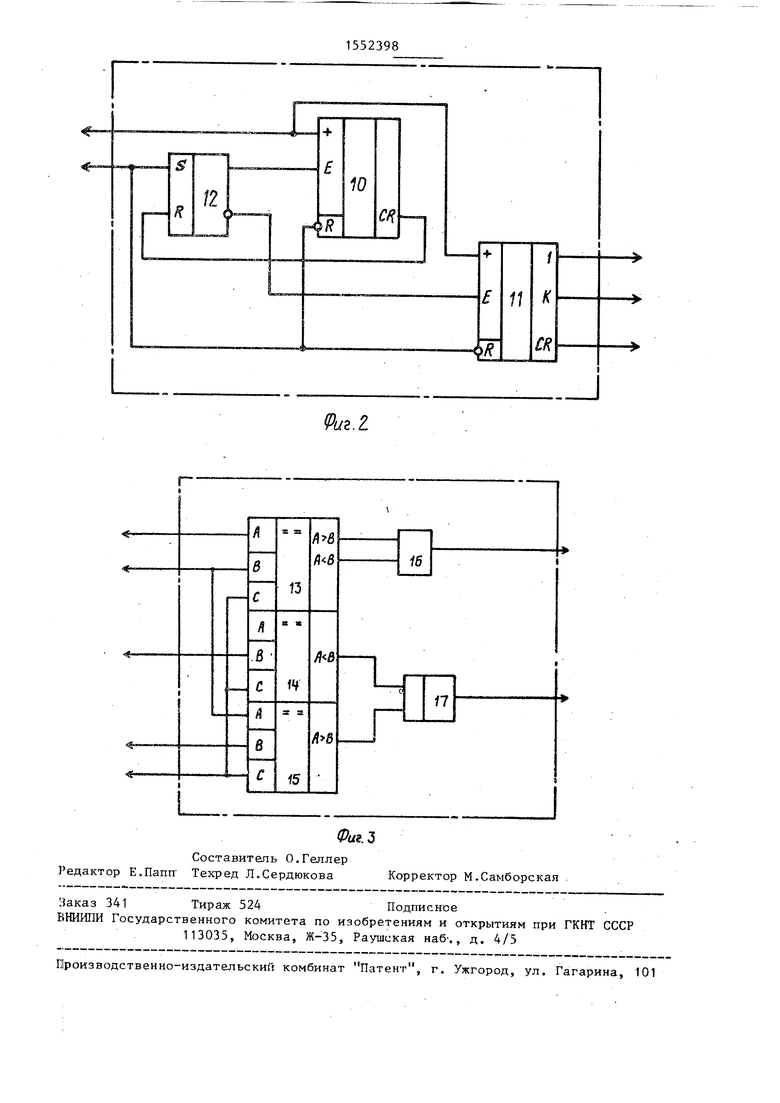

На фиг. 1 изображена структурная электрическая схема предлагаемого детектора; на фиг. 2 - структурная электрическая схема синхронизатора; на фиг. 3 - структурная -электрическая схема формирователя управляющих сигналов.

Детектор сигналов манипуляции с минимальным сдвигом содержит генера- тор 1, синхронизатор 2, преобразователь 3 аналог-код, сумматор 4, бпок 5 сравнения, первый регистр 6, триггер 7, формирователь 8 управляющих сигналов и второй регистр 9.

Синхронизатор содержит первый и второй счетчики 10 и 11 импульсов и триггер 12. Формирователь управляющих сигналов содержит первый, второй и третий блоки 13-15 сравнения двух чисел, элемент ИЛИ 16 .и одновибратор 17.

Детектор работает следующим образом .

Входной сигнал поступает на вход преобразователя 3 аналог - код, на другой вход которого поступают импульсы тактовой частоты (Јт/2) с первого выхода синхронизатора 2.

В преобразователе 3 аналог-код произ- ни и при резких скачках значений ,

водится измерение амплитуды входного сигнала в точках отсчета и выдача результатов измерения в коде, определяющем значение амплитуды входного А; в данный момент времени. Количество импульсов, поступающих на преобразователь 3 аналог-код от синхронизатора 2, на каждом интервале отсчета выбирается из условия возможности измерения максимальной амплитуды входного сигнала (неискаженного). Под воздействием помех (импульсных,гармонических и др.) амплитуда входного сигнала может превысить указанный порог, однако на выходе преобразователя 3 аналог-код будет зафиксировано максимально возможное значение амплитуды входного сигнала (т.е. произойдет ограничение по амплитуде измеряемого сигнала), что повысит помехоустойчивость приема особенно при действии импульсных помех. Количество отсчетов п на интервале анализа, равном длительности элементарного передаваемого

сигнала (0 , выбирается достаточно большим с цепью пмпьоненип то июсти ап- пргкс.имации входного сигнала.

По сигналу Отсчет синхронизатора 2. в первом блоке S сравнения производится сравнение амппитуд входного сигнала в данной момент времени (А;м) с кодом амплитуды входного сигнала, полученным при предыдущем отсчете (А () и хранящимся в первом регистре 6, и формирование сигнала Чнак, соответствуюнего выражению |Л;|(А;,|.

По заднему фронту сигнала Отсчет выполняются следующие операции: в сумматоре 4 вычисляется ДА |Л;- Л;+(| (с учетом сигнала Чнак) и уммирует- ся текущее (вычисленное) значение с результатами всех вычислений, полученных на предыдущих отсчетах на данном интервале анализа; стирание в первом регистре 6 значе гия Л и запись в него текущего значения А;41 ; установка в исходное состояние преобразователя 3 анатог-код.

Сумматор 4 состоит из комбинационного сумматора-вычитателя и накапливающего сумматора (не показано). С целью повышения помехоустойчивости детектора в сумматоре 4 введен порог на максимально возможную величину Л А путем ограничения разрядной сетки при вычислении & А | А; - A;f, | (где ,2, . . п), что исключает погрешность вычислеО5

0

5

вызванньк действием помех на входной

сигнал.

I

По достижении конца интервала анализа, равного длительности элементарного сигнала (посыпки), на третьем выходе синхронизатора 2 появляется сигнал Опрос. По этому сигналу в формирователе 8 управляющих сигналов производится сравнение значения суммы отсчетов, полученных на предыдущем интервале анализа (Sm), с текущим значением суммы отсчетов (S ти ). По заднему фронту сигнала Опрос производятся следующие действия: триггер 7 переключается в положение, соответствующее сигналу на втором выходе фор- мироватепя 8 (&S); содержимое второго регистра 9 ($„,) стирается и в него записывается текущее значение суммы отсчетов (Smv,); сумматор А устанавливается в исходное состояние; производится (если это необходимо) коррекция фазы сигнала Опрос в синхронизаторе 2 по сигналу Коррекция, формируемому на первом выходе формирователя 8.

Коррекция фазы сигнала Опрос за- ктючается в следующем. В формировател 8 управляющих сигналоп сравнения введены два порога сравнения (С и D), которые и ограничивают допустимые величины сумм отсчетов. Если на какомSm. будет

либо иитерпале аналичл от+, такой, что S m+, С то на первом выходе фор;п1ропатепя 8 появится сигнал Коррекция,который формируется одновибратором 17. По этому сигналу в синхронизаторе 2 будет произведена подстройка фазы сигнала Опрос. Величина (таг) подстройки фазы Шределя- ется емкостью счетчика IO нмпУЛЬСОВ.

Форму

и з обр е т

е н и я

входу блока сравнения, третий вход ключей к выходу -ретьего блока сравторого соединен с вторым входом первого регистра, с вторым входом преобразователя аналог-код, с вторым выходом синхронизатора и с третьим входом румматора, выход которого соединен с первым входом формирователя /прав- ляющих сигналов и с первым входом второго регистра, выход которого подключен к второму входу формирователя управляющих сигналов, первый выход которого подключен к второму входу синхронизатора, третий выход которого соединен с четвертым входом сумматора, с вторым входом второго регистра, с первым входом триггера и с третьим входом формирователя управляющих сигналов, второй выход которого подключен к второму входу триггера, выход блока сравнения подключен

0

к пятому входу сумматора,при этом третий нход преобразорателя аналог - код является сигнальным входом детектора, первым и вторым пороговыми входами которого являются соответственно четвертый и пятый входы формирователя управляющих сигналов, я выход триггера является выходом детектора.

и триггер, единичный и инверсный выходы которого соединены с управляющиc мл входами соответственно первого и второго счетчиков импульсов, установочные входы котормх соединены с S-РХЭДОМ триггера, R-вход которого соединен с выходам лергчто счетчика

Q импульсов, тактольо в;.од которого соединен с тактовым вхочом второг счетчика и явпяется первым входом син- .щии, втгрым входом которого является S-вход триггера, при этом

5 первый, второй и третий выходы второго счетчика являются соответственно первым, вторым и третьим выходами синхронизатор .

5

нания двух чисел, третий вход которого подключен к третьему входу второго блока сравнения двух чисел и к третьему входу первого блока срлвнения двух чисел, второй вход которого соединен с первым входом третьего блока сравнения двух чисел и является первым входом формирователя, вторым, третьим, четвертым и пятым лхолами которого являются соответственно первый вход первого блока сравнения двух чисел, третий вход третьего блока сравнения двух чисел, второй вход второго блока сравнения двух

чисел и второй вход третьего блока сравнения двух чисел, при этом первым и вторым выходами формирователя являются соответственно выход одно- вибратора и выход элемента ИЛИ.

Я/г. 2

Авторы

Даты

1990-03-23—Публикация

1988-05-10—Подача