Изобретение относится к вычислительной технике, в частности к устройствам записи информации в полупроводниковые запоминающие устройства.

Целью изобретения является расширение области применения за счет увеличения класса программируемых микросхем, и повышения надежности программирования.

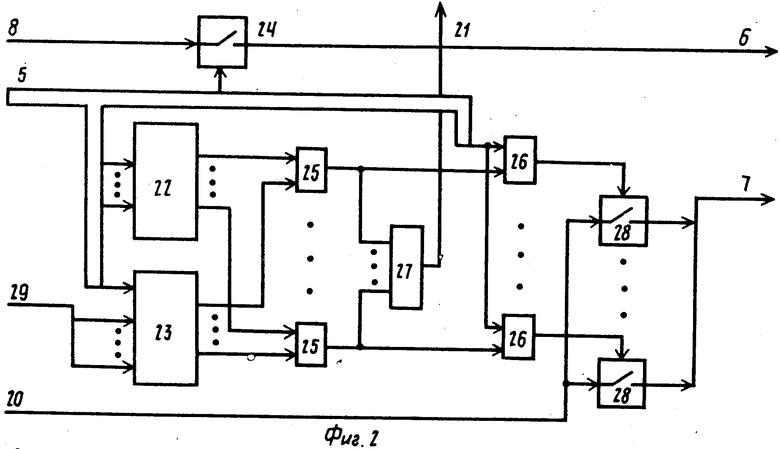

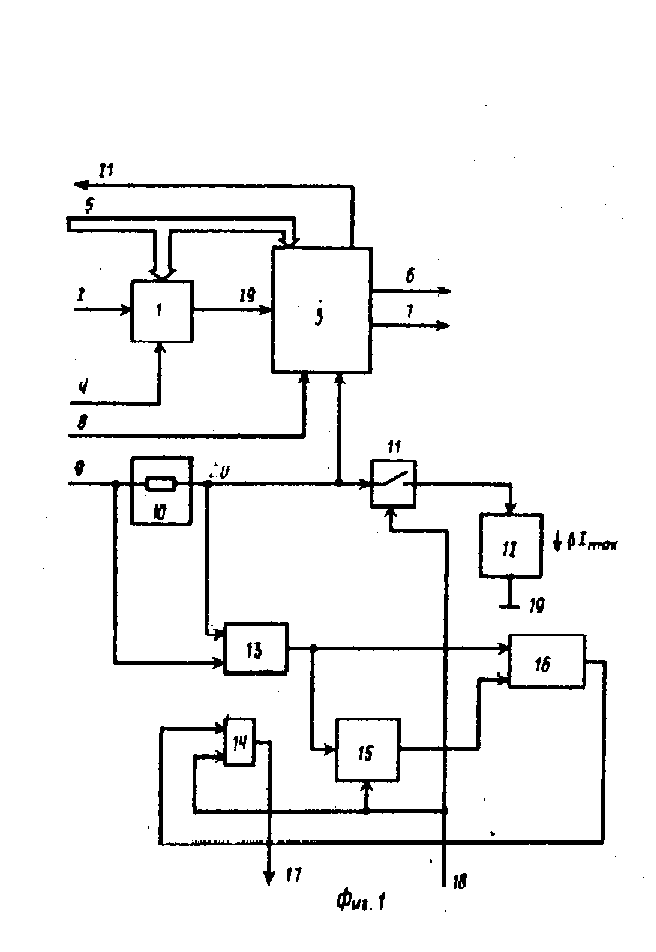

На фиг. 1, 2 представлены соответственно блок-схема устройства и блок-схема блока передачи данных.

Устройство для записи информации в ППЗУ содержит блок памяти 1, информационный вход 2, блок передачи данных 3, адресный вход 4, группу шин 5 управления работой устройства, выход 6 передачи высокого напряжения питания, информационный выход 7 блока передачи данных, вход 8 передачи высокого напряжения блока передачи данных, первый генератор тока 9 с первым выводом 10, ключевую схему 11, второй генератор тока 12, усилитель 13, элемент И 14, блок выборки-хранения 15 начального тока, компаратор 16, выход 17 контроля окончания программирования, вход 18 разрешения программирования, шину 19 нулевого потенциала, второй вывод 20 первого генератора тока, выход 21 контроля начала программирования.

Блок передачи данных содержит дешифратор 22, регистр 23, ключевую схему 24 блока передачи данных, элементы И 25 первой группы, элементы И 26 второй группы, элемент ИЛИ 27, ключевые схемы 28 группы, информационные входы 29.

Устройство работает следующим образом.

Микросхема ППЗУ, подлежащая программированию, соответствующими выводами подключается к выходам 6, 7, к входу 4 и входу 18 разрешения программирования. Под действием сигналов на шинах 5 управления и на входе 4 адреса в блок 1 памяти по входу 2 заносится программа (коды ППЗУ) с какого-либо внешнего устройства или вручную. Затем, в соответствии с начальным адресом, передаваемым по входу 4, код данных из блока 1 памяти передается на вход 29 блока 3 передачи данных и заносится в регистр 23. По одной из шин 5 на вход дешифратора 22 подается начальный код, вызывающий появление сигнала логической "1" на первом выходе дешифратора 22. Если на первом выходе регистра 23 присутствует сигнал логического "0", т. е. отсутствует необходимость в пережигании перемычки, то на выходе 21 блока 3 не вырабатывается запускающий сигнал для задания режима программирования микросхемы ППЗУ и на вход дешифратора 22 подается следующий код, вызывающий появление логической "1" на следующем выходе дешифратора 22.

При наличии логической "1" на соответствующем выходе регистра 23 на выходе 21 блока 3 вырабатывается запускающий сигнал логической "1", в ответ на который по одной из шин 5 управления в блок 3 поступают сигналы, обеспечивающие задание режима программирования микросхемы ППЗУ, а именно: замыкается ключевая схема 24 и соответствующая ключевая схема 28, на выход 6 поступает повышенное напряжение питания с шины 8, а на выход 7 - напряжение программирования с входа 9.

Если на входе 18 разрешения программирования сигнал отсутствует (логический "0"), то при этом через ключевую схему 11 к выходу 20 генератора тока 10 подключен источник тока 12, имеющий величину тока Io+ Δ Iмакс; блок 15 находится в режиме выборки; на втором входе элемента И 14 присутствует логический "0"; по входу 9 напряжения программирования и генератору тока 10 протекает ток величиной Io + ΔIмакс.

Сигнал в генераторе тока 10 через усилитель 13 поступает на вход блока 15, который работает в режиме выборки. Затем на входе 18 разрешения программирования появляется сигнал логическая "1", при этом блок 15 переводится в режим хранения и фиксирует на своем выходе напряжение, соответствующее протекающему через генератор 10 току величиной Io + ΔIмакс; ключевая схема 11 размыкается; по выводу 9 и генератору 10 начинает протекать ток для программирования выбранной перемычки.

Сигнал с генератора 10 через усилитель 13 поступает на первый вход компаратора 16, на втором входе которого присутствует напряжение с выхода блока 15. Когда выбранная перемычка разрушается, протекающий через генератор 10 ток уменьшается до величины, меньшей чем Io + Δ Iмакс. При этом значение напряжения на первом входе компаратора 16 будет меньше, чем на втором его входе, компаратор переключится и на его выходе появится сигнал логической "1", поступающий на первый вход элемента И 14, на втором входе которого присутствует сигнал логической "1", поступающий с входа 18 разрешения программирования. В результате элемент И 14 срабатывает и на выходе 17 появляется сигнал окончания программирования.

При появлении этого сигнала прекращается подача сигналов по одной из шин 5 управления, вызывающих замыкание схем 24 и 28, а также прекращается подача сигнала по входу 18. Таким образом, режим программирования прекращается сразу после разрушения выбранной перемычки. После выдержки паузы, необходимой для охлаждения микросхемы ППЗУ, осуществляется проверка состояния следующего разряда регистра 23 и пережигание следующей перемычки в случае наличия логической "1" в этом разряде кода данных. После перебора всех разрядов кода данных, записанного в регистре 23, по входу 4 адреса передается следующее значение адреса и в регистр 23 из блока 1 памяти заносится новый код данных. Далее процесс повторяется для всего массива адресов.

Таким образом, предлагаемое устройство позволяет осуществлять запись информации для более широкого класса существующих типов ППЗУ при сохранении быстродействиязаписи информации. В устройстве повышена достоверность критерия разрушения перемычки, что позволяет повысить надежность занесения информации в ППЗУ благодаря контролю величины тока утечки матрицы ППЗУ в процессе программирования, так как при этом появляются не полностью разрушенные перемычки и матрицы микросхем ППЗУ, имеющие завышенный ток утечки, ухудшающийкачество программирования. (56) Авторское свидетельство СССР N 1280449, кл. G 11 C 7/00, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для программирования микросхем памяти | 1986 |

|

SU1381592A1 |

| Устройство для контроля и идентификации пользователя | 1991 |

|

SU1833902A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для обмена данными | 1984 |

|

SU1239724A2 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1985 |

|

SU1354243A1 |

| Устройство для записи информации в полупроводниковые блоки постоянной памяти | 1987 |

|

SU1444882A2 |

Изобретение относится к вычислительной технике, в частности к устройствам записи информации в полупроводниковые запоминающие устройства. Целью изобретения является расширение области применения за счет увеличения класса программируемых микросхем. Поставленная цель достигается тем, что устройство для записи информации в программируемое постоянное запоминающее устройство содержит второй генератор тока, ключевую схему, блок выборки и хранения начального тока, компаратор, а блок передачи данных устройства содержит дешифратор, регистр, ключевую схему, первую и вторую группы элементов И, элемент ИЛИ и группу ключевых схем. 2 ил. , 1 з. п. ф-лы.

Авторы

Даты

1994-05-15—Публикация

1988-04-01—Подача