(21)4407372/24-24

(22)11.04.88

(46) 23.04.90. Бкш. № 15 (72) С.А, Куликов

(53)681.325(088.8)

(56)Авторское свидетельство СССР по заявке № 4132396/09,

кл. Н 03 М 7/00, 20.01.88.

Авторское свидетельство СССР по заявке № 4327674/24, кл. Н 03 М 7/30, 1988.

(54)УСТРОЙСТВО ДЛЯ ЭФФЕКТИВНОГО КОДИРОВАНИЯ ИЗОБРАЖЕНИЙ

(57)Изобретение относится к вычислительной технике и технике связи. Его

использование в цифровых телевизионных системах позволяет повысить помехоустойчивость и упростить устройство, которое содержит сипхрогенера- тор 1, блок 2 временных задержек, сумматоры , вычитатели 7-10, коммутаторы 16, 17 и преобразователь параллельного кода в последовательный. Благодаря введению элемента ИЛИ 11, блока 12 сумматоров по модулю два, буферных регистров 13-15, блока 18 оперативной памяти и триггера 19 в устройстве обеспечивается адаптивное помехоустойчивое кодирование с повышенным качеством изображений, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный импульсный кодер телевизионного сигнала | 1987 |

|

SU1481900A2 |

| Устройство сжатия полосы частот видеосигнала | 1986 |

|

SU1394466A1 |

| Устройство для кодирования телевизионного сигнала | 1988 |

|

SU1559409A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство имитостойкого кодирования и декодирования информации избыточными систематическими кодами | 2016 |

|

RU2634201C1 |

| Устройство для кодирования | 1987 |

|

SU1462494A1 |

| Устройство для кодирования и декодирования двоичной информации сверточными кодами | 1982 |

|

SU1035819A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Устройство для кодирования | 1987 |

|

SU1496010A2 |

| Декодер мажоритарных блоковых кодов | 1986 |

|

SU1349011A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в цифровых телевизионных системах позволяет повысить помехоустойчивость и упростить устройство, которое содержит синхрогенератор 1, блок 2 временных задержек, сумматоры 3-6, вычитатели 7-10, коммутаторы 16, 17 и преобразователь параллельного кода в последовательный. Благодаря введению элемента ИЛИ 11, блока 12 сумматоров по модулю два, буферных регистров 13-15, блока 18 оперативной памяти и триггера 19 в устройстве обеспечивается адаптивное помехоустойчивое кодирование с повышенным качеством изображений. 2 ил.

СЛ

сл

SD

Јь

Изобретение относится к вычислительной технике и технике связи и может быть использовано в цифровых телевизионных системах.

Цель изобретения - повышение помехоустойчивости и упрощение устройства.

На фиг. приведена функциональная схема устройства; на фиг. 2 - блок сумматоров по модулю два.

Устройство содержит синхрогенера- тор 1, блок 2 временных задержек, первый - четвертый сумматоры 3-6, первый - четвертый вычитатели 7-10, элемент ИЛИ 11, блок 12 сумматоров по модулю два, первый - третий буферные регистры 13-15, первый 16 и второй 17 коммутаторы, блок 18 оперативной памяти, триггер 19 и преобразователь 20 параллельного кода в последовательный.

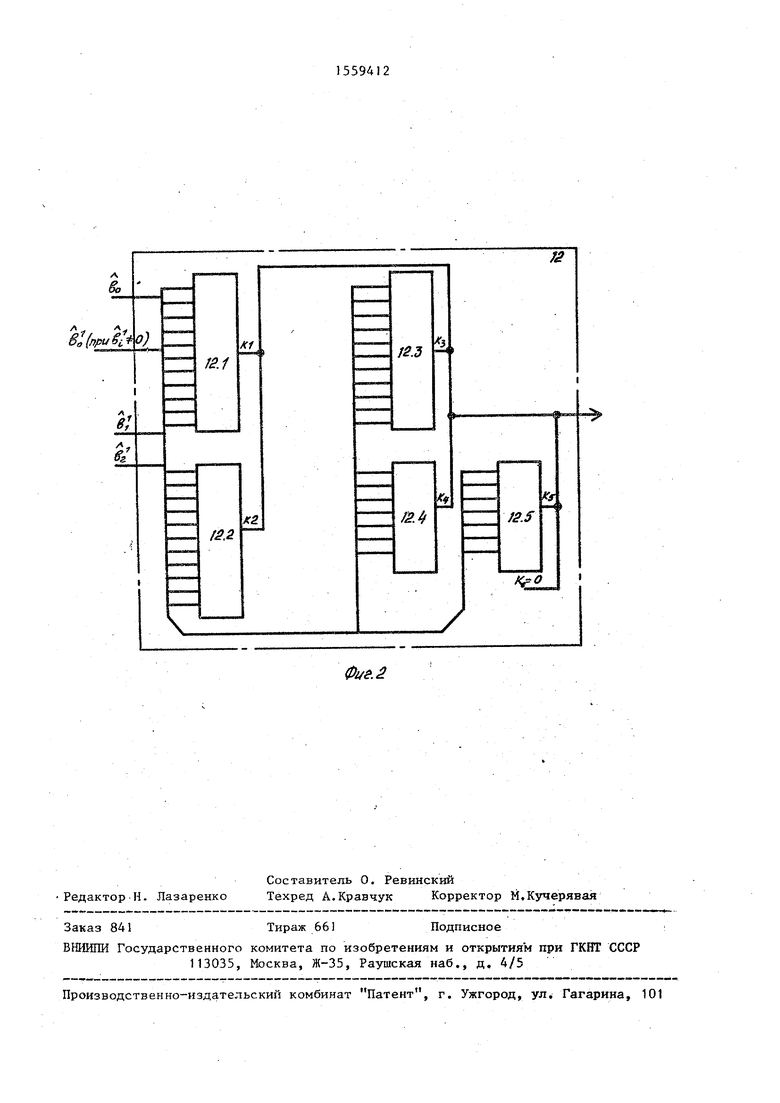

Блок 2 реализован в виде последовательно-параллельного регистра. Сумматор 6 и вычитатели 9 и 10 трехразрядные. Блок 12 выполнен (фиг. 2) на сумматорах по модулю два. На фиг.2 обозначено: Ъ - j-й разряд (j 1,6) шестиразрядного кода Ъ0 ; Ъ(. j-й разряд (j 1,3) трехразрядного кода b; (i 1 л 2) | К;- i-й проверочный символ (i 1,6).

Блок 18 реализован на двух последовательно соединенных и одновременно тактируемых параллельных регистрах.

Преобразователь 20 может быть реализован на мультиплексоре.

Синхрогенератор I выдает на первом выходе последовательность импульсов с тактовой частотой fr, на втоцрм выходе - с частотой группы Јт/4, а на третьем выходе - с канальной частотой

В устройстве реализуется следующий

алгоритм.

Кодируемые элементы a(i 6,3) подвергаются быстрому преобразованию Адамира с вычислением

-.

В„ а„ + а, + а.

аъ

В,

Л

В«

А

в,

а„ - а. + а„ а

а.

а.

+ а, - аа - а.

- а, аг + а

Затем формируется корректирующий д с восемнадцатью информационными шестью проверочными символами п едующему закону. Коды Б0, Б, и Бс

ЛЛА

код D равенства нулю В1 , В, В

0

5

0

5

0

5

0

5

0

5

,3 находятся значения |« „ „ t

Если D 1, т.е.

задерживаются на такт частоты группы, а код В0 - на два такта этой частоты. Для группы oi со значениями элементов

лЛЛА

5, « ИА S

С в;К|в в; илр . г

когда В| Вг В3 ,0, от группы ei защищаются разряды В0 ,.а от.группы

г IIЛ ц л И fl

Ос - разряды кодов В0, В4 и В4 . Поэтому при D 1 и D 1 нет необходиЛ1 «II Л(|

мости в защите от ошибок В0 , В0 , В,, , §Ј, так как они защищены. В этом случае в кодере защищаются шесть разрядов В0. При D (0 1 формируется код с

ft,

м

В, В, , В4, а приВ D .1 R(

QJ О f - - - . код с информационными символами Вд, Лш &i Л Т

С0 В1 Й2.

Рассмотрим 4 группы, следующие друг за другом: сх,, ., °Ц 4- Пусть D( Dt 0 и D3 D(. 1 . В рассматриваемом устройстве защищены группы г, о(з и а также 6 разрядов В0 группы di . Эти разряды по отношению к группе 0(4.

в соответствии с принятыми обознзчедшниями будут BQ . Таким образом, кроме

равнояркостных и контурных (т.е. прилегающих к группам с D l) групп, защищается часть текстурных групп (т.е. прилегающих к группам с D 0). Очевидно, что эффективность реализуемого адаптивного /к значению D ) помехоустойчивого кодирования тем выше, чем больше детальность изображений.

Устройство работает следующим образом.

На вход блока 2 поступает видеосигнал в цифровом виде. С помощью сумматоров 3-6 и вычитателей 7-10 формируются четыре элементадтрансформанты Адамира: В0, В, В4, Вэ. Коды В0, Bt, В г поступают на входы регистров 13-15 соответственно, где задерживаются на время кодирования квартета из четырех элементов изображения.

На выходах этих регистров находятся коды В0, В , BЈ предшествующей кодируемой группы. Коды В,, ступают на вход элемента I1, где осуществляется поразрядное сложение этих трехразрядных кодов. Сигнал D с выхода элемента 11 является управляющим для коммутатора 16, а также задерживается на такт частоты группы в триггере 19. Кроме того, сигнал D поступает в преобразователь 20. В блоблоке 12 восемнадцати информационным

2 Л А Л / А {, символам В0, В0, В, , В или Bfi, Б0 ,

В., В2 ставятся в соответствие шесть проверочных символов, которые посту Ј 3 П°

разрядДВ;

пают на один из входов коммутатора 1 На два других входа этого коммутатора 16 поступают шесть разрядов (в суме) В и В4 К выходу коммутатора 16 подключаются проверочные символы, если D 1. С помощью коммутатора 17 формируются шесть информационных символов для блока 12. Ими являА ft

ются разряды Bfl, если D 0 или разряды в й с выхода блока 18, если D 1, С помощью преобразователя 20 формируется выходное кодовое слово кодируемой группы.

Необходимо отметить, что знаковый

(i 1,2,3) равен нулю, когда В; 0.

Таким образом, устройство реализует адаптивное помехоустойчивое кодирование элементов трансформанты, при этом защищаются не только равно яркостные и контурные .группы, но и часть групп, принадлежащих текстурным участкам. За счет этого повышаются помехоустойчивость передачи высокодетальных изображений и, как следствие, качество таких изображений.

Формула изобретения

Устройство для- эффективного кодирования изображений, содержащее блок временных задержек, информационный вход которого является входом устройства, синхрогенератор, первый выход которого соединен с тактовым входом блока временных задержек, первый и второй выходы которого подключены соответственно к первым и вторым входам первых сумматора и вычитателя, третий и четвертый выходы блока временных задержек соединены соответственно с первыми и вторыми входами-вто вторых сумматора и вычитателя, выходы первого и второго сумматоров подключены соответственно к первым и вторым входам третьих сумматора и вычитателя, выходы первого и второго вычитателей соединены соответственно с первыми и вторыми входами четвертых сумматора и вычитателя, первый и второй коммутаторы и преобразователь параллельного кода в последователь- .ный, выход которого является выходом устройства, отличающееся тем что, с целью повышения помехоустойчивости и упрощения устройства, в

10

5

0

5

него введены буферные регистры, блок оперативной памяти, элемент ИЛИ, блок сумматоров по модулю два и триггер, выходы третьего сумматора подключены к информационным входам первого буферного регистра, первым информационным входам преобразователя параллельного кода в последовательный и первым входам блока сумматоров по модулю два, выходы которого соединены с первыми информационными входами первого коммутатора, выходы которого подключены к вторым информационным входам преобразователя параллельного кода в последовательный, выходы четвертого сумматора соединены с информационными входами второго буферного регистра, вторыми информационными входами первого коммутатора и первыми входами элемента ИЛИ, выход которого подключен к управляющему входу первого коммутатора, третьему информационному входу преобразователя параллельного кода в последовательный и информационному входу триггера, выход которого соединен с управляющим входом второго коммутатора, выходы блока оперативной памяти 0 подключены к первым информационным

входам второго коммутатора, выходы которого соединены с вторыми входами блока сумматоров по модулю два, выходы третьего вычитателя подключены к информационным входам третьего буферного регистра, вторым входам элемента ИЛИ и третьим информационным входам первого коммутатора, выходы четвертого вычитателя соединены с третьими входами элемента ИЛИ и четвертыми информационными входами преобразователя параллельного кода в последовательный, выходы первого буферного регистра подключены к информационным входам блока оперативной памяти и вторым информационным входам второго коммутатора, выходы второго и третьего буферных регистров подключены соответственно к третьим и четвертым входам блока сумматоров по модулю два, второй выход синхрогенератора соединен с тактовыми входами блока оперативной памяти, буферных регистров и триггера, третий выход синхрогенератора подключен к тактовому входу преобразователя параллельного кода в последовательный.

5

0

5

0

5

Фие.2

Авторы

Даты

1990-04-23—Публикация

1988-04-11—Подача