Область техники

Предлагаемое изобретение относится к области радио- и электросвязи и может быть использовано для обеспечения имитозащищенности и помехоустойчивости информации, передаваемой по радиоканалам, при кодировании и декодировании избыточными систематическими кодами.

Уровень техники

Известны способ и устройство помехоустойчивого кодирования и декодирования дискретной информации, содержащее на передающей стороне последовательно соединенные источник информации, блок информации, первый кодирующий блок, второй кодирующий блок, модулятор или передатчик, а на приемной стороне - два демодулятора приемника, разнесенные друг от друга, последовательно соединенные с ними первый декодирующий блок, приемный перемножитель, второй декодирующий блок, демультиплексор и получатель информации [Патент США №3988767, кл. H04L 1/10, 1976].

Недостатками данного устройства являются:

- низкий уровень помехоустойчивости при заданной скорости передачи;

- низкий уровень общей скорости кода.

Известно устройство для помехоустойчивого кодирования и декодирования двоичной информации сверточными кодами, содержащее на передающей стороне преобразователь входной информации, первый и второй канал кодирования, сумматор по модулю два, при этом выходы преобразователя входной информации подключены к входам коммутаторов разделения ветвей первого и второго каналов кодирования, причем выход кодера второго канала кодирования подключен к соответствующему входу коммутатора объединения ветвей второго канала кодирования, выход которого подключен к первому входу сумматора по модулю два, к второму входу которого подключен выход кодера первого канала кодирования, а выход сумматора по модулю два подключен к соответствующему входу коммутатора объединения ветвей первого канала кодирования, на приемной стороне - второй канал декодирования и преобразователь выходной информации, к выходам которого подключены выходы коммутаторов объединения ветвей первого и второго каналов декодирования, а также второй и третий сумматоры по модулю два, первый и второй буферные накопители, третий кодер и третий коммутатор объединения ветвей, при этом выход кодера первого канала декодирования подключен через первый буферный накопитель к первому входу первого сумматора по модулю два и через второй сумматор по модулю два - к входу коммутатора разделения ветвей второго канала декодирования, выход кодера второго канала декодирования подключен к первому входу первого сумматора по модулю два второго канала декодирования, а к второму входу первого сумматора по модулю два второго канала декодирования подключен соответствующий выход коммутатора разделения ветвей второго канала декодирования, выходы корректора ошибок второго канала декодирования подключены к входам третьего коммутатора объединения ветвей непосредственно и через третий кодер, при этом соответствующий выход коммутатора разделения ветвей первого канала декодирования подключен к второму выходу сумматора по модулю два и через второй буферный накопитель - к первому входу третьего сумматора по модулю два, к второму входу которого подключен выход третьего коммутатора объединения ветвей, а выход третьего сумматора по модулю два подключен к второму входу первого сумматора по модулю два [Авторское свидетельство №1035819 от 15.08.83 г. Устройство для кодирования и декодирования двоичной информации сверточными кодами А.И. Королев, О.Д. Купеев, 1983. - 5 с.: ил.].

Недостатком данного устройства является отсутствие возможности защиты передаваемой по каналам связи двоичной информации от преднамеренных (имитирующих действий злоумышленника) помех.

Наиболее близким по своей технической сущности к заявленному устройству имитостойкого кодирования и декодирования информации избыточными систематическими кодами (прототип) является устройство, описанное в [Касами Т., Токура Н., Ивадари Ё., Инагаки Я. Теория кодирования. М.: Мир, 1979, с. 298-300, фиг. 6.3, с. 396-397, фиг. 7.14].

Устройство-прототип на передающей стороне содержит первый канал кодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и коммутатора объединения ветвей, а на приемной стороне - канал декодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и к первой группе входов корректора ошибок, к второй группе входов которого подключены выходы анализатора синдромной последовательности, к входу которого подключен выход первого сумматора по модулю два, при этом выходы корректора ошибок подключены к входам коммутатора объединения ветвей.

К основному недостатку устройства-прототипа также следует отнести отсутствие возможности защиты передаваемой по каналам связи двоичной информации от преднамеренных (имитирующих действий злоумышленника) помех. Соответственно в условиях имитирующих действий злоумышленника, которому известны алгоритмы формирования избыточных систематических кодов (алгоритмы функционирования кодера), передаваемая имитируемая им двоичная информация на выходе приемного устройства воспринимается как легитимная.

Раскрытие изобретения

Целью заявляемого технического решения является обеспечение возможности защиты передаваемой по каналам связи двоичной информации от преднамеренных (имитирующих действий злоумышленника) помех.

Указанный технический результат достигается тем, что устройство для кодирования и декодирования двоичной информации сверточными кодами, содержащее на передающей стороне канал кодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и коммутатора объединения ветвей, а на приемной стороне - первый канал декодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и к первой группе входов корректора ошибок, к второй группе входов которого подключены выходы анализатора синдромной последовательности, к входу которого подключен выход первого сумматора по модулю два, при этом выходы корректора ошибок подключены к входам коммутатора объединения ветвей, на передающей стороне дополнительно введены блоки сумматоров по модулю два, блок распределения гаммы, регистр ключевой гаммы, при этом выходы регистра ключевой гаммы подключены к входу блока распределения гаммы, первая группа выходов которого подключена к второй группе входов первого блока сумматоров по модулю два, к первой группе входов которого подключены выходы коммутатора разделения ветвей, при этом выходы блока сумматоров по модулю два подключены к входам кодера, выходы которого подключены к первой группе входов второго блока сумматоров по модулю, к второй группе входов которого подключена вторая группа выходов блока распределения гаммы, при этом выходы второго блока сумматоров по модулю два подключены к соответствующему входу коммутатора объединения ветвей канала кодирования, а на приемной стороне дополнительно введены блоки сумматоров по модулю два, блок распределения гаммы, регистр ключевой гаммы, при этом выходы регистра ключевой гаммы подключены к входам блока распределения гаммы, первая группа выходов которого подключена к второй группе входов третьего блока сумматоров по модулю два, к первой группе входов которого подключены выходы коммутатора разделения ветвей, выходы третьего блока сумматоров по модулю два подключены к входам кодера, выходы которого подключены к первой группе входов второго блока сумматора по модулю, к второй группе выходов которого подключена вторая группа выходов блока распределения гаммы, при этом выход второго блока сумматоров по модулю два подключен к первой группе входов первого блока сумматоров по два, к второй группе входов которого подключены соответствующие выходы коммутатора разделения ветвей, выходы первого блока сумматоров по модулю два подключены к входам анализатора синдромной последовательности, выходы которого подключены к второй группе входов корректора ошибок, выходы которого подключены к соответствующим входам коммутатора объединения ветвей канала декодирования.

Благодаря введению в известный объект совокупности существенных отличительных признаков устройство имитостойкого кодирования и декодирования информации избыточными систематическими кодами обеспечивает защиту информации:

- от преднамеренных (имитирующих) помех, вызванных действиями злоумышленника, который не может вычислить и подменить избыточные символы, соответствующие новой (имитируемой) информации, как следствие необходимости вскрытия системы шифрования, используемой для обеспечения имитостойкости;

- от непреднамеренных помех (флуктуационных, космических, атмосферных).

Указанные отличительные признаки заявленного изобретения по сравнению с прототипом позволяют сделать вывод о соответствии заявленного технического решения критерию «новизна».

Описание чертежей

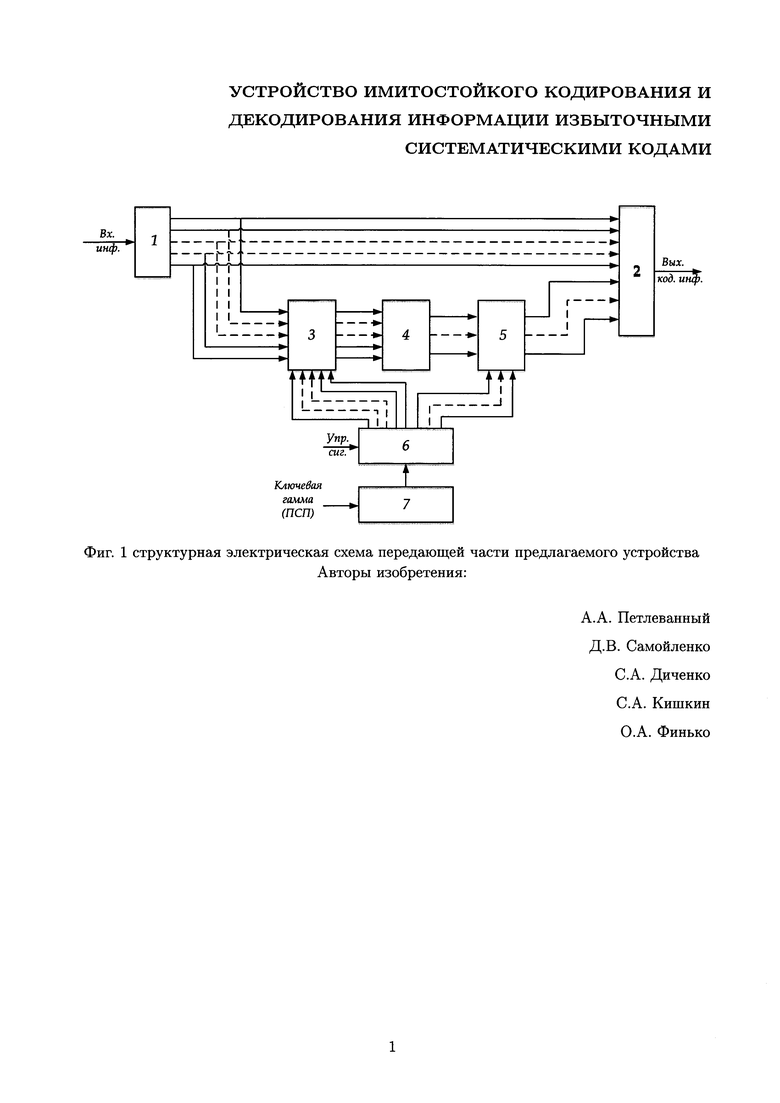

На чертежах представлено:

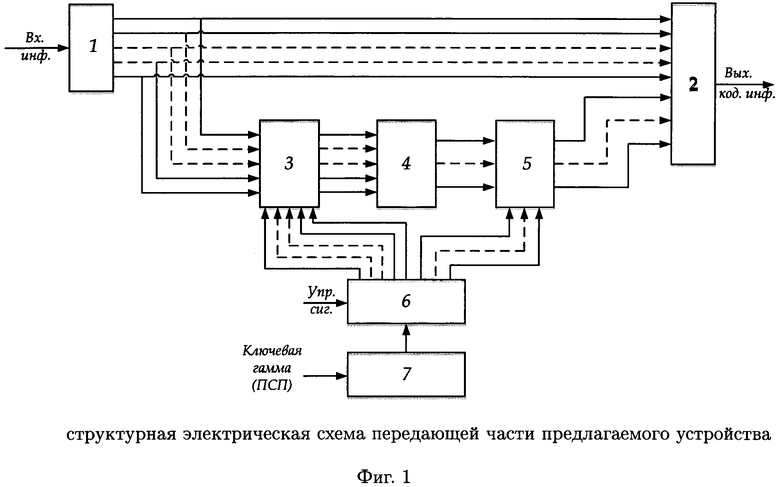

на фиг. 1 - структурная электрическая схема передающей части предлагаемого устройства;

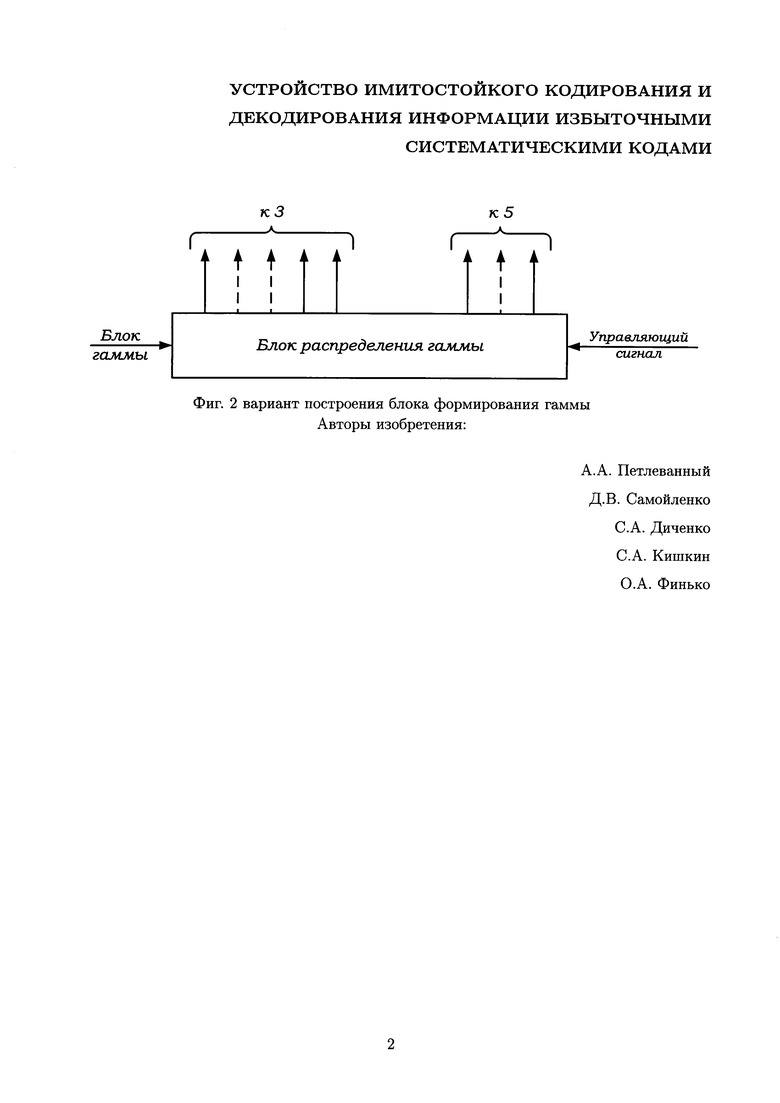

на фиг. 2 - вариант построения блока формирования гаммы;

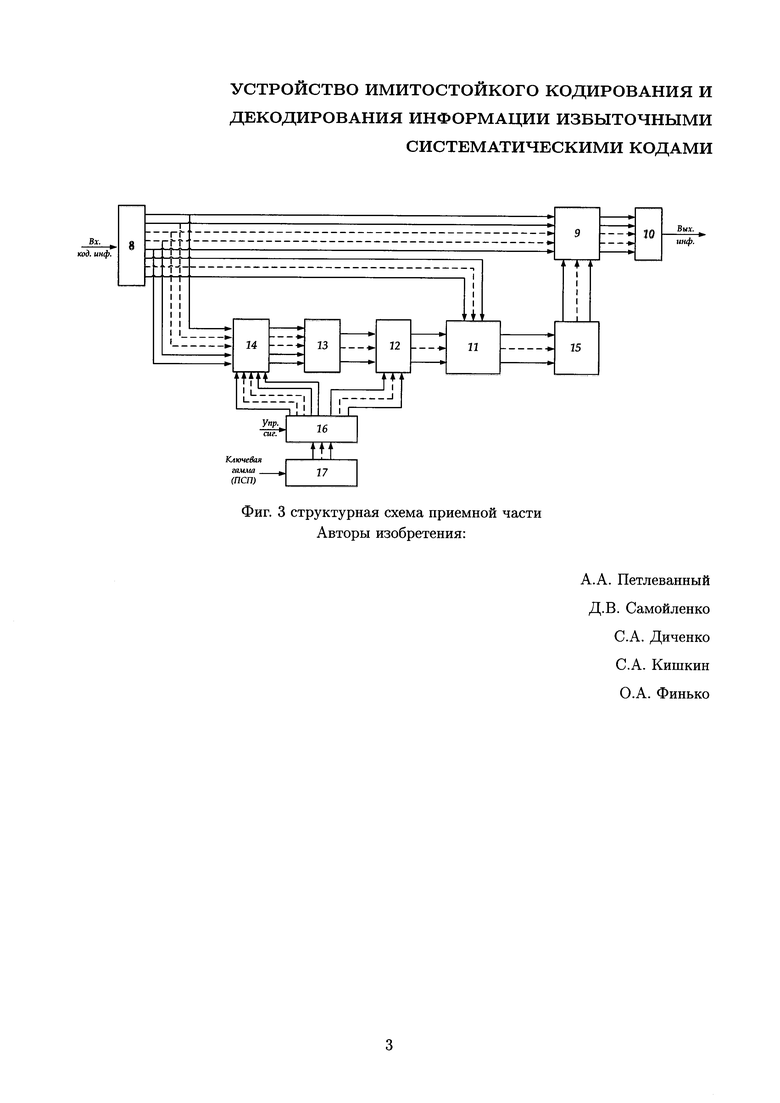

на фиг. 3 - структурная схема приемной части;

на фиг. 4-6 - действующий макетный образец разрабатываемого устройства.

Устройство имитостойкого кодирования и декодирования информации избыточными систематическими кодами содержит на передающей стороне (фиг. 1) канал кодирования, содержащий коммутатор 1 разделения ветвей, коммутатор 2 объединения ветвей, блок сумматоров 3 по модулю два, кодер 4, блок сумматоров 5 по модулю два, блок распределения гаммы 6, а также регистр 7 ключевой гаммы, и на приемной стороне устройство содержит канал декодирования, содержащий коммутатор 8 разделения ветвей, корректор ошибок 9, коммутатор 10 объединения ветвей, первый блок сумматоров 11 по модулю два, второй блок сумматоров 12 по модулю два, кодер 13, третий блок сумматоров 14 по модулю два, анализатор 15 синдромной последовательности, блок распределения гаммы 16, регистр 17 ключевой гаммы.

Устройство работает следующим образом.

Подлежащая передаче входная информация поступает в коммутатор 1 разделения ветвей, в котором происходит декомпозиция на информационные подпотоки. С выхода коммутатора 1 разделения ветвей информационные подпотоки поступают на вход коммутатора 2 объединения ветвей и на первую группу входов блока сумматоров 3 по модулю два, на вторую группу входов которого, через первую группу выходов блока 6 распределения гаммы, поступает k-разрядный блок гаммы, выработанный регистром 7 ключевой гаммы для канала кодирования, при этом длина блока гаммы соответствует количеству символов информационного подпотока. С выходов блока сумматоров 3 по модулю два зашифрованные символы информационного подпотока поступают на входы кодера 4 канала кодирования. В кодере 4 из зашифрованных информационных символов формируются проверочные символы, объединяемые в проверочные последовательности. Процесс формирования проверочных последовательностей осуществляется на основании выбранных порождающих полиномов систематических кодов канала кодирования. Полученные проверочные последовательности с выходов кодера 4 поступают на первую группу входов блока сумматоров 5 по модулю два, на вторую группу входов которого через вторую группу выходов блока 6 распределения гаммы поступает поступает r-разрядный блок гаммы, выработанный регистром 7 ключевой гаммы для канала кодирования, при этом длина блока гаммы соответствует количеству символов проверочной последовательности. Полученные зашифрованные проверочные последовательности с выхода блока сумматоров 5 по модулю два поступают на один из входов коммутатора 2 объединения ветвей, который формируют выходную кодовую последовательность. С выхода коммутатора 2 объединения ветвей кодовая последовательность поступает в канал связи.

На приемной стороне принятая кодовая последовательность поступает на вход коммутатора 8 разделения ветвей канала декодирования, с выхода которого символы информационных подпотоков поступают одновременно на первый вход корректора 9 ошибок и на первую группу входов блока сумматоров 14 по модулю два, на вторую группу входов которого, через первую группу выходов блока 16 распределения гаммы, поступает поступает k-разрядный блок гаммы, выработанный регистром 17 ключевой гаммы для канала кодирования. Вновь сформированная зашифрованная последовательность информационных симоволов с выхода блока сумматоров 14 по модулю два поступает на входы кодера 13, в котором формируются проверочные символы, объединяемые в проверочные последовательности.

Сформированная проверочная последовательность с выходов кодера 13 поступает на первую группу входов блока сумматоров 12 по модулю два, на вторую группу входов которого через вторую группу выходов блока 16 распределения гаммы поступает поступает r-разрядный блок гаммы, выработанный регистром 17 ключевой гаммы, с выхода которого зашифрованная проверочная последовательность поступает на первую группу входов блока сумматоров 11 по модулю два, на вторую группу входов которого с выхода коммутатора 8 разделения ветвей поступает принятая зашифрованная проверочная последовательность, где при суммировании по модулю два указанных последовательностей происходит формирование синдромной последовательности характеризующей преднамеренные (имитирующие действия злоумышленника) и непреднамеренные помехи в канале связи. С выходов блока сумматоров 11 по модулю два синдромная последовательность поступает на вход анализатора 15 синдромной последовательности, который проводит анализ этой последовательности. При этом нулевые символы в анализаторе ошибок являются признаком отсутствия преднамеренных (имитирующие действия злоумышленника) и непреднамеренных помех, в противном случае в анализаторе ошибок наблюдается присутствие ненулевых символов и информация с корректора ошибок данного канала декодирования стирается, дальнейшая обработка информации блокируется.

При отсутствии преднамеренных (имитирующие действия злоумышленника) и непреднамеренных помех (присутствие нулевых символов в анализаторе синдромной последовательности) с второго выхода корректора ошибок 9 символы информационных подпотоков поступают на входы коммутатора 10 объединения ветвей канала декодирования.

Отличительным признаком, характерным для преднамеренных (имитирующие действия злоумышленника) и непреднамеренных помех в канале связи, является несоответствие проверочной последовательности, сформированной кодером 13, блоком 16 распределения гаммы, регистром 17 ключевой гаммы и блоком сумматоров 14 по модулю два, и проверочной последовательности, сформированной кодером 4, блоком 6 распределения гаммы, регистром 7 ключевой гаммы и блоком сумматоров 5 по модулю два канала кодирования на передающей стороне.

Таким образом, предлагаемое устройство обеспечивает помехоустойчивость и имито-защищенность передаваемой по радиоканалам связи информации при заданной скорости передачи.

Заявленное изобретение может быть осуществлено с помощью средств и методов, описанных в доступных источниках информации. Это позволяет сделать вывод о соответствии заявленного изобретения признакам «промышленной применимости».

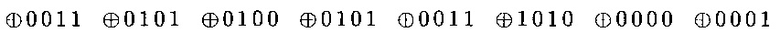

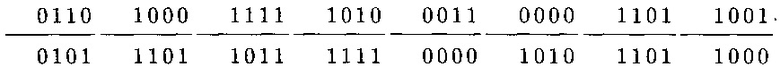

Пример. Порядок функционирования устройства имитостойкого кодирования и декодирования информации, основанного на расширенном коде Хэмминга (8, 4, 4). Для простоты понимания сущности предлагаемого решения процедура формирования помехоустойчивого кода Хэмминга (8, 4, 4) осуществляется с помощью порождающей матрицы.

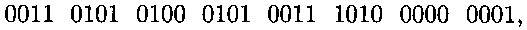

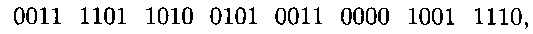

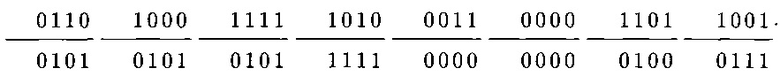

Пусьт М - информационный подпоток

и γ1 - ключевая гамма (ПСП), длины k=4

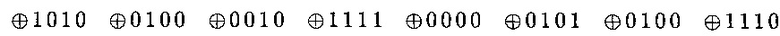

Процедура шифрования информационного подпотока примет вид:

тогда

тогда

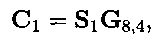

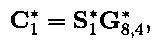

Формирование корректирующего кода (проверочных символов) на основании зашифрованного информационного подпотока осуществляется следующим образом:

где G8,4 - порождающая матрица кода Хэмминга.

Тогда

где (a1-a4) - информационные разряды, t0 - разряд четности, (t1-t3) - проверочные разряды.

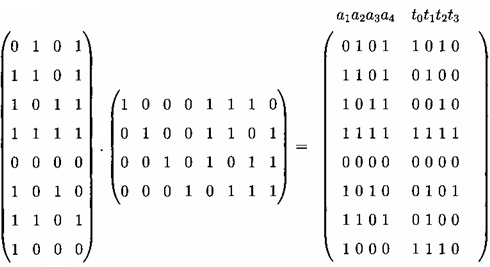

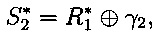

Пусть γ2 - ключевая гамма (ПСП), длины r=4

Процедура шифрования проверочных символов R1 определена выражением

тогда

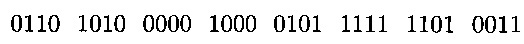

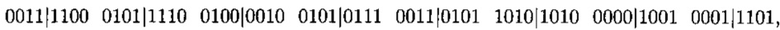

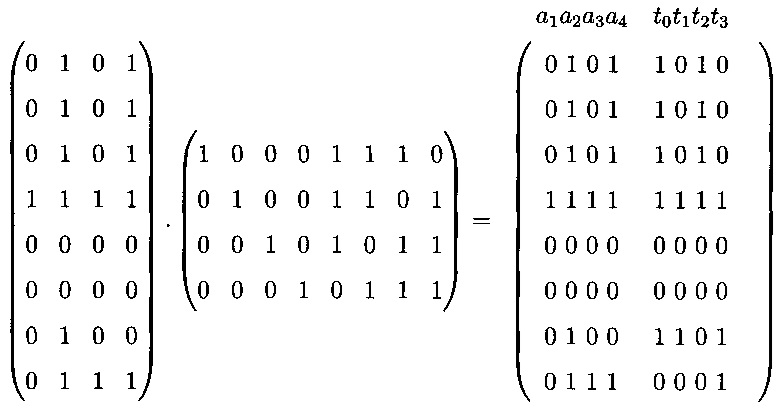

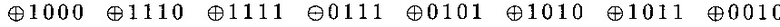

Кодовая последовательность (с зашифрованной проверочной частью)  передаваемая по каналу связи примет вид:

передаваемая по каналу связи примет вид:

где | - операция конкатенации.

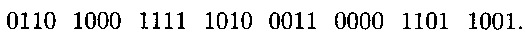

Принятая кодовая последовательность  , содержащая искажения от воздействия преднамеренных (имитирующих действий злоумышленника) и непреднамеренных помех:

, содержащая искажения от воздействия преднамеренных (имитирующих действий злоумышленника) и непреднамеренных помех:

где  - искаженный(е) разряд(ы), отличающиеся от исходных.

- искаженный(е) разряд(ы), отличающиеся от исходных.

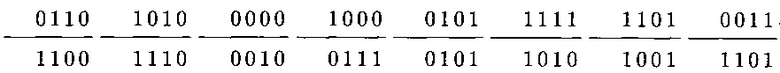

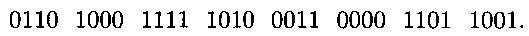

Тогда М* - принятый информационный подпоток

a γ1 - ключевая гамма (ПСП), длины k=4

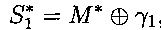

Процедура шифрования принятого информационного подпотока примет вид:

тогда

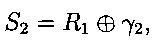

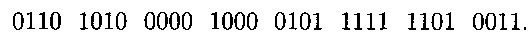

Соответственно формирование корректирующего кода (проверочных символов) на основании принятого зашифрованного информационного подпотока примет вид:

тогда

Пусть γ2 - ключевая гамма (ПСП), длины r=4

Процедура шифрования проверочных символов  примет следующий вид:

примет следующий вид:

тогда

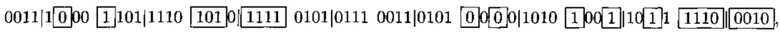

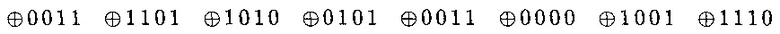

Анлиз принятой зашифрованной проверочной последовательности и выработанной:

)

)

Сформированная синдромная последовательность определяет присутствие (ненулевые символы синдрома) или отсутствие искажений (нулевые символы синдрома), вызванных преднамеренными (имитирующие действия злоумышленника) или непреднамеренными помехами в канале связи.

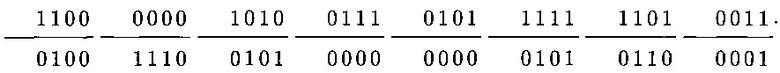

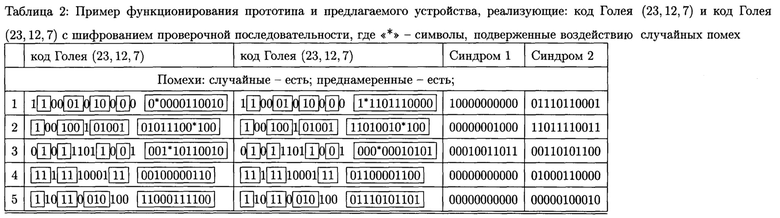

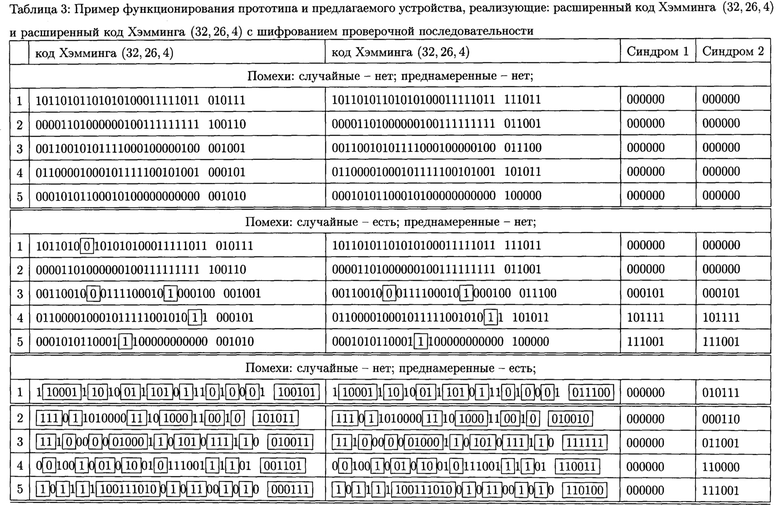

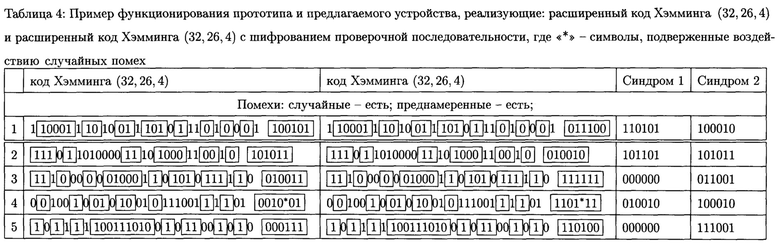

На фиг. 4-6 представлен действующий макетный образец разрабатываемого устройства, реализованный на отладочной плате LDM-K1986BE92QI. Результаты имитационного моделирования предлагаемого устройства представлены в таблицах 1-4.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ИСПОЛЬЗОВАНИЕМ БЛОЧНЫХ РАЗДЕЛИМЫХ КОДОВ, ОТ ИМИТИРУЮЩИХ ДЕЙСТВИЙ ЗЛОУМЫШЛЕННИКА | 2019 |

|

RU2738789C1 |

| Устройство для кодирования и декодирования двоичной информации сверточными кодами | 1982 |

|

SU1035819A1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| СПОСОБ И УСТРОЙСТВО ИМИТОУСТОЙЧИВОЙ ПЕРЕДАЧИ ИНФОРМАЦИИ ПО КАНАЛАМ СВЯЗИ | 2017 |

|

RU2669144C1 |

Изобретение относится к области электросвязи. Технический результат - обеспечение возможности защиты передаваемой по каналам связи двоичной информации от преднамеренных помех. Поставленная цель достигается тем, что информация, подлежащая передаче, поступает в канал кодирования. Процесс формирования защищенной проверочной последовательности осуществляется на основании поступившего в канал кодирования информационного подпотока, который подвергается процедуре зашифрования на соответствующих ключах. На основании полученной зашифрованной последовательности осуществляется формирование проверочной последовательности, которая в свою очередь также подвергается процедуре зашифрования. Сформированная зашифрованная проверочная последовательность объединяется с последовательностью информационного подпотока канала кодирования и поступает в канал связи. На приемной стороне из принятой кодовой последовательности осуществляется формирование информационной и порверочной последовательности канала декодирования. Далее осуществляется формирование зашифрованной проверочной последовательности на основании принятой информационной последовательности. Принятая зашифрованная проверочная последовательность канала декодирования и сформированная зашифрованная проверочная последовательность на приемной стороне формируют синдромную последовательность, структура которой соответствует присутствию (ненулевые символы синдрома) или отсутствию (нулевые символы синдрома) преднамеренных (имитирующие действия злоумышленника) или непреднамеренных помех в канале связи. Исходя из структуры синдромной последовательности производится обнаружение преднамеренных (имитирующие действия злоумышленника) или непреднамеренных помех. 6 ил., 4 табл.

Устройство для кодирования и декодирования двоичной информации сверточными кодами, содержащее на передающей стороне канал кодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и коммутатора объединения ветвей, а на приемной стороне - первый канал декодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и к первой группе входов корректора ошибок, к второй группе входов которого подключены выходы анализатора синдромной последовательности, к входу которого подключен выход первого сумматора по модулю два, при этом выходы корректора ошибок подключены к входам коммутатора объединения ветвей, отличающееся тем, что на передающей стороне введены блоки сумматоров по модулю два, блок распределения гаммы, регистр ключевой гаммы, при этом выходы регистра ключевой гаммы подключены к входу блока распределения гаммы, первая группа выходов которого подключена к второй группе входов первого блока сумматоров по модулю два, к первой группе входов которого подключен выходы коммутатора разделения ветвей, при этом выходы блока сумматоров по модулю два подключены к входам кодера, выходы которого подключены к первой группе входов второго блока сумматоров по модулю, к второй группе входов которого подключена вторая группа выходов блока распределения гаммы, при этом выходы второго блока сумматоров по модулю два подключены к соответствующему входу коммутатора объединения ветвей канала кодирования, а на приемной стороне введены блоки сумматоров по модулю два, блок распределения гаммы, регистр ключевой гаммы, при этом выходы регистра ключевой гаммы подключены к входам блока распределения гаммы, первая группа выходов которого подключена к второй группе входов третьего блока сумматоров по модулю два, к первой группе входов которого подключены выходы коммутатора разделения ветвей, выходы третьего блока сумматоров по модулю два подключены к входам кодера, выходы которого подключены к первой группе входов второго блока сумматора по модулю, к второй группе выходов которого подключена вторая группа выходов блока распределения гаммы, при этом выход второго блока сумматоров по модулю два подключен к первой группе входов первого блока сумматоров по два, к второй группе входов которого подключены соответствующие выходы коммутатора разделения ветвей, выходы первого блока сумматоров по модулю два подключены к входам анализатора синдромной последовательности, выходы которого подключены к второй группе входов корректора ошибок, выходы которого подключены к соответствующим входам коммутатора объединения ветвей канала декодирования.

| УСТРОЙСТВО И СПОСОБ ДЛЯ СВЕРТОЧНОГО КОДИРОВАНИЯ В ЦИФРОВОЙ СИСТЕМЕ | 1999 |

|

RU2214677C2 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| ВЫКЛЮЧАТЕЛЬ ЭЛЕКТРИЧЕСКОГО ТОКА | 1929 |

|

SU17471A1 |

| WO 00/41316 A, 13.07.2000 | |||

| CN 103746711 A, 23.04.2014 | |||

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2017-10-24—Публикация

2016-07-26—Подача