1

(21)4418361/24-09

(22)04.04.88

(46) 23.04.90. Бюл. № 15

(71)Куйбышевский электротехнический институт связи

(72)И.С.Брайнина и В.Н.Стрельников

(53)621.395.44 (088.8)

(56)Патент ГДР № 214272, кл. Н 04 Q 1/457, 1985.

(54)ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК МНОГОЧАСТОТНОГО КОДА

(57)Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости и упрощение цифрового группового приемника многочастотного кода. Он содержит блок задающих г-ров 1, коммутатор 2 адресов, блок оперативной памяти 3,формирователь 4 огибающей сигнала,эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 5, эл-т ИЛИ 6,счетчик-дешифратор 7 длины пачки,формирователь 8 знака пачки, формирователь 9 сигнала смены знака, блок задержки 10, счетчик-дешифратор 11 интервала между пачками, блоки 12 и 17 эл-тов И,блок счетчиков 13 среднего интервала, блок счетчиков 14 разноса частот, обнаружитель 15 кода и шифратор 16 кода. Цель достигается за счет осуществления одноканального приема многоканального сигнала.2 ил.

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости и упрощение цифрового группового приемника многочастотного кода. Он содержит блок задающих генераторов 1, коммутатор 2 адресов, блок оперативной памяти 3, формирователь 4 огибающей сигнала, элемент Исключающее ИЛИ 5, элемент ИЛИ 6, счетчик-дешифратор 7 длины пачки, формирователь 8 знака пачки, формирователь 9 сигнала смены знака, блок задержки 10, счетчик-дешифратор 11 интервала между пачками, блоки элементов И 12 и 17, блок счетчиков 13 среднего интервала, блок счетчиков 14 разноса частот, обнаружитель 15 кода и шифратор 16 кода. Цель достигается за счет осуществления одноканального приема многоканального сигнала. 2 ил.

(S

с

Фиг.1

Изобретение относится к радиотехнике и связи и может быть использовано в устройствах приема сигналов набора номера в спектре тональных час- тот, например, кодом 2 из 6,передаваемых в составе группового 32-ка- нального цифрового потока со скоростью 102 к бит/с с дельта-модуляцией и слоговым компандированием.

Целью изобретения является повышение помехоустойчивости и упрощение устройства за счет осуществления од- ноканального приема многоканального сигнала.

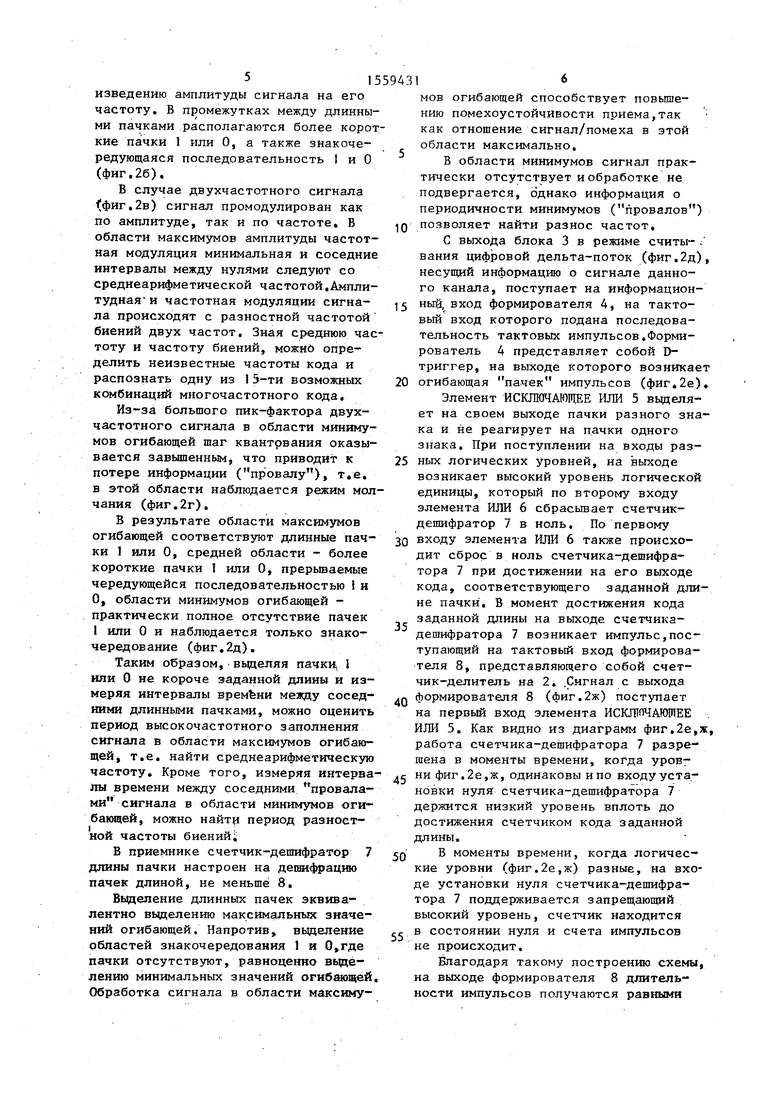

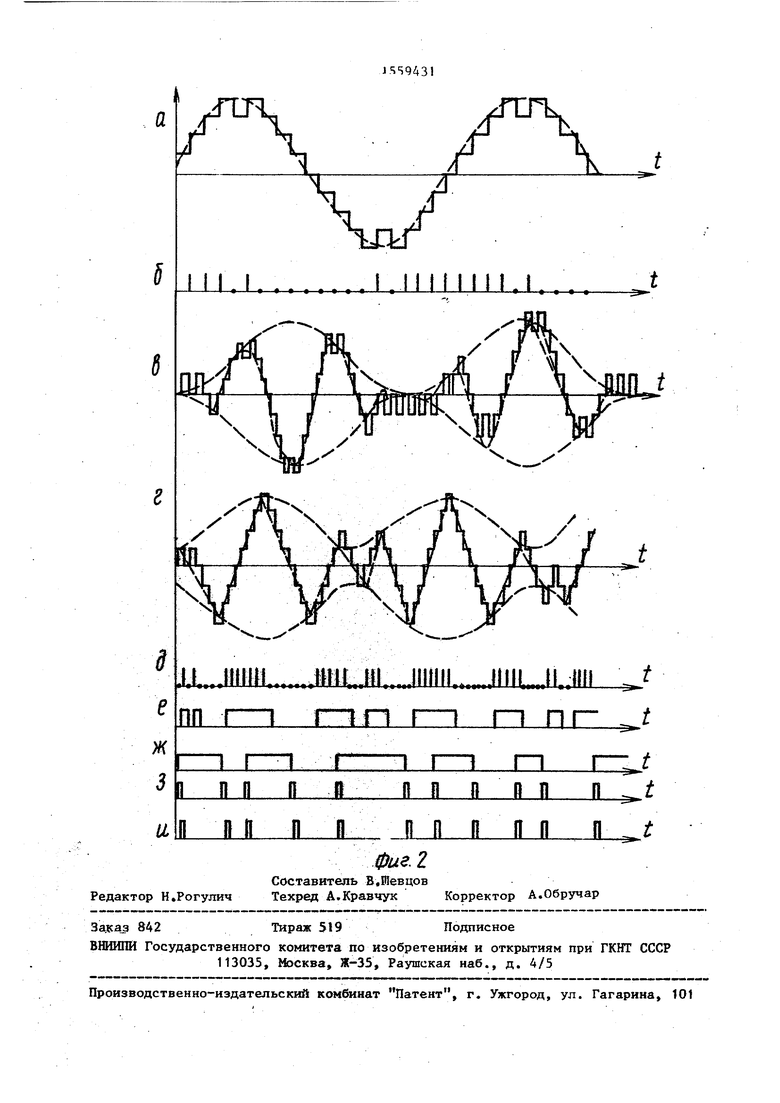

На фиг.1 представлена структур-; ная электрическая схема цифрового группового приемника многочастотного кода; на фиг.2 - эпюры напряжений, поясняющие работу приемника.

Приемник содержит блок задающих генераторов, коммутатор 2 адресов, блок 3 оперативной памяти,формирователь 4 огибающей сигнала,элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, элемент ИЛИ 6 счетчик-дешифратор 7 длины пачки, формирователь 8 знака пачки, формирователь 9 сигнала смены знака,блок 10 за держки, счетчик-дешифратор 11 интервала между пачками, первый блок 12 элементов И, блок 13 счетчиков среднего интервала, блок 14 счетчиков разноса частот, обнаружитель 15 кода, шифратор 16 кода и второй блок 17 элементов И.

Приемник работает следующим образом.

На вход приемника, а именно на вход данных блока 3, поступает групповой цифровой поток с тактовой час- тотой 1024 кГц, сформированный путем уплотнения 32 дельта-модулированных сигналов многочастотного кода со скоростью передачи 32 к бит/с на канал. Сигналы многочастотного кода 2 из 6 передаются при наборе номера комбинациями из двух частот ряда 700, 900, 1100, 1300, 1500 и 1700 Гц в диапазоне уровней порядка 30 дБ с возможным перекосом уровней близко отстоящих частот до 3 дБ и далеко отстоящих частот до 10 дБ. Всего может существовать 15 различных комбинаций кода. Дельта-отсчеты каждого из 32-каналов передаются в групповом цифровом потоке последовательно.

Последовательность отсчетов группового цифрового дельта-потока записывается в блок 3 по мере поступле

,

5

0

5 0

о 45 о

5

ния в соответствующие каждому каналу адреса. Для формирования адресов используются сетки частот 512, 256, 128, 64, 32, 16, 8, 4, 2, 1, 0,5, 0,25 и 0,125 кГц, вырабатываемые в блоке 1 из тактовой частоты 1024 кГц.

Для цикловой синхронизации блока 1 на его второй вход поступает импульсная последовательность цикловой частоты 8 кГц.

Время обработки отрезка двухчас- тотного сигнала не должно превышать 10 мс.

Поскольку за время 8 мс должен завершиться полный цикл записи и считывания из блока 3 всей ранее записанной информации, каждый тактовый отрезок времени делится пополам, В первую половину времени происходит запись в блок 3 отсчета сигнала по мере его поступления в реальном масштабе времени по адресу очередного канала, а во вторую половину времени - считывание из блока 3 другого отсчета сигнала по адресу другого канала, который в данный отрезок вре- .мени подлежит обработке.

Для формирования нужных адресов блока 3 в режимах записи и считывания информации в приемнике используется коммутатор 2, управляемый по своему второму входу импульсами записи/считывания 0

В режиме считывания на выходе блока 3 появляется информация, записанная ранее по данному каналу, в виде пачек 1 (импульсов длительностью 0,5 мкс) с частотой 1024 кГц,либо в виде- пачек 0 (отсутствия импуль- ов). либо в виде чередующихся импульсов и пауз (фиг.26).

Как следует из фиг.2а, б, области нарастания сигнала (положительной производной) соответствует пачка 1, области убывания сигнала (отрицательной производной) - пачка 0, области экстремумов сигнала (малой производительности) - режим молчания - чередующихся последовательность импульсов и пауз.

Величина ступеньки квантования (фиг.-2а) в дельта-кодере с адаптивным слоговым компандированием устанавливается за время адаптации 10 мс, равное периоду основного тона речи. Адаптивный шаг определяется средним модулем производной сигнала, которая в свою очередь пропорциональна про-

изведению амплитуды сигнала на его частоту. В промежутках между длинными пачками располагаются более короткие пачки 1 или 0, а также знакочередующаяся последовательность 1 и О (фиг.26).

В случае двухчастотного сигнала {фиг.2в) сигнал промодулирован как по амплитуде, так и по частоте. В области максимумов амплитуды частотная модуляция минимальная и соседние интервалы между нулями следуют со среднеарифметической частотой,Амплитудная и частотная модуляпии сигнала происходят с разностной частотой биений двух частот. Зная среднюю частоту и частоту биений, можно определить неизвестные частоты кода и распознать одну из 15-ти возможных комбинаций многочастотного кода.

Из-за большого пик-фактора двухчастотного сигнала в области минимумов огибающей шаг квантрвания оказывается завышенным, что приводит к потере информации (провалу), т.е. в этой области наблюдается режим молчания (фиг.2г).

В результате области максимумов огибающей соответствуют длинные пачки 1 или 0, средней области - более короткие пачки 1 или 0, прерываемые чередующейся последовательностью I н О, области минимумов огибающей - практически полное отсутствие пачек 1 или 0 и наблюдается только знако- чередование (фиг.2д).

Таким образом, выделяя пачки, 1 или 0 не короче заданной длины и измеряя интервалы времени между соседними длинными пачками, можно оценить период высокочастотного заполнения сигнала в области максимумов огибающей, т.е. найти среднеарифметическую

частоту. Кроме того, измеряя шггерва- , ни фиг.2е,ж, одинаковы ипо входу уста - -

лы времени между соседними провалами сигнала в области минимумов огибающей, можно найти период разностной частоты биений,

В приемнике счетчик-дешифратор 7 длины пачки настроен на дешифрацию пачек длиной, не меньше 8.

Выделение длинных пачек эквивалентно выделению максимальных значений огибающей. Напротив, выделение областей знакочередования 1 и 0,где пачки отсутствуют, равноценно выделению минимальных значений огибающей. Обработка сигнала в области максиму50

55

новки нуля счетчика-дешифратора 7 держится низкий уровень вплоть до достижения счетчиком кода заданной длины.

В моменты времени, когда логические уровни (фиг.2е,ж) разные, на входе установки нуля счетчика-дешифратора 7 поддерживается запрещающий высокий уровень, счетчик находится в состоянии нуля и счета импульсов не происходит.

Благодаря такому построению схемы на выходе формирователя 8 длительности импульсов получаются равными

мов огибающей способствует повышению помехоустойчивости приема,так как отношение сигнал/помеха в этой области максимально.

В области минимумов сигнал практически отсутствует и обработке не подвергается, однако информация о периодичности минимумов (провалов) позволяет найти разнос частот,

С выхода блока 3 в режиме считы- . вания цифровой дельта-поток (фиг.2д), несущий информацию о сигнале данного канала, поступает на информацион5 ный, вход формирователя 4, на тактовый вход которого подана последовательность тактовых импульсов.Формирователь 4 представляет собой D- триггер, на выходе которого возникает

0 огибающая пачек импульсов (фиг.2е). Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 выделяет на своем выходе пачки разного знака и не реагирует на пачки одного знака. При поступлении на входы раз5 ных логических уровней, на выходе возникает высокий уровень логической единицы, который по второму входу элемента ИЛИ 6 сбрасывает счетчик- дешифратор 7 в ноль. По первому

0 входу элемента ИЛИ 6 также происходит сброс в ноль счетчика-дешифратора 7 при достижении на его выходе кода, соответствующего заданной длине пачки. В момент достижения кода заданной длины на выходе счетчика- дешифратора 7 возникает импульс,поступающий на тактовый вход формирователя 8, представляющего собой счетчик-делитель на 2. .Сигнал с выхода

Q формирователя 8 (фиг.2ж) поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5. Как видно из диаграмм фиг.2е,ж, работа счетчика-дешифратора 7 разрешена в моменты времени, когда уров5

- -

новки нуля счетчика-дешифратора 7 держится низкий уровень вплоть до достижения счетчиком кода заданной длины.

В моменты времени, когда логические уровни (фиг.2е,ж) разные, на входе установки нуля счетчика-дешифратора 7 поддерживается запрещающий высокий уровень, счетчик находится в состоянии нуля и счета импульсов не происходит.

Благодаря такому построению схемы, на выходе формирователя 8 длительности импульсов получаются равными

интервалам между соседними длинными пачками импульсов противоположного знака, При этом длинные пачки импуль сов одного и того же знака,прерываемые короткими пачками другого знака, на выходе формирователя, 8 не фиксируются.

Формирователь 9 выделяет соответственно передние и задние фронты импульсов с выхода формирователя 8 знака пачки (фиг.2з)«В момент смены знака пачки открьюается один из элементов И первого блока 12, номер которого К соответствует интервалу между пачками импульсов. Это обеспечивается счетчиком-дешифратором 11, на сметный вход которого поступают тактовые импульсы, В момент смены знака пачки через открытый К-й элемент И блока I2 информация со счетчика- дешифратора 11 переписывается в одновременный счетчик блока 13,накапливающий число интерваловsсодержащих К периодов тактовой частоты.После этого счетчик-дешифратор 11 обнуляется с выхода блока 10 импульсами (фигв2и «

Одновременно с информацией о среднем интервале между пачками в счетчи ках блока 14 накапливается информация о разностной частоте Это достигается путем подсчета счетчиками разноса частот числа провалов той или иной длительности, фиксируемых на выходах того или иного открытого элемента И блока 17„ Таким образом, более длинные интервалы между пачками импульсов должны быть отнесены к провалам в области минимумов двухчастотного сигнала (фиг,2в,г). Фиксируя длительности провалов, открывающих элемент И блока 17 и подсчитывая их количество счетчиками блока 14, можно оценить разнос частот.

Информация о среднем интервале между пачками с выходов блока 13 и о числе провалов заданной длительное ти с выходов блока 14 поступает в конце интервала времени анализа на обнаружитель 15. На одном из 15-ти выходов обнаружителя 15 появляется высокий логический уровень, пос тупающий на шифратор 16, В зависимости от адреса выхода обнаружителя 15, на котором появился высокий уровень, счетчик адреса шифратора 16 останавливается.

10

15

20

25

30

35

40

45

50

55

При этом на выходе шифратора 16 устанавливается четырехразрядный двоичный код, соответствующий номеру i одной из 15-ти передаваемых комбинаций. Формула изобретения

Цифровой групповой приемник много- частотного кода, содержащий блок задающих генераторов, блок счетчиков среднего интервала и блок счетчиков разноса частот, отличающий- с я тем, что, с целью повышения помехоустойчивости и упрощения приемника за счет осуществления однока- нального приема многоканального сигнала, введены коммутатор адресов, блок оперативной памяти,первый и второй блоки элементов И, обнаружитель кода, шифратор кода и последовательно соединенные формирователь огибающей сигнала, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ, счетчик-дешифратор длины пачки, формирователь знака пачки, формирователь сигналов смены знака, блок задержки и счетчик-дешифратор интервалов между пачками, первые и вторые выходы которого подключены к первым входам соответственно первого и второго блоков элементов И, вторые входы которых объединены и подключены к выходу формирователя сигналов смены знака, вход которого объединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а второй вход элемента ИЛИ соединен с выходом счетчика-дешифратора длины пачки, тактовый вход которого объединен с тактовыми входами шифратора кода, счетчика-дешифратора интервалов между пачками, формирователя огибающей сигнала, блока оперативной памяти и блока задающих генераторов, выходы которого через коммутатор адресов подключены к входам блока оперативной памяти, вход записи-считывания которого объединен с управляющим входом коммутатора адресов и подключен к первому управляющему выходу блока задающих генераторов, второй управляющий выход которого подключен к объединенным входам сброса блока счетчиков среднего интервала, блока счетчиков разноса частот и шифратора кода, входы которого через обнаружитель кода подключены к соответствующим выходам блока счетчиков среднего интервала и блока счетчиков разноса частот, причем выход блока оперативной памяти подключен к входу формирователя огибающей сигнала.

и

6

I I L L

Л...ШПИttHL-tn1ШШtilH.JI.IIH

ПП I t 1 П F I I П Г t

ж

I

1 П П П П

и

П if Я П И П П В П П П t

Редактор Н.Рогулич

фиг. г

Составитель В,Шевцов

Техред А.Кравчук Корректор А.Обручар

I Jl 1 111 J L

t

t

1

П П П П П

П

t

Авторы

Даты

1990-04-23—Публикация

1988-04-04—Подача