UnofipereHne (относится к вычислительной технике и мпжет быть исполь- -u.iBano лпя of MeHa информацией между двумя разноскоростньми устройствами.

Цель изобретения - повьшшние быстродействия устройства сопряжения при чтении информации за счет предварительной подготовки считываемой информации.

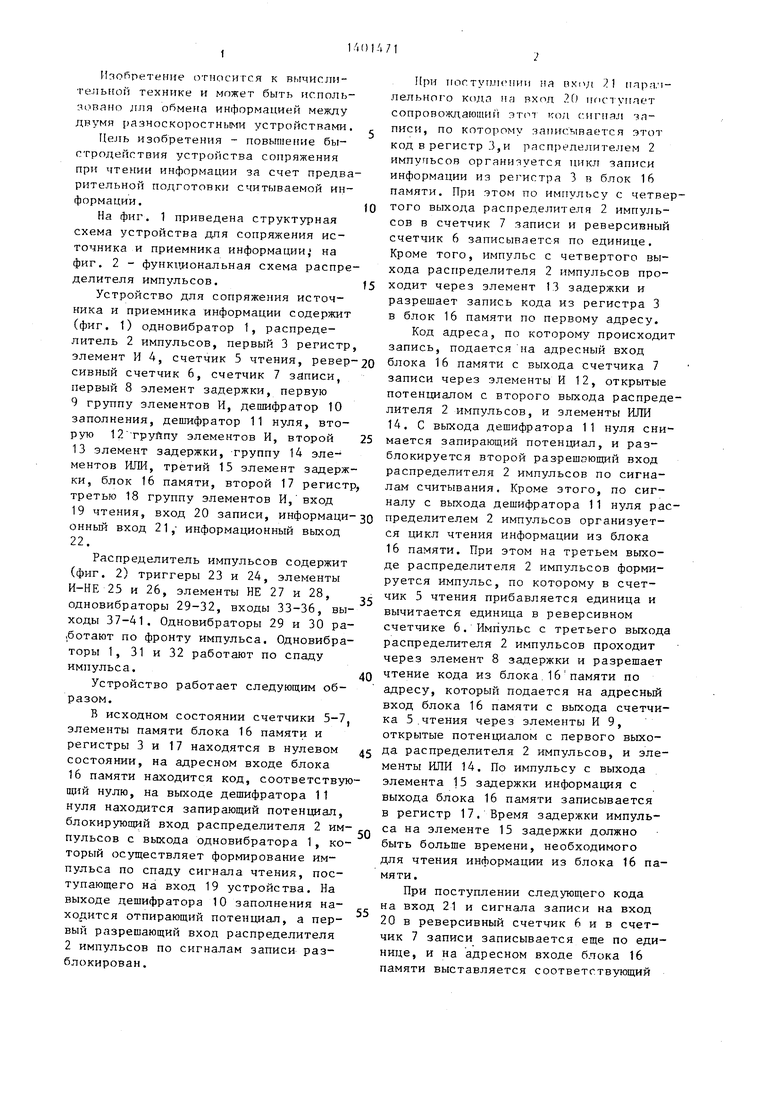

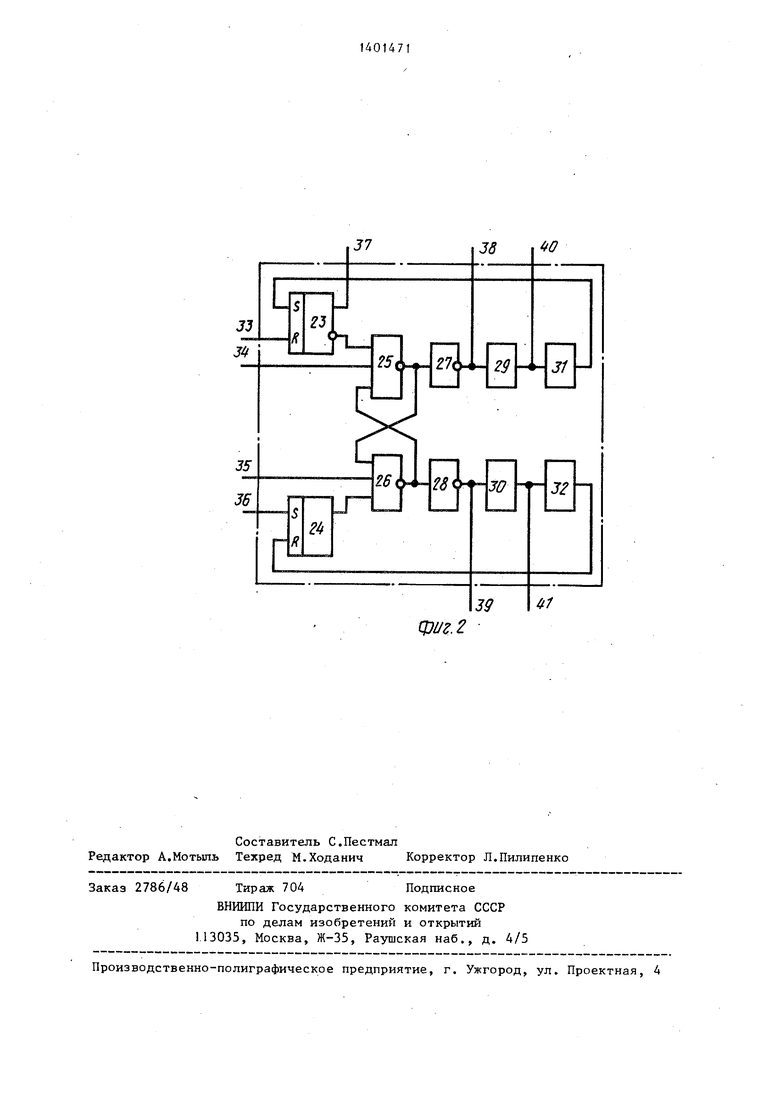

На фиг. 1 приведена структурная схема устройства для сопряжения источника и приемника информации, на фиг. 2 - функид1ональная схема распределителя импульсов.

Устройство для сопряжения источника и приемника информации содержит (фиг. 1) одновибратор 1, распределитель 2 импульсов, первый 3 регистр элемент И 4, счетчик 5 чтения, реверсивный счетчик 6, счетчик 7 записи, первый 8 элемент задержки, первую 9 группу элементов И, дешифратор 10 заполнения, дешифратор 11 нуля, вторую 12 труйпу элементов И, второй 13 элемент задержки, -группу 14 элементов ИЛИ, третий 15 элемент задержки, блок 16 памяти, второй 17 регистр третью 18 группу элементов И, вход 19 чтения, вход 20 записи, информационный вход 21 , информационный выход 22.

Распределитель импульсов содержит (фиг. 2) триггеры 23 и 24, элементы И-НЕ 25 и 26, элементы НЕ 27 и 28, одновибраторы 29-32, входы 33-36, выходы 37-41. Одновибраторы 29 и 30 ра- (ботают по фронту импульса, Одновибраторы 1, 31 и 32 работают по спаду импульса.

Устройство работает следующим образом.

В исходном состоянии счетчики 5-7 элементы памяти блока 16 памяти и регистры 3 и 17 находятся в нулевом состоянии, на адресном входе блока 16 памяти находится код, соответствующий нулю, на выходе дешифратора 11 нуля находится запирающий потенциал, блокирующий вход распределителя 2 импульсов с выхода одновибратора 1, который осуществляет формирование импульса по спаду сигнала чтения, поступающего на вход 19 устройства. На выходе дешифратора 10 заполнения находится отпирающий потенциал, а первый разрешающий вход распределителя 2 импульсов по сигналам записи разблокирован .

Q

5

0 5 о

. Q

g 0

5

При ггоступ.1(М1ии на nxivi плрп.ч- лельного кода на вход .() ипп упа(. т сопровождающий зт(п код сшгпэл записи, по которому записывается этот код в регистр 3,и распределителем 2 импуггьсов органи: |уется цикл записи информации из регистра 3 в блок 16 памяти. При этом по импульсу с четвертого выхода распределителя 2 импульсов в счетчик 7 записи и реверсивный счетчик 6 записывается по единице. Кроме того, импульс с четвертого выхода распределителя 2 импульсов проходит через элемент 13 задержки и разрешает запись кода из регистра 3 в блок 16 памяти по первому адресу.

Код адреса, по которому происходит запись, подается на адресный вход блока 16 памяти с выхода счетчика 7 записи через элементы И 12, открытые потенциалом с второго выхода распределителя 2 импульсов, и элементы ИЛИ 14. С выхода дешифратора 11 нуля снимается запирающий потенциал, и разблокируется второй раз-решнющий вход распределителя 2 импульсов по сигналам счить вания. Кроме этого, по сигналу с вькода дешифратора 11 нуля распределителем 2 импульсов организуется цикл чтения информации из блока 16 памяти. При этом на третьем выходе распределителя 2 импульсов формируется импульс, по которому в счетчик 5 чтения прибавляется единица и вычитается единица в реверсивном счетчике 6. Импульс с третьего выхода распределителя 2 импульсов проходит через элемент 8 задержки и разрешает чтение кода из блока.16 памяти по адресу, который подается на адресный вход блока 16 памяти с выхода счетчика 5.чтения через элементы И 9, открытые потенциалом с первого выхода распределителя 2 импульсов, и элементы ИЛИ 14. По импульсу с выхода элемента 15 задержки информация с выхода блока 16 памяти записывается в регистр 17. Время задержки импульса на элементе 15 задержки должно быть больше времени, необходимого для чтения информации из блока 16 памяти.

При поступлении следующего кода на вход 21 и сигнала записи на вход 20 в реверсивный счетчик бив счетчик 7 записи записывается еще по единице, и на адресном входе блока 16 памяти выставляется соответствующий

адрес, по которому записывается код с выхода регистра 3. Аналогичным образом происходит дальнейшее заполнение информацией блока 16 памяти, но цикл чтения распределителем 2 импульсов до прихода сигнала чтения на вход 19 больше не организуется.

Если на вход 19 приходит сигнал считывания до того, как произойдет заполнение блока 16 памяти, счетчика 7 и реверсивного счетчика 6 импульсами, управляющими записью,происходит чтение заранее подготовленной информации в регистре 17. При этом сигнал чтения проходит на первый вход группы 18 элементов И через элемент И 4, открытый разрешающим потенциалом с пятого выхода распределителя 2 имподготовка информации к очередному чтению. При завершении считывания всех записанных в блок 16 памяти кодов реверсивный счетчик 6 устанавливается в нулевое состояние, вследствие чего дешифратор 11 формирует сигнал, блокирующий распределитель 2 импульсов по сигналам чтения и запрещающий изменение состояния устройства по сигналам чтения, приходящим на вход 19. Одновременно сигнал с выхода дешифратора 11 может быть подан на приемник как сигнал запрета чте- ния (отсутствия информации для чтения) .

В случае, когда реверсивньп счетчик 6 заполняется импульсами, поступившими с четвертого выхода распреде

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1166125A1 |

Изобретение относится к области вычислительной техники и может быть использовано для обмена информацией между двумя разноскоростными устройствами. Целью изобретения является повышение быстродействия. .-Устройство содержит блок памяти, распределитель импульсов, реверсивный счетчик, счетчик записи, счетчик чтения, дешифратор заполнения, дешифратор нуля, два регистра, три группы элементов И, группу элементов ИЛИ, элемент И, одновибратор, три элемента задержки. 2 ил.

пульсов, и тем самым разрешает прохож- 20 лителя 2 импульсов, что свидетельстдение кода с выхода регистра 17 через группу 18 элементов И на выход устройства.

После окончания сигнала чтения на выходе одновибратора 1 по спаду вход- ного сигнала появляется импульс, по которому распределителем 2 импульсов организуется очередной цикл считывания информации из блока 16 памяти, при условии наличия разрешающего потенциа- ла с выхода дешифратора 11 нуля, т.е. наличия в блоке Т6 памяти информации. При этом на третьем выходе распреде- лителя 2 импульсов формируется импульс, по которому в счетчик 5 чтения прибавляется единица и вычитается единица в реверсивном счетчике 6. Импульс с третьего выхода распределителя 2 импульсов проходит через элемент 8 задержки и разрешает чтение кода из блока 16 памяти по адресу, который подается на адресный вход блока 16 памяти.с выхода счетчика 5 чтения через элементы И 9, открытые потенциалом с первого выхода распределителя 2 импульсов, и элементы ИЛИ 14. По импульсу с выхода элемента 15 задержки информация с выхода блока 16 памяти

записьтается в регистр 17 и, таким образом, подготавливается для считывания цо очередному сигналу чтения.

При поступлении следующего сигнала чтения на вход 19 устройства аналогично происходит чтение информа- ции из регистра 17 через группу 18 элементов И и затем осуществляется цикл чтения очередного кода из блока f6 памяти и запись в регистр 17, т.е.

5 О 5

5

0

g

вует о заполнении всего объема памяти блока 16 памяти, дешифратор 10 заполнения формирует сигнал, блокирующий распределитель 2 импульсов по первому входу и тем самым запрещающий дальнейшую запись информации. Первый сигнал, поступивший на вход 19, производит считывание информации и снимает блокировку устройства по входу 20, тем самым разрешает дальнейшую запись информации в устройство. Сигнал с выхода дешифратора 10 может быть выдан источнику как сигнал переполнения буферной памяти и блокировки вьщачи данных на вход 21.

В случае, когда на входы 19 и 20 поступают одновременно оба сигнала, распределителем 2 импульсов осуществляется разделение во времени цик- 0 лов записи и считывания и тем самым устранение сбойной ситуации.

При несовпадении во времени сигнат лов записи и чтения распределитель 2 импульсов работает следующим образом.

В исходном состоянии триггеры 23 и 24 находятся в нулевом состоянии. При записи информации в устройство на вход 36 поступает сигнал записи, а на вход 35 - сигнал с выхода дешифратора 10 заполнения. Триггер 24 устанавливается в единичное состояние. Так как триггер 23 находится в нулевом состоянии, а на входе 34, на который поступает сигнал с выхода дешифратора 11 нуля, находится нулевой уровень, то на выходе элемента И-НЕ 25 находится высокий уровень. При этом на выходе 39 тоже устанавливается высокий уровень. По фронту этого уровня формирователем 30 формируется импульс, который Поступает на выход 41 распределителя импульсов.

По спаду этого импульса формирователем 32 формируется импульс, который сбрасывает триггер 24. При этом на выходе элемента Й-НЕ 26 устанавливается высокий уровень,, а на выходе элемента НЕ 28 - низкий уровень Сигнал на выходе 39 распределителя импульсов используется для разрешения прохождения кода адреса с выхода счетчика 7 записи на адресный вход блока 16 памяти, а сигнал на выходе 41 - для записи информации в блок 16 памяти и в качестве входных импульсов счетчика 7 записи и реверсивного счетчика 6. После записи первого код в блок 16 памяти на вход 34 распределителя импульсов с выхода дешифратора 11 нуля приходит высокий уровень. Так как триггер 24 находится в нулевом состоянии, на выходе элемента И-НЕ 26 находится высокий уровень. При этом на выходе 38 распределителя импульсов устанавливается высокий уровень. По фронту этого уровня од- новибратором 29 формируется импульс, который поступает на выход 40 распределителя импульсов. По спаду этого импульса одновибратором 31 .формируется импульс, который устанавливает триггер 23 в единичное состояние. При этом на выходе элемента И-НЕ 25 устанавливается высокий уровень, а на выходе элемента НЕ 27 - низкий уровень.. Сигнал на выходе 38 используется для разрешения прохождения кода адреса с выхода счетчика 5 чтения на адресный вход блока 16 памяти а сигнал на выходе 40 - для чтения

50

информации из блока 16 памяти и в ка- g мента задержки, причем группа инфор- честве входных импульсов счетчика 5 чтения и реверсивного счетчика 6.

При одновременном поступлении импульсов на выходы 33 и 36 распределитель импульсов осуществляет поочередное формирование импульсов на выходах 37, 38, 40 и 39, 41. При этом триггер 23 сбрасывается, а триггер 24 устанавливается в единичное состояние. Схема взаимной блокировки на элементах И-НЕ 25 и 26 управляет очередностью формирования импульсов на выходах 37, 38, 40 и 39, 41. Так, например, при срабатьшании первым во

мационных входов первого регистра образует группу входов устройства для подключения к группе информационных вьгходов источника информации, первый тактовый вход распределителя импульсов соединен с входом записи, первого регистра и является входом устройства для подключения к выходу записи источника информации, при этом 55 группа информационных выходов первого регистра соединена с группой информационных входов блока памяти, группа адресных входов которого соединена с выходами элементов ИЛИ группы, первремени элемента И-НЕ 25 на его выходе появляется низкий уровень, ко- fropbrti блокирует элемент И-НЕ 26, на выходе которого появляется высокий уровень. При этом формируются импульсы на выходах 38 и 40, триггер 23 импульсом с выхода одновибратора 31 устанавливается в единичное состояние.

На выходе элемента И-НЕ 25 появляется высокий уровень и тем самым снимается блокировка с элемента И-НЕ 26. Так как триггер 24 находится в единичном состоянии, на выходе элемента

И-НЕ 2с появляется низкий уровень и формируются импульсы на выходах 39 и 41. Импульсом с выхода одновибратора 32 сбрасывается триггер 24, на этом работа распределителя импульсов заканчивается до поступления очередных импульсов на входы 33 и 36.

Таким образом, предлагаемое устройство обладает большим быстродействием при чтении информации из устройства за счет того, что считываемая информация готовится заранее и непосредственно в цикле чтения она считывается сразу из буферного регистра 17. Такой эффект достигается за

счет введения одновибратора,- формирующего импульс по сп.аду входного сигнала, элемента задержки, регистра, группы элементов И и новых связей.

35

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее счетчик чтения, счетчик записи, 40 реверсивный счетчик, дешифратор заполнения, дешифратор нуля, блок памяти, первый регистр, распределитель импульсов, две группы элементов И, группу элементов ИЛИ, элемент И, два эле

ента задержки, причем группа инфор-

мационных входов первого регистра образует группу входов устройства для подключения к группе информационных вьгходов источника информации, первый тактовый вход распределителя импульсов соединен с входом записи, первого регистра и является входом устройства для подключения к выходу записи источника информации, при этом группа информационных выходов первого регистра соединена с группой информационных входов блока памяти, группа адресных входов которого соединена с выходами элементов ИЛИ группы, пер

ные и BToptiif пхнл.ы KOTdpbix соединены соответстреннс) с выходами тлем«нтов И первой и BTopcifi первые входы которых соединены соответственно с группами выходов счетчик-т чтени и счетчика записи, вторые входы элементов И первой и второй групп соединены соответственно с первым и вторым -выходами распределителя импуль- сов, третий выход которого соединен с входом первого элемента задержки, .со счетным входом счетчика чтения и с входом вычитания реверсивного счетчика, группа выходов которого соединена с группами информационных входов дешифратора заполнения и дешифратора нуля, выходы которого соединены соответственно с первым и вторым разрешающими входами распредели- теля импульсов, четвертьш выход которого соединен с входом сложения реверсивного счетчика, со счетным входом счетчика записи и с входом второго элемента задержки,, выход которого соединен с входом записи блока памяти вход чтения которого соединен с выходом первого элемента задержки, отличающееся тем, что, с це5

0 5

лью попьииения Оме rpiiiKMici 11ИЧ . и ие.го впелены nTopofi рит ист11, трегт я груп- п а эл мент1и Ц, rrt i-nii элемент nnni p - ки, однов 5 1рятор, причем вход запуска однпвибраторя гоелинон с нерпьм входом элемента И и является входом устройства для подключения к выходу чтения источника информации, выходы элементов И третьей группы образуют группу выходов устройства для подключения к группе информационных входов приемника информации, при этом выход одновибратора соединен с вторым TaKi-oBbiM входом распределителя импульсов, пятый выход которого соединен с вторым входом элемента И, выход которого соединен с первыми входами элементов И третьей группы, вторые входы которых соединены с группой информационных выходов третьего регистра, группа информационных входов которого соединена с группой информационных выходов блока памяти, выход первого элемента задержки соединен с входом третьего элемента задержки, выход которого соединен с входом записи третьего регистра.

3d 0

«/

фиг. 2

| Устройство для сопряжения | 1983 |

|

SU1104498A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения источника и приемника информации | 1985 |

|

SU1309032A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-07—Публикация

1986-12-19—Подача