1309032

введены регистр 3, предназначенный значенный для разделения во времени для хранения входной информации, и циклов записи и считывания. 1 з.п. распределитель 6 импульсов, предна ф-лы, 3 ил.

Изобретение относится к вычислительной .технике и может быть использовано для обмена информацией между двумя разноскоростными устройствами.

Целью изобретения является повьше- ние достоверности функционирования устройства.

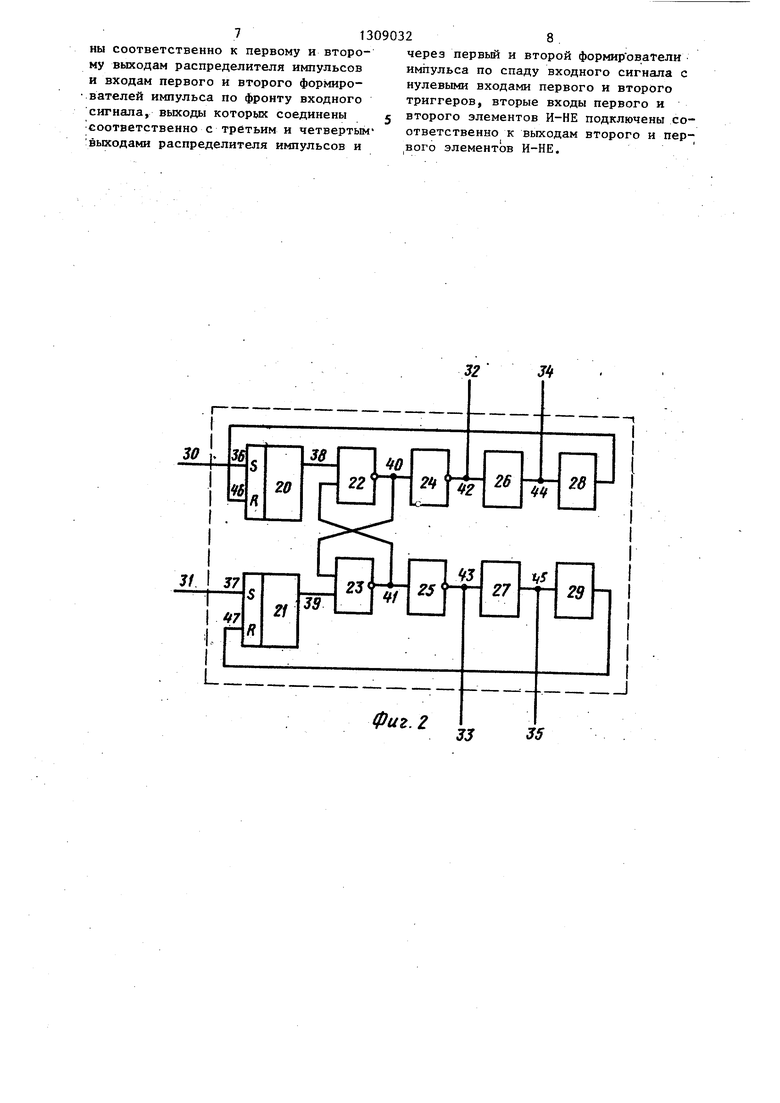

На фиг. 1 представлена блок-схема устройства; на фиг. 2 функциональная схема распределителя импульсов; на фиг. 3 - временная диаграмма работы распределителя импульсов.

Устройство (фиг. 1) содержит первый 1 и второй 2 элементы И, регистр 3, реверсивный счетчик 4, счетчик 5 чтения, распределитель 6 импульсов, счетчик 7 записи, первый 8 и второй 9 элементы задержки, дешифратор 10 заполнения, дешифратор 11 нуля, .первую 12 и вторую 13 группу элементов И, блок 14 памяти, группу элементов ИЛИ 15, 16 и 17 синхроимпульсов чтения и записи.устройства, информационные вход 18 и выход 19 устройства.

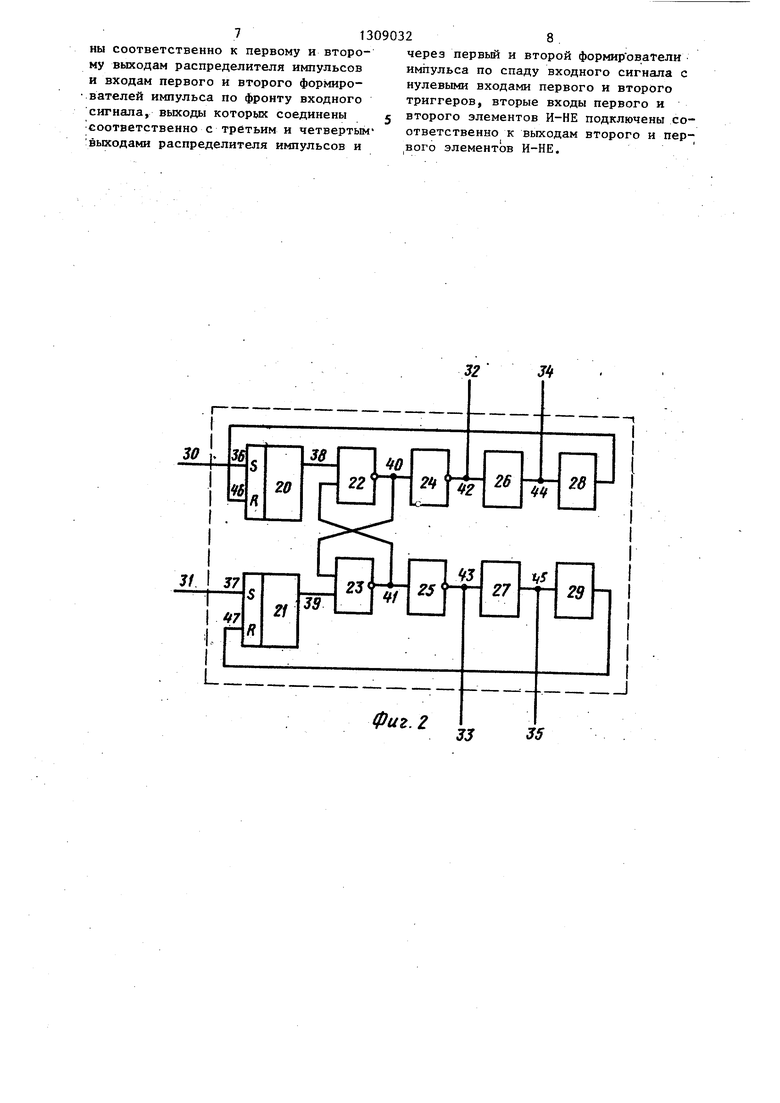

Распределитель импульсов (фиг.2) содержит первый 20 и второй 21 триггеры, первьш 22 и второй 23 элементы И-НЕ, первый 24 и второй 25 элеметы НЕ, первый 26 и второй 27 формиро ватели импульса по фронту входного сигнала, первый 28 и второй 29 формирователи импульса по спаду входног сигнала, первый 30 и второй 31 входы первый 32, второй 33, третий 34 и четвертый 35 выходы, входы 36-47 элементов распределителя.

Устройство работает следующим образом.4Q

В исходном состоянии счетчики 4,5, 7, элементы памяти блока 14 и регистр 3 находятся в нулевом состоянии, на адресном входе блока 14 находится потенциал, соответствующий О, на вы- 5 ходе дешифратора 11 находится запирающий потенциал, блокируклций элемент И 1, на выходе дешифратора 10

5

.

5

Q

5

находится потенциал ,открьшакядий эле.мент И 2.

Сигналом на входе 17 поступающий по входу параллельный код записывается в регистр 3 и модифицируются счетчик 7 и реверсивный счетчик 4. Кроме этого по сигналу на входе 17 распределитель 6 формирует импульс, который с выхода 35 проходит через элемент 9 задержки и разрешает запись кода из регистра 3 в блок 14 по первому адресу.

Код адреса, по которому происходит запись, подается на адресный вход блока 14 с выхода счетчика 7 через элементы И 13, открытые потенциалом с выхода 33 распределителя 6, и элементы ИЛИ 15. С выхода дептфратора 11 снимается запирающий потенциал, и разблокируется вход 16 для сигналов считывания.

При поступлении следующего кода на вход 18 и сигнала на вход 17 в реверсивный счетчик 4 и в счетчик 7 записывается еще по единице, и на адресный вход блока 14 поступает соответствующий адрес, по которому записывается код с выхода регистра 3. Аналогичным образом происходит дальнейшее заполнение информацией блока 14.

Если на вход 16 приходит сигнал считывания до того, как произойдет заполнение блока 14, счетчика 7 и реверсивного счетчика 4 импульсами, управляющими записью, из содержимого реверсивного счетчика 4 вычитается единица, в счеТчик 5 записывается единица. С выхода 34 распределителя 6 через элемент 8 задержки на вход блока 14 поступает импульс, по которому происходит считывание информации из блока 14 на выход 19 устройства. Причем код адреса, по которому происходит считывание-, подается с выхода счетчика 5 через элементы И 12, от- крытые потенциалом с выхода 32 распределителя 6, и элементы ИЛИ 15.

При поступлении следующего считы- вающего сигнала из содержимого реверсивного счетчика 4 вычитается еще единица, в счетчик 5 добавляется единица и на адресном вкоде блока 14 выставляется код второго адреса. Значение информации, записанной по этому адресу, считывается и поступает на выход 19 устройства. При завершении считывания всех записанных в па- мять кодов реверсивный счетчик 4 устанавливается в нулевое состояние, вследствие чего дешифратор 11 формирует сигнал, блокирующий элемент И 1 и запрещающий изменение состояния устройства по сигналам считывания, проходящим на вход 16. Одновременно сигнал с выхода дешифратора 11 может быть подан на приемник как сигнал запрета чтения (отсутствия информации для чтения).

В случае, когда реверсивный счетчик 4 заполняется импульсами, поступившими по входу 17, что свидетельствует о заполнении всего объема памяти блока 14, дешифратор 10 заполнения формирует сигнал, блокирующий элемент И 2 и тем самым запрещающий дальнейшую запись информации. Первый , сигнал, поступивший на вход 16, производит считывание информации по адресу с выхода счетчика 5 чтения и снимает блокировку устройства по входу 17, тем самым разрешая дальнейшую запись информации в устройство. Сигнал с выхода дешифратор 10 может быть вьвдан источнику как сигнал переполнения буферной памяти и блокировки выдачи данных на вход 18.В случае,, когда на входы 16 и 17 поступают одновременно оба сигнала для устранения сбойной ситуации распределитель 6 осуществляет разделение во время, циклов записи и считывания, При этом информация на входе 18 по сигналу на входе 17 записывается в регистр 3. После этого распределитель 6 формирует сигналы, по которым осуществляется запись информации из регистра 3 в блок 14, а затем чтение информации из блока 14 или, наоборот, сначала чтение информации, а затем запись информации из регистра .3 в блок 14. Порядок следования циклов запись-чтение зависит только от величин внутренних задержек в распределителе 6 и принципиального значения не имеет.

, «

Если в первую очередь организуется цикл записи, то устройство работает следующим образом. По сигналам,с выходов элементов И 1 и И 2 на втором выходе распределителя 6 формируется сигнал, по которому разрешается прохождение код адреса с выхода счетчика 7 через элементы И 13 и элементы ИЛИ.15 на адресный вход блока 14 памяти. Затем на вьтходе 35 распределителя 6 формируется сигнал, по которому информация из регистра 3 переписывается в блок 14. Сразу после записи информации распределитель 6 организует чтение информации. При этом на выходе 32 распределителя 6 формируется сигнал, по которому разрешается прохождение кода адреса с выхода сЧет- чика 5 через элементы И 12 и элементы ИЛИ 15 на адресный вход блока 14. Затем на выходе 34 формируется сигнал, по которому информация из блока 14 поступает на выход 19 устройства.

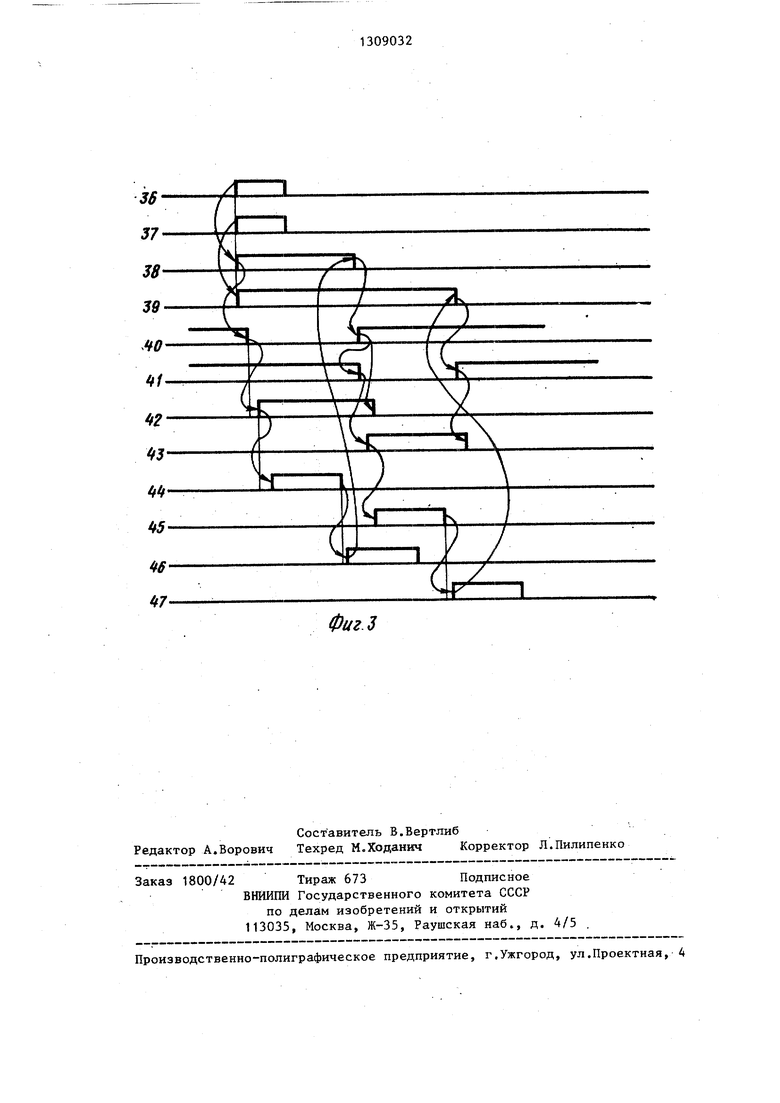

Распределитель 6 импульсов (фиг.2 и 3) работает следующим образом. В исходном состоянии триггеры 20 и 21 находятся в нулевом состоянии. На вход 30 поступает импульс чтения, который устанавливает триггер 20 в еди-, ничное состояние. Так как триггер 21 находится в нулевом состоянии, на выходе элемента И-НЕ 23 находится вьюо- кий уровень. При этом на выходе 32 распределителя 6 импульсов устанавливается высокий уровень. По фронту этого уровня формирователем 26 формируется импульс, который поступает на выход 34 распределителя 6. По спаду этого импульса формирователем 28 формируется импульс, который сбрасывает триггер 20. При этом на выходе элемента И-НЕ 22 устанавливается высокий уровень, а на выходе элемента НЕ 24 - уровень. Сигнал на выходе 32 используется для разрешения прохождения кода адреса на адресный вход блока 14, а сигнал на выходе 34.- для чтения информации из блока 14. При поступлении на вход 31 импульса записи триггер 21 устанавливается в единичное состояние. Так как триггер 20 находится в нулевом состоянии, на выходе элемента И-НЕ 22 находится высокий уровень. При этом на выходе 33 устанавливается высокий уровень. По фронту этого уровня формирователем 27 формируется импульс.

записи, выходы счетчика чтения и счеткоторый поступает на выход 35. По спаду этого импульса формирователем 29 формируется импульс, который сбра- сьшает триггер 21. При этом на выхо- дб элемента И-НЕ 23 устанавливается высокий уровень, а на выходе элемента НЕ 25 - низкий уровень. Сигнал на выходе 33 используется для разрешения прохождения кода адреса на адресный вход блока 14, а сигнал на выходе 35-10 ключения информационного входа прием- для записи информации в блок 14. При ника информации, входы записи и чте- одновременном поступлении импульсов чтения и записи на входы 30 и 31 распределитель 6 осуществляет поочередное формирование импульсов на выходах t5 ного счетчика соединен с входами де- 32, 34 и 33, 35. При этом триггеры 20 шифратора нуля и дешифратора заполне- и 21 устанавливаются в единичное сое- ния тояние. Схема взаимной блокировки на элементах И-НЕ 22 и 23 управляет очередностью формирования импульсов 20 на выходах 32, 34 и 33, 35. Так, например, при срабатывании первым во времени элемента И-НЕ 22 на его выходе появляется низкий уровень, который блокирует элемент И-НЕ 23, на вы- чающееся тем, что, с целью ходе которого появляется высокий уро- повышения достоверности функциониро- вень. При этом формируются импульсы

чика записи соединены соответственно с информационными входами элементов И первой и второй групп, выходы которых соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых соединены с адресным входом блока памяти, выход которого является выходом устройства для подния блока памяти соединены соответственно с выходами первого и второго элементов задержки, выход реверсив, выходы которых соединены соответственно с первыми вз одами первого и второго элементов И, вторые входы которых являются соответственно входами устройства для подключения выхода синхроимпульса чтения приемника информации и выхода синхроимпульса записи источника информации, о т л ивания устройства, в него введены регистр и распределитель импульсов, причем выходы первого и второго элена выходах 32 и 34, триггер 20 импульсом с выхода формирователя 28

устанавливается в нулевое состояние. 30 ментов И подключены соответственна

На вькоде элемента И-НЕ 22 появляется высокий уровень и тем сатлм снимается блокировка с элемента И-НЕ 23. Так как триггер 21 находится в единичном состоянии, на выходе элемента 35 элементов И первой и второй групп и

И-НЕ 23 появляется низкий уровень и формируются импульсы на выходах 33 и 35. Импульсом с выхода формирователя 29 Сбрасывается триггер 21 и на

этом работа распределителя 6 заканчи- 40 торого являются соответственно входа- вается до поступления очередных им- ми устройства для подключения информационного выхода и выхода синхроимпульса записи источника информации.

пульсов на входы 30 и 31.

Формула изобретения

45

1i Устройство для сопряжения ис- чающееся тем, что распреде- точника и приемника информации, содер- литель импульсов содержит два тригге- жащее блок памяти, первый и второй ра, два элемента И-НЕ, два злемен- элементы И, реверсивный счетчик, де- та НЕ, два формирователя импульса по шифратор заполнения и дешифратор нуля, фронту входного сигнала, два формиро- счетчик чтения, счетчик записи, две вателя импульса по спаду входного группы элементов И, группа элемен- сигнала, причем единичные входы пер- тов ИЛИ и два элемента задержки, при- вого и второго триггеров являются чем вь1ход первого элемента И соединен соответственно первым и вторым входа- с вычитающим входом реверсивного счет- с ми запуска распределителя импульсов.

чика и счетным входом счетчика чтения, выход второго элемента И соединен с суммирующим входом реверсивного счетчика-и счетным входом счетчика

записи, выходы счетчика чтения и счетключения информационного входа прием- ника информации, входы записи и чте- ного счетчика соединен с входами де- шифратора нуля и дешифратора заполне- ния чающееся тем, что, с целью повышения достоверности функциониро-

ключения информационного входа прием- ника информации, входы записи и чте- ного счетчика соединен с входами де- шифратора нуля и дешифратора заполне- ния чающееся тем, что, с целью повышения достоверности функциониро-

чика записи соединены соответственно с информационными входами элементов И первой и второй групп, выходы которых соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, выходы которых соединены с адресным входом блока памяти, выход которого является выходом устройства для подключения информационного входа прием- ника информации, входы записи и чте- ного счетчика соединен с входами де- шифратора нуля и дешифратора заполне- ния чающееся тем, что, с целью повышения достоверности функциониро-

ния блока памяти соединены соответственно с выходами первого и второго элементов задержки, выход реверсивключения информационного входа прием- ника информации, входы записи и чте- ного счетчика соединен с входами де- шифратора нуля и дешифратора заполне- ния чающееся тем, что, с целью повышения достоверности функциониро-

, выходы которых соединены соответственно с первыми вз одами первого и второго элементов И, вторые входы которых являются соответственно входами устройства для подключения выхода синхроимпульса чтения приемника информации и выхода синхроимпульса записи источника информации, о т л иключения информационного входа прием- ника информации, входы записи и чте- ного счетчика соединен с входами де- шифратора нуля и дешифратора заполне- ния чающееся тем, что, с целью повышения достоверности функциониро-

вания устройства, в него введены регистр и распределитель импульсов, причем выходы первого и второго элек первому и второму входам запуска распределителя импульсов, первый-чет- вертый выходы которог о подключены соответственно к управляющим входам

входам первого и второго элементов задержки, информационный вход блока памяти соединен с выходом регистра, информационный вход и синхровход ко

2. Устройство по п. 1, о т л ичающееся тем, что распреде- литель импульсов содержит два тригг ра, два элемента И-НЕ, два злемен- та НЕ, два формирователя импульса п фронту входного сигнала, два формир вателя импульса по спаду входного сигнала, причем единичные входы пер вого и второго триггеров являются соответственно первым и вторым вход ми запуска распределителя импульсов

а выходы подключены соответственно к первым входам первого и второго элементов И-НЕ, выходы которых через первый и второй элементы НЕ подключены соответственно к первому и второму выходам распределителя импульсов и входам первого и второго формирователей импульса по фронту входного сигнала, выкодь которых соединены соответственно с третьим и четвертым- выходами распределителя импульсов и

через первый и второй формир ователи импульса по спаду входного сигнала с нулевыми входами первого и второго триггеров, вторые входы первого и второго элементов И-НЕ подключены соответственно к выходам второго и первого элементов И-НЕ.

32

34

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1401471A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1562921A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Устройство управления | 1984 |

|

SU1171790A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1117627A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальное устройство управления вводом информации в микроЭВМ | 1984 |

|

SU1234844A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

Изобретение относится к области вычислительной техники и может быть использовано для обмена информацией между двумя разноскоростными устройст- :вами обработки данных в качестве буферной памяти; Целью изобретения является повышение достоверности функционирования за счет обеспечения работы устройства сопряжения при любом временном положении сигналов записи и счи- тьтания. Цель достигается тем, что в устройство, содержащее два элемента И 1,2, реверсивный счетчик 4, счетчик 5 чтения, счетчик 7 записи, элементы 8 и 9 задержки, дешифратор 10 заполнения, дешифратор 11 нуля, две группы элементов И 12, 13, блок 14 памяти, группу элементов ИЛИ 15, DO О СО о 00 ю -|

f9if t

г

j..

...I

иг.2

JJ

J5

Фиг.

| Устройство для сопряжения | 1978 |

|

SU723563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство сопряжения | 1982 |

|

SU1019428A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-07—Публикация

1985-12-02—Подача