Изобретение относится к автоматике и может быть использовано в цифровых системах автоматического регулирования станков, роботов и технологических установок.

Цель изобретения - повышение точности и расширение диапазона регулирования,

гистры, блок 7 оперативной памяти ошибки регулирования, блок 8 операт ной памяти управления, перый 9 и вт рой 10 блоки памяти произведений, второй 11 и третий 12 сумматоры.

Более высокая точность цифровог регулятора обеспечивается благодаря

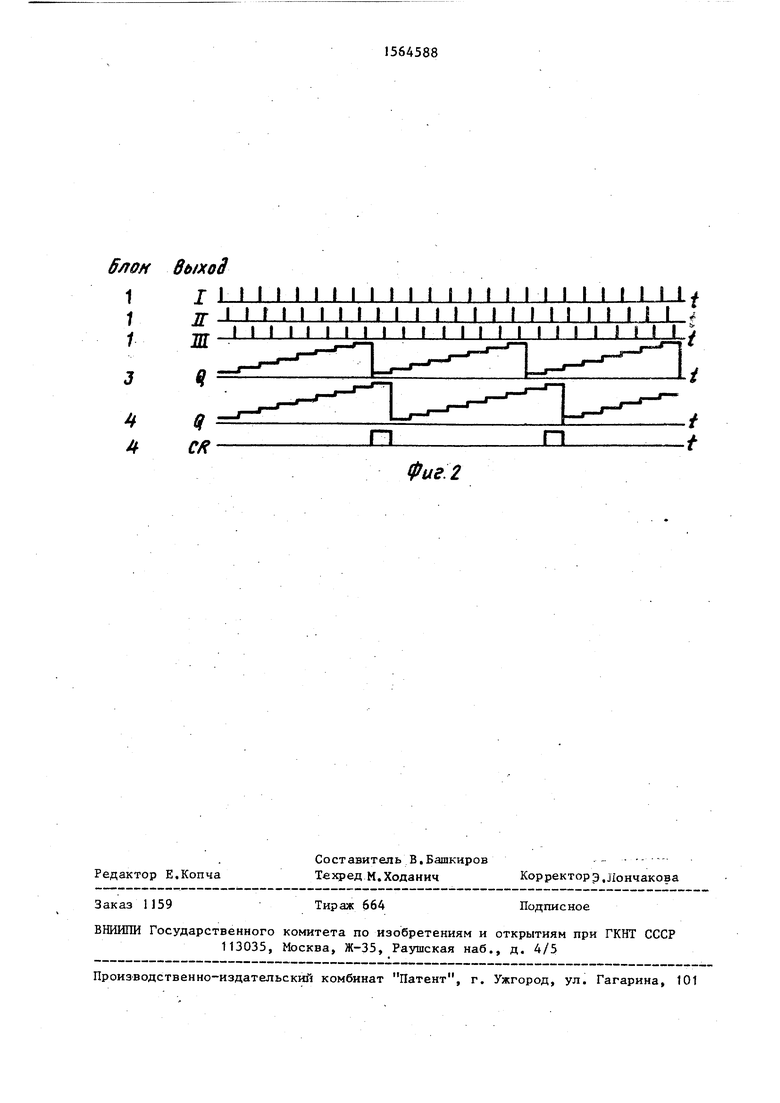

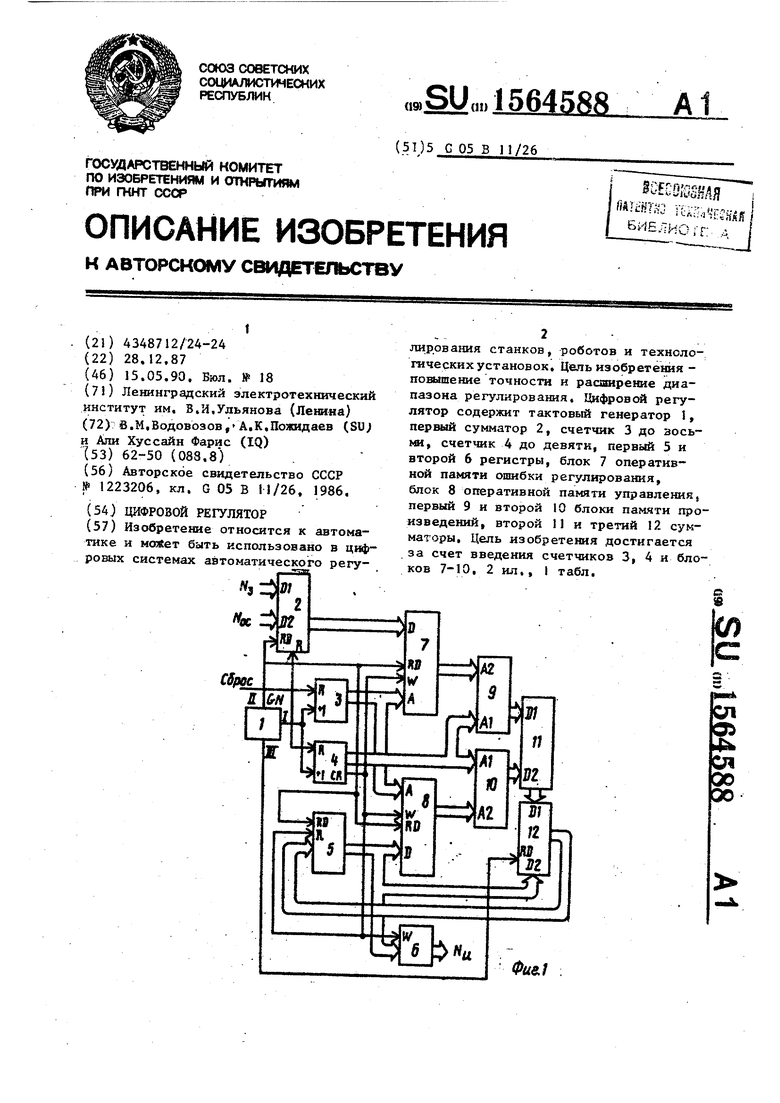

На фиг, 1 представлена функционалЬ-JQ новой организации работы цифрового

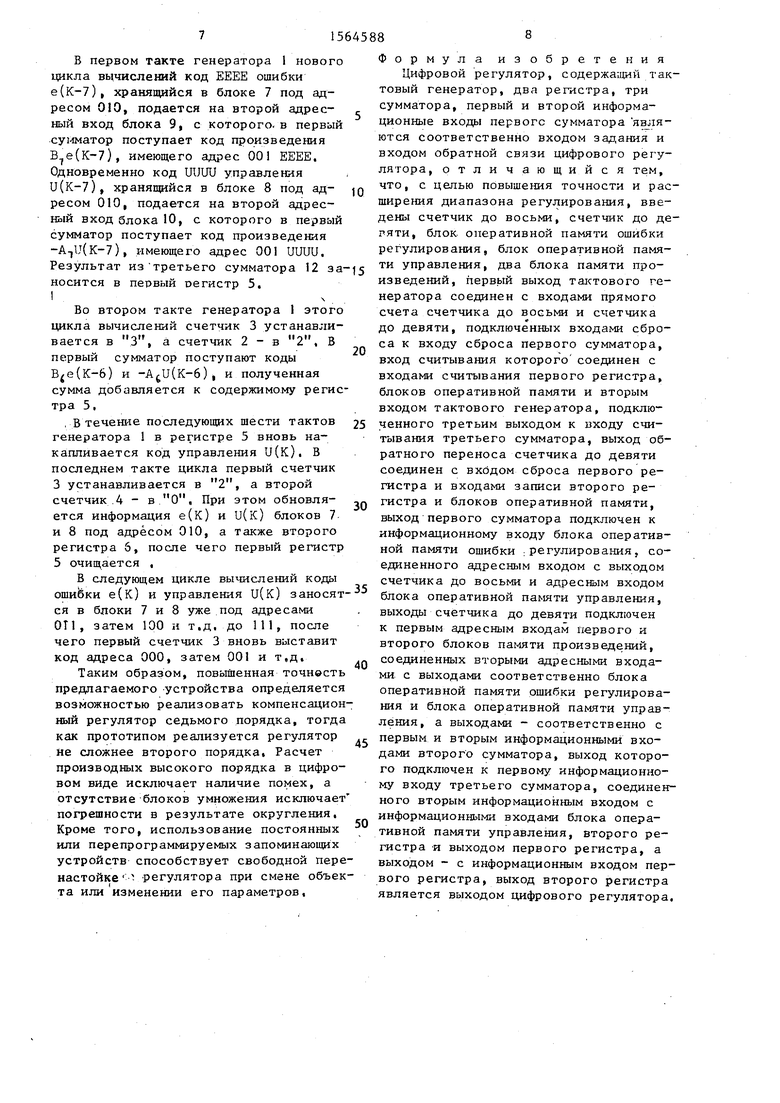

ная схема устройства; на фиг, 2 - временные диаграммы работы тактового генератора и счетчиков.

Цифровой регулятор (фиг, 1) содержит, тактовый генератор 1, первый сум- 15 матор 2, счетчик 3 до восьми, счетчик А до девяти, первый 5 и второй 6 ре регулятора. Каждый К-й цикл формиро вания очередного кода управления U(K здесь разбит на девять -тактов, Во время каждого такта происходит с мирование текущего значения кода с очередной парой слагаемых в соответ вии с уравнением,.

гистры, блок 7 оперативной памяти ошибки регулирования, блок 8 оперативной памяти управления, перый 9 и второй 10 блоки памяти произведений, второй 11 и третий 12 сумматоры.

Более высокая точность цифрового регулятора обеспечивается благодаря

регулятора. Каждый К-й цикл формирования очередного кода управления U(K) здесь разбит на девять -тактов, Во время каждого такта происходит суммирование текущего значения кода с очередной парой слагаемых в соответствии с уравнением,.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РЕГУЛЯТОР | 1992 |

|

RU2036502C1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1427386A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168940A1 |

| Устройство для быстрого преобразования Фурье | 1989 |

|

SU1633425A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

Изобретение относится к автоматике и может быть использовано в цифровых системах автоматического регулирования станков, роботов и технологических установок. Цель изобретения - повышение точности и расширение диапазона регулирования. Цифровой регулятор содержит тактовый генератор 1, первый сумматор 2, счетчик 3, до восьми, счетчик 4 до девяти, первый 5 и второй 6 регистры, блок 7 оперативной памяти ошибки регулирования, блок 8 оперативной памяти управления, первый 9 и второй 10 блоки памяти произведений, второй 11 и третий 12 сумматоры. Цель изобретения достигается за счет введения счетчиков 3, 4 и блоков 7-10. 2 ил.

и(К)В0е(к)+В1е(К-1)+В1е(К-2) + ...+В7е(К-7)-А,и(К-1) А.ги(К-2)-...-А7и{К-7),

которое, в свою очередь, соответст- вует передаточной функции f v UЈz) 60+6,. .. fl(Z)e(z) +А г +А27Лн...+А72-7

гдеU - код управления;25

a Nv-N0 - код ошибки;

Z - оператор дискретного

преобразования Лапласа;

В1, А ,, | коэффициент передаточной .A,J функции;

К -- номер цикла работы регулятора.

Получаемый в результате сложения код управления учитывает значения оши-35

бок и управлений за семь предшествую щих циклов работы регулятора, а отсутствие операций умножения исключает по гр ешно сти окру гле ния,

Широкий диапазон регулирования уст ройства обеспечивается благодаря возможности перепрограммирования коэффициента уравнения, хранящегося в посто янных запоминающих устройствах, в соответствии с фактическими параметрами объекта управления,

Устройство работает следующим образом,

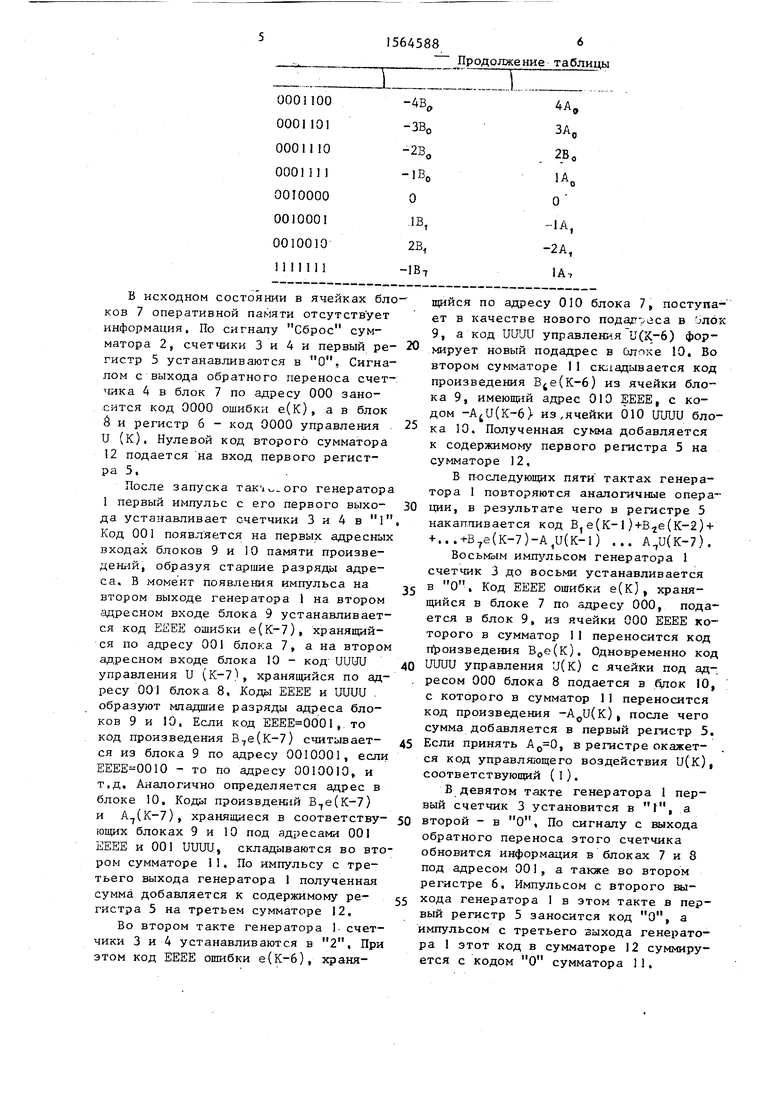

В ячейках блоков 9 и 10 памяти про изведений хранится следующая информация, представленная в таблице.

2В0 ЗВ0

4В0 5В0 6В0 В0 -8В0

- &

-6В0

-5В.

бок и управлений за семь предшествующих циклов работы регулятора, а отсутствие операций умножения исключает по гр ешно сти окру гле ния,

Широкий диапазон регулирования устройства обеспечивается благодаря возможности перепрограммирования коэффициента уравнения, хранящегося в постоянных запоминающих устройствах, в соответствии с фактическими параметрами объекта управления,

Устройство работает следующим образом,

В ячейках блоков 9 и 10 памяти произведений хранится следующая информация, представленная в таблице.

-2А0 -ЗА, -4А0 -5А0 -6А0 -7А0 8А0

7А0 6А0 5А

В исходном состоянии в ячейках блоков 7 оперативной памяти отсутствует информация. По сигналу Сброс сумматора 2, счетчики 3 и 4 и первый регистр 5 устанавливаются в О. Сигналом с выхода обратного переноса счетчика 4 в блок 7 по адресу 000 заносится код 0000 ошибки е(К), а в блок 8 и регистр б - код 0000 управления U (К), Нулевой код второго сумматора 12 подается на вход первого регистра 5.

После запуска так к.ого генератора 1 первый импульс с его первого выхода устанавливает счетчики 3 и 4 в 1 Код 001 появляется на первых адресных входах блоков 9 и 10 памяти произведений, образуя старшие разряды адреса, В момент появления импульса на втором выходе генератора 1 на втором адресном входе блока 9 устанавливается код ЕЕЕЕ ошибки е(), хранящийся по адресу 001 блока 7, а на втором адресном входе блока 10 - код UUUU управления U (К-7, хранящийся по адресу 001 блока 8, Коды ЕЕЕЕ и UUUU образуют младшие разряды адреса блоков 9 и 10. Если код , то код произведения В7е(К-7) считывается из блока 9 по адресу 0010001, если ЕЕЕЕ-0010 - то по адресу 0010010, и т.д. Аналогично определяется адрес в блоке 10, Коды произвдений В7е(К-7) и А7(К-7), хранящиеся в соответствующих блоках 9 и 10 под адресами 001 ЕЕЕЕ и 001 UUUU, складываются во втором сумматоре 11. По импульсу с третьего выхода генератора 1 полученная сумма добавляется к содержимому ре- гистра 5 на третьем сумматоре 12.

Во втором такте генератора 1 счетчики 3 и 4 устанавливаются в 2, При этом код ЕЕЕЕ ошибки е(К-6), храня

Продолжение таблицы

0

5

0

щийся по адресу 010 блока 7, поступает в качестве нового подар-у са в лиок 9, а код ULTJU управления U(K-6) формирует новый подадрес в бгпхе 10. Во втором сумматоре I1 складывается код произведения (К-б) из ячейки блока 9, имеющий адрес 010 ЕЕЕЕ, с кодом -AcU(K-6) из,ячейки 010 UUUU блока 10, Полученная сумма добавляется к содержимому первого регистра 5 на сумматоре 12,

В последующих пяти тактах генератора I повторяются аналогичные операции, в результате чего в регистре 5 накапливается код В,е(К-1)+В1е(К-2)+ + ...i-B7e(K-7)-A1U(K-l) ... А иСК-7).

Восьмым импульсом генератора 1 счетчик 3 до восьми устанавливается 5 в О. Код ЕЕЕЕ ошибки е(К), хранящийся в блоке 7 по адресу 000, подается в блок 9, из ячейки 000 ЕЕЕЕ которого в сумматор 11 переносится код произведения В0е(К), Одновременно код UUUU управления U(K) с ячейки под адресом 000 блока 8 подается з блок 10, с которого в сумматор 11 переносится код произведения -Аои(к), после чего сумма добавляется в первый регистр 5. Если принять , в регистре окажет- . ся код управляющего воздействия U(K), соответствующий (I).

В девятом такте генератора 1 первый счетчик 3 установится в Ч, а второй - в О, По сигналу с выхода обратного переноса этого счетчика обновится информация в блоках 7 и 8 под адресом 001, а также во втором регистре 6. Импульсом с второго выхода генератора 1 в этом такте в первый регистр 5 заносится код О, а импульсом с третьего выхода генератора 1 этот код в сумматоре 12 суммируется с кодом О сумматора 11.

0

5

0

В первом такте генератора 1 нового цикла вычислений код ЕЕЕЕ ошибки е(К-7), хранящийся в блоке 7 под адресом 010, подается на второй адресный вход блока 9, с которого, в первый сумматор поступает код произведения В7е(К-7), имеющего адрес 001 ЕЕЕЕ. Одновременно код UUUU управления U(K-7), хранящийся в блоке 8 под адресом 010, подается на второй адресный вход блока 10, с которого в первый сумматор поступает код произведения -A-,U(K-7), имеющего адрес 001 UUUU. Результат из третьего сумматора 12 за носится в первый регистр 5.

Во втором такте генератора 1 этого цикла вычислений счетчик 3 устанавливается в 3, а счетчик 2 - в 2, В первый сумматор поступают коды (К-Ь) и -AtU(K-6), и полученная сумма добавляется к содержимому регистра 5.

В течение последующих шести тактов генератора 1 в регистре 5 вновь накапливается код управления U(K). В последнем такте цикла первый счетчик 3 устанавливается в 2, а второй счетчик 4 - в О, При этом обновляется информация е(К) и U(K) блоков 7 и 8 под адресом 010, а также второго регистра 6, после чего первый регистр 5 очищается ,

В следующем цикле вычислений коды ошибки е(К) и управления U(K) заносят ся в блоки 7 и 8 уже под адресами ОТ1, затем 100 и т.д. до 111, после чего первый счетчик 3 вновь выставит код адреса 000, затем 001 и т.д.

Таким образом, повышенная точность предлагаемого устройства определяется возможностью реализовать компенсационный регулятор седьмого порядка, тогда как прототипом реализуется регулятор не сложнее второго порядка. Расчет производных высокого порядка в цифровом виде исключает наличие помех, а отсутствие блоков умножения исключает погрешности в результате округления, Кроме того, использование постоянных или перепрограммируемых запоминающих устройств способствует свободной пере настойке Л регулятора при смене объек та или изменении его параметров.

0

5

20

25

30

35

40

45

50

Формула изобретения

Цифровой регулятор, содержащий тактовый генератор, два регистра, три сумматора, первый и второй информационные входы первого сумматора являются соответственно входом задания и входом обратной связи цифрового регулятора, отличающийся тем, что, с целью повышения точности и расширения диапазона регулирования, введены счетчик до восьми, счетчик до де- гяти, блок оперативной памяти ошибки регулирования, блок оперативной памяти управления, два блока памяти произведений, первый выход тактового ге- нератора соединен с входами прямого счета счетчика до восьми и счетчика до девяти, подключенных входами сброса к входу сброса первого сумматора, вход считывания которого соединен с входами считывания первого регистра, блоков оперативной памяти и вторым входом тактового генератора, подключенного третьим выходом к входу считывания третьего сумматора, выход обратного переноса счетчика до девяти соединен с входом сброса первого регистра и входами записи второго регистра и блоков оперативной памяти, выход первого сумматора подключен к информационному входу блока оперативной памяти ошибки регулирования, соединенного адресным входом с выходом счетчика до восьми и адресным входом блока оперативной памяти управления, выходы счетчика до девяти подключен к первым адресным входам первого и второго блоков памяти произведений, соединенных вторыми адресными входами с выходами соответственно блока оперативной памяти ошибки регулирования и блока оперативной памяти управления, а выходами - соответственно с первым и вторым информационными входами второго сумматора, выход которого подключен к первому информационному входу третьего сумматора, соединенного вторым информационным входом с информационными входами блока оперативной памяти управления, второго регистра и выходом первого регистра, а выходом - с информационным входом первого регистра, выход второго регистра является выходом цифрового регулятора.

блок выход

1 j i i i i i i i i i i i i i i t i i i i I i i i i-if

1ж t 1 I I I I I I I 1 I 1 I I I I M I t I i I i i i i i i i i i i t i i i i i i i i i i i i I .y

Редактор Е.Копча

Составитель В.Башкиров Техред М.Ходанич

Заказ 1159

Тираж 664

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Фиг. 2

Корректорэ.Лончакова

Подписное

| Цифровой пропорционально-интегрально-дифференциальный регулятор | 1984 |

|

SU1223206A2 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-05-15—Публикация

1987-12-28—Подача