Изобретение относится к вычислительной технике и может быть использовано для автоматизации процесса комплексной отладки высокопроизводи- тельных микропрограммных ЭВМ.

Цель изобретения - повышение достоверности работы системы.

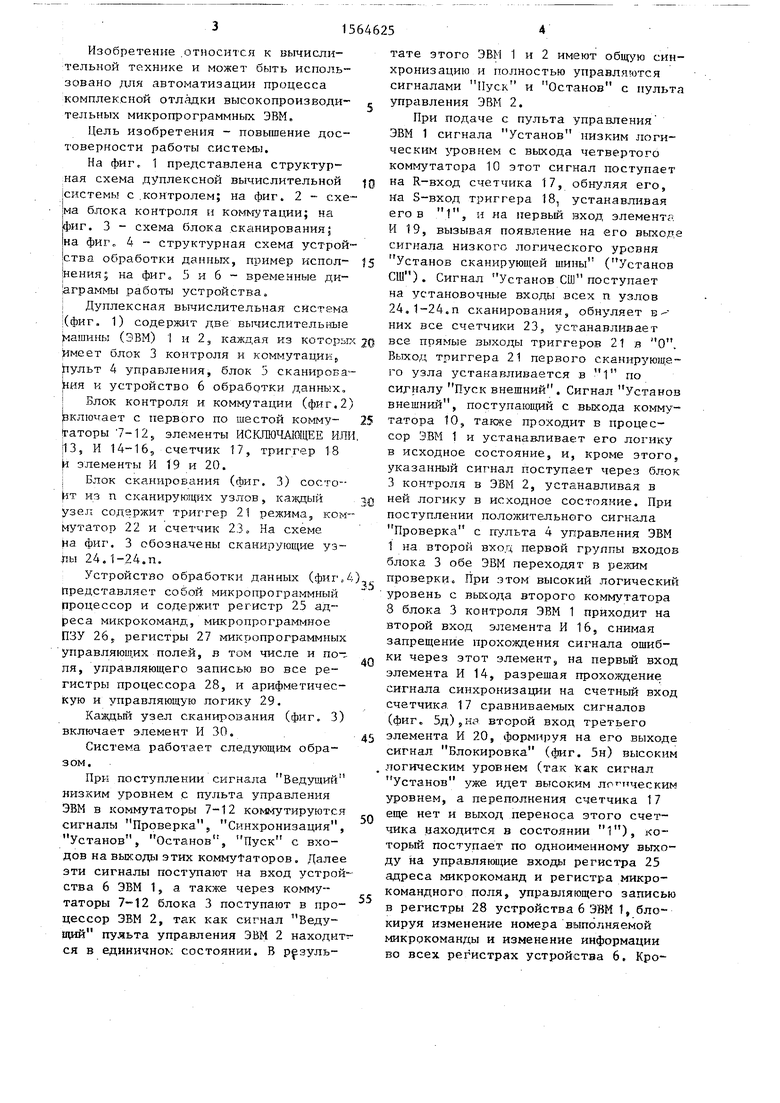

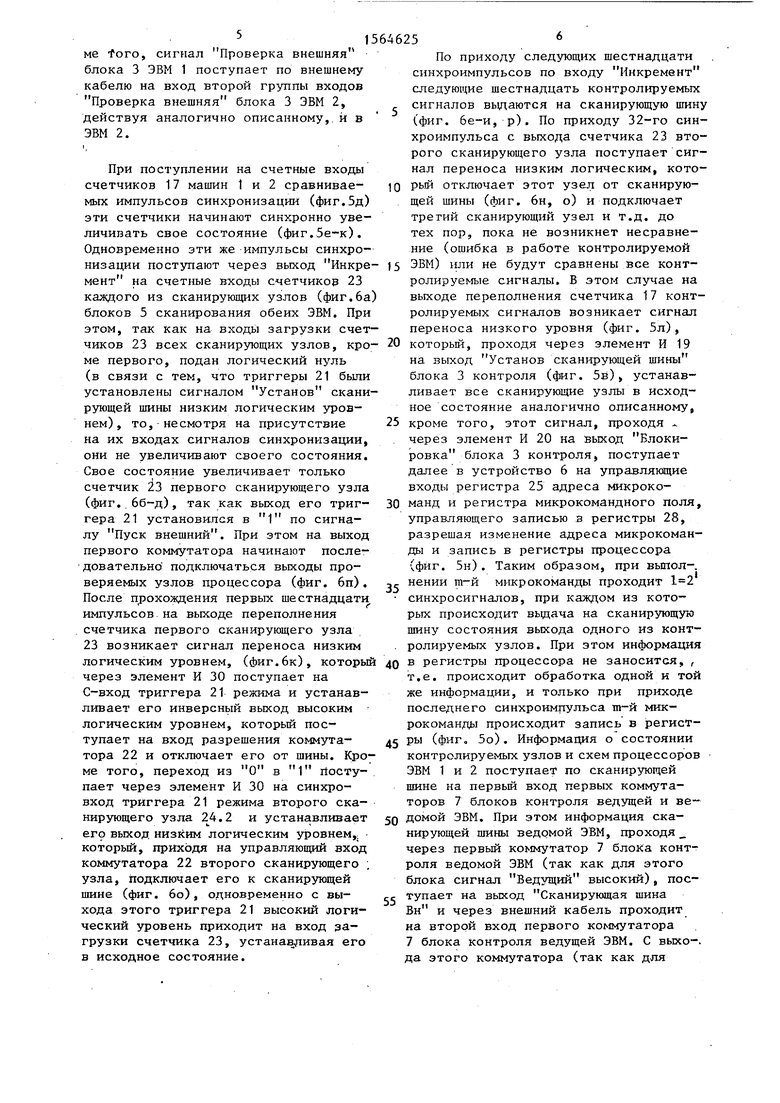

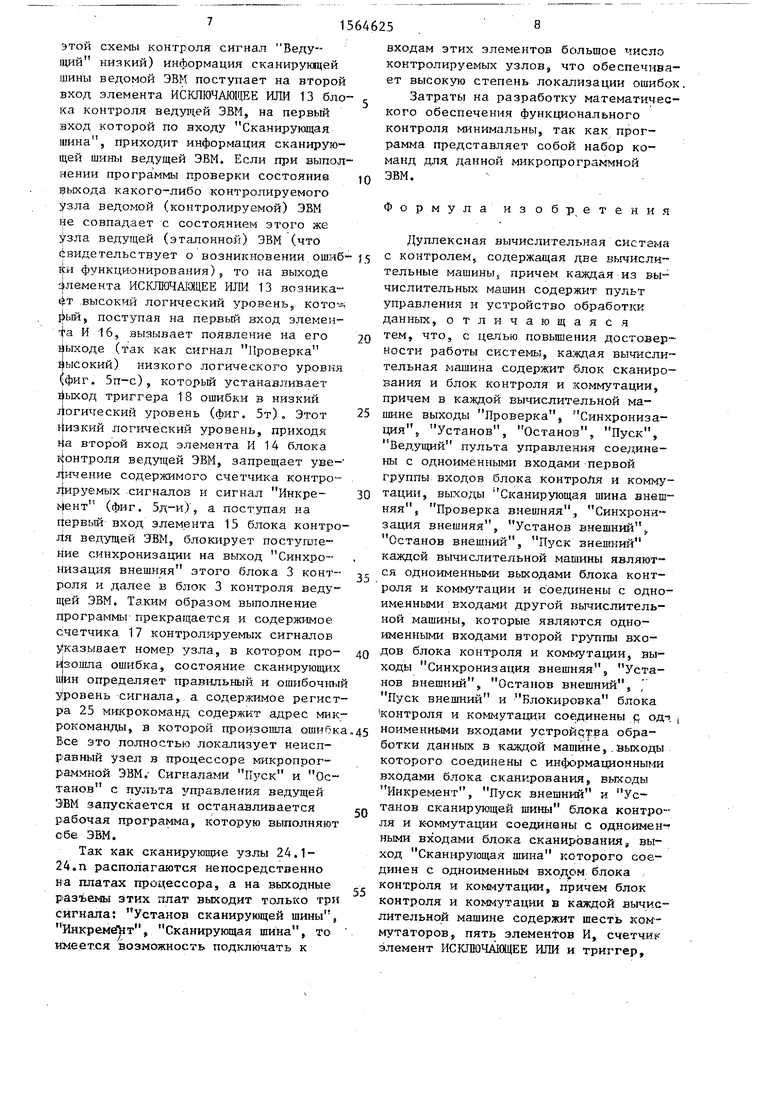

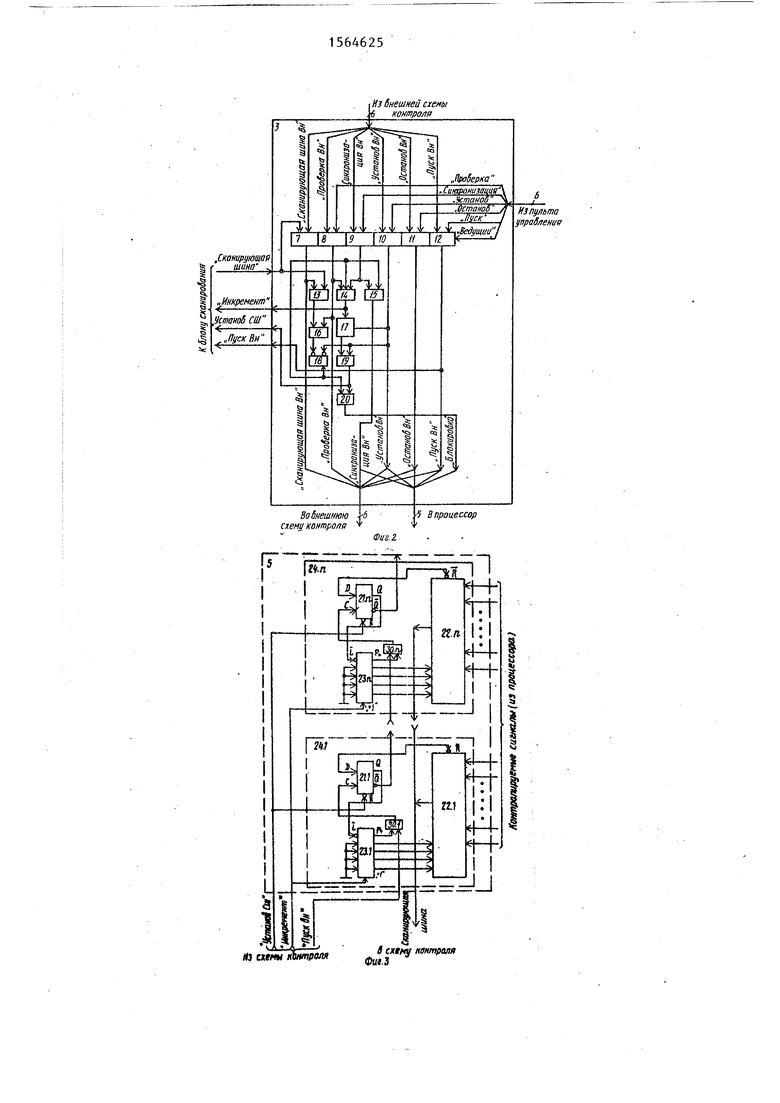

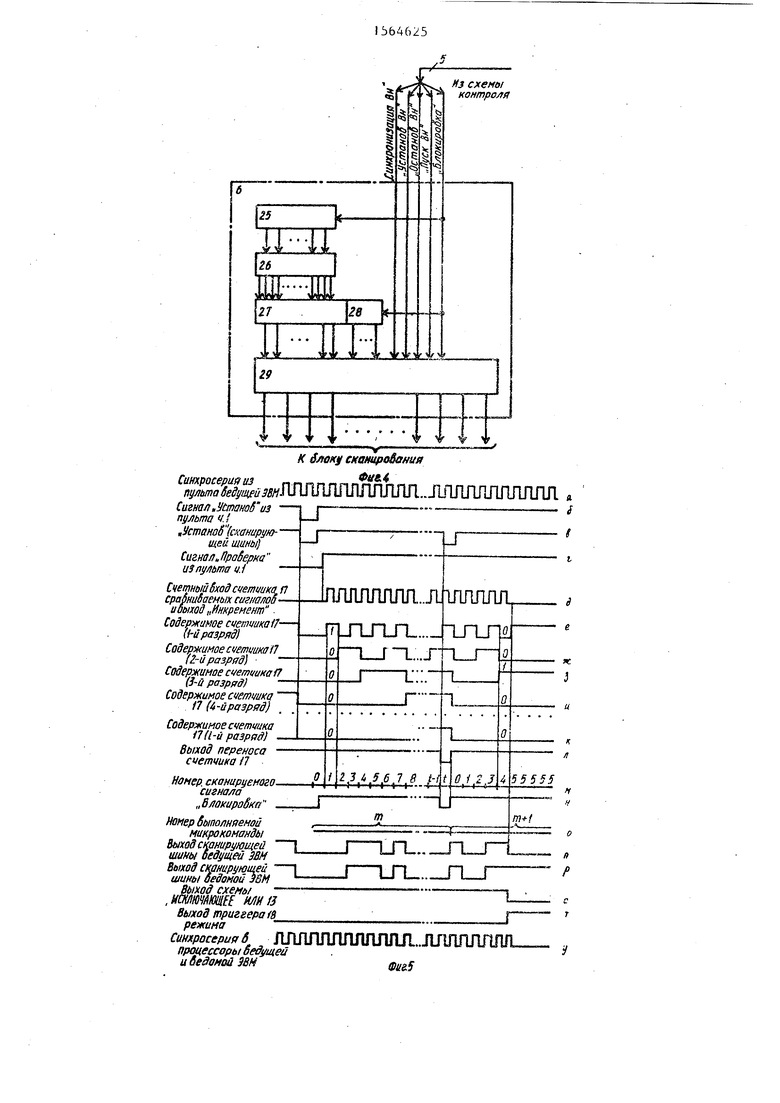

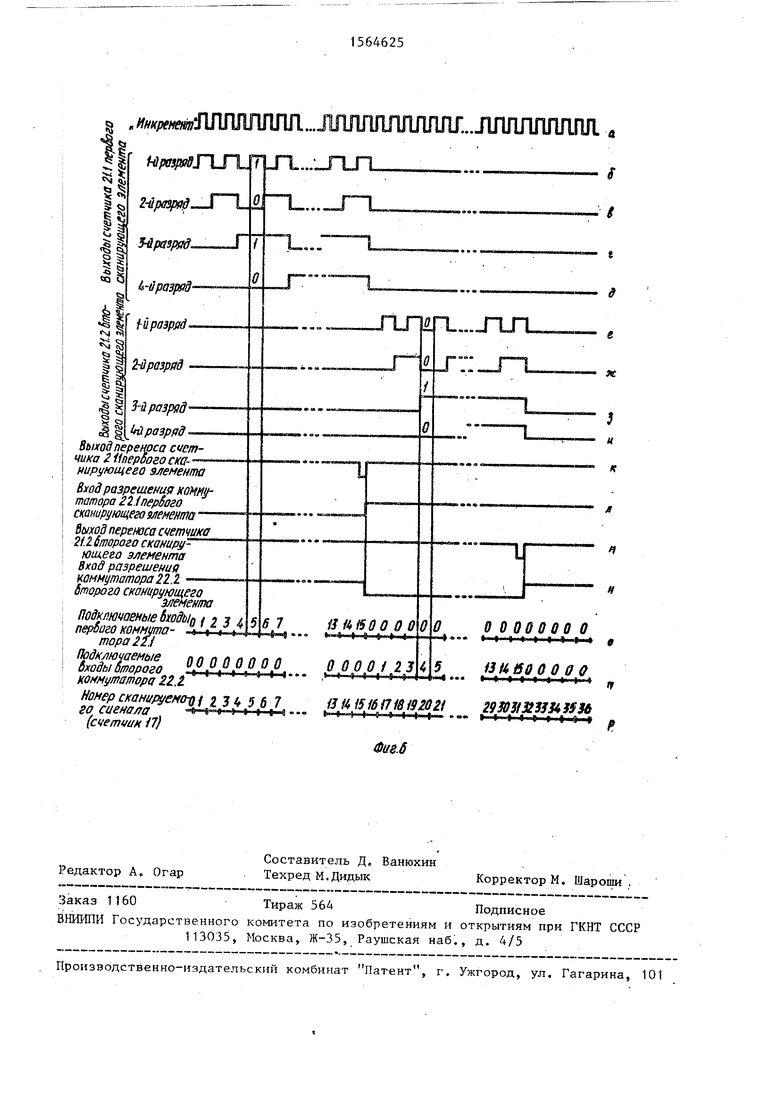

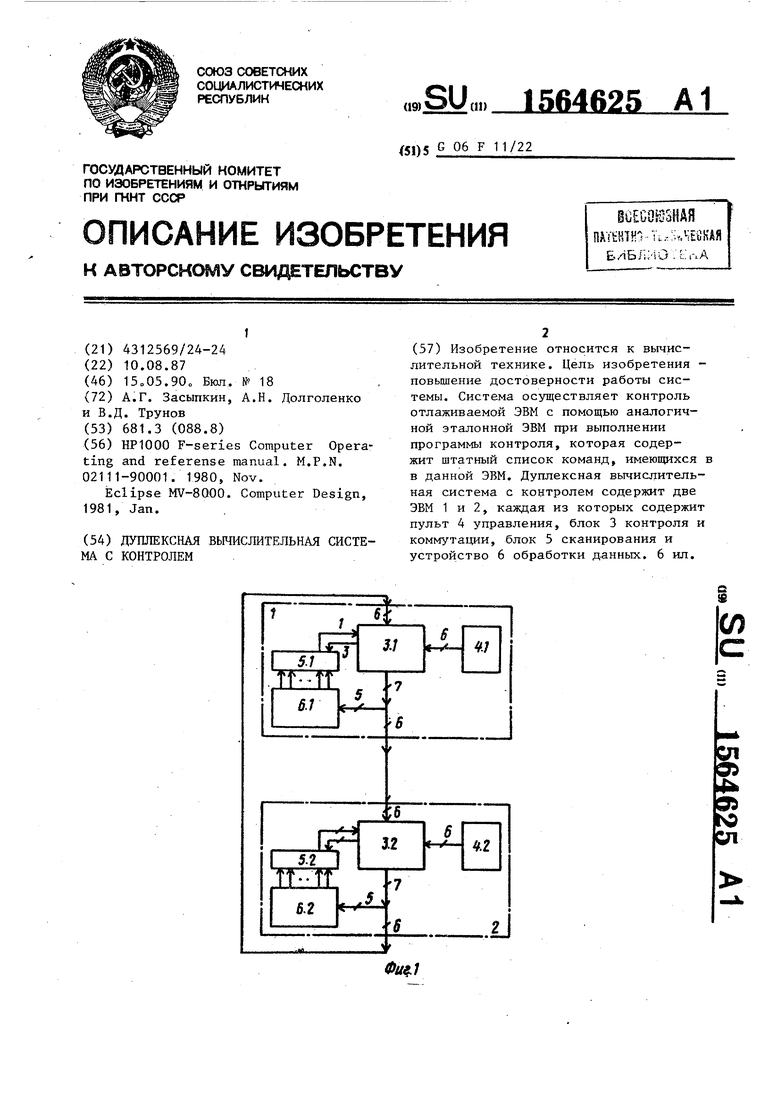

На фиг 1 представлена структурная схема дуплексной вычислительной системы с контролем; на фиг. 2 - схема блока контроля и коммутации; на гоиг. 3 - схема блока сканирования, |на фиг„ 4 - структурная схема устройства обработки данных, пример испол- нения; на фиг„ Ь и 6 - временные диаграммы работы устройства.

Дуплексная вычислительная система (фиг. 1) содержит две вычислительные Машины (ЭВМ) I н 2, каждая из которых Имеет блок 3 контроля и коммутации, гульт 4 управления, блок 3 сканирова- шя и устройство 6 обработки данных, 1 Блок контроля и коммутации (фиг.2) включает с первого по шестой комму- (гаторы 7-12, элементы ИСКЛЮЧАЮЩЕЕ И ПИ 13, И 14-16, счетчик 17, триггер 18

тате этого ЭВМ I и 2 имеют общую синхронизацию и полностью управляются сигналами Пуск и Останов с пульта управления ЭВМ 2.

При подаче с пульта управления ЭВМ 1 сигнала Установ низким логическим уровнем с выхода четвертого коммутатора 10 -этот сигнал поступает на R-вход счетчика 17, обнуляя его, На S-вход триггера 18, устанавливая его в 1, и на первый вход, элемент;- И 19, вызывая появление на его выходе сигнала низкого логического уровня Установ сканирующей шины (Установ СШ). Сигнал Установ СШ поступает ча установочные входы всех п узлов 24. 1-24.п сканирования, обнуляет в -- них все счетчики 23, устанавливает все поямые выходы триггеров 21 л О, Выход триггера 21 первого сканирующего узла устанавливается в 1 по сигналу Пуск внешний. Сигнал Установ внешний, поступающий с выхода коммутатора 10, также проходит в процессор ЭВМ 1 и устанавливает его логику

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

Изобретение относится к вычислительной технике. Цель изобретения - повышение достоверности работы системы. Система осуществляет контроль отлаживаемой ЭВМ с помощью аналогичной эталонной ЭВМ при выполнении програмы контроля, которая содержит штатный список команд, имеющихся в данной ЭВМ. Дуплекская вычислительная система с контролем содержит две ЭВМ 1 и 2, каждая из которых содержит пульт управления 4, блок контроля и коммутации 3, блок сканирования 5 и устройство обработки данных 6. 6 ил.

k элементы И 19 и 20.

Блок сканирования (фиг. 3) соето- Ит из п сканирующих узлов, каждый узел содержи триггер 21 режима, коммутатор 22 и счетчик 23 На схеме на Фиг. 3 обозначены сканирующие уэ- пы 24.1-24.п.

Устройство обработки данных (фиг,4 Представляет собой микропрограммный процессор и содержит регистр 25 адреса микрокоманд, микропрограммное ПЗУ 26, регистры 27 микропрограммных управляющих полей, в том числе и поля, управляющего записью во все регистры процессора 28, и арифметическую и управляющую логику 29.

Каждый узел сканирования (фиг. 3) включает элемент И 30.

Система работает следующим образом.

При поступлении сигнала Ведущий 1 низким уровнем с пульта управления ЭВМ в коммутаторы 7-12 коммутируются сигналы Проверка, Синхронизация, Установ, Останов, Пуск с входов на выходы этих KOMMytaTopos. Далее эти сигналы поступают на вход устрой ства 6 ЭВМ 1, а также через коммутаторы 7-12 блока 3 поступают в процессор ЭВМ 2, так как сигнал Ведущий пульта управления ЭВМ 2 находится в единичное состоянии. В резулъ

S

указанный сигнал поступает через блок 3 контроля в ЭВМ 2, устанавливая в ней логику в исходное состояние. При поступлении положительного сигнала Проверка с пульта 4 управления ЭВМ 1 на второй вхо первой группы входов блока 3 обе ЭВМ переходят в режим проверки При -этом высокий логический уровень с выхода второго коммутатора 8 блока 3 контроля ЭВМ 1 приходит на второй вход элемента И 16, снимая запрещение прохождения сигнала ошибя ки через этот элемент, на первый вход элемента И 14, разрешая прохождение сигнала синхронизации на счетный вход счетчика 17 сравниваемых сигналов (фиг. 5д),НсЗ второй вход третьего 5 элемента И 20, формируя на его выходе сигнал Блокировка (фиг. 5н) высоким логическим уровнем (так как сигнал Установ уже идет высоким логическим уровнем, а переполнения счетчика 17 еще нет и выход переноса этого счетчика находится в состоянии 1), который поступает по одноименному выходу на управляющие входы регистра 25 адреса микрокоманд и регистра микрокомандного поля, управляющего записью в регистры 28 устройства 6 ЭНМ 1, блокируя изменение номера выполняемой микрокоманды и изменение информации во всех регистрах устройства 6. Кро0

5

ме того, сигнал Проверка внешняя блока 3 ЭВМ 1 поступает по внешнему кабелю на вход второй группы входов Проверка внешняя блока 3 ЭВМ 2, действуя аналогично описанному, и в ЭВМ 2.

I

При поступлении на счетные входы счетчиков 17 машин 1 и 2 сравниваемых импульсов синхронизации (фиг.5д) эти счетчики начинают синхронно увеличивать свое состояние (фиг.5е-к). Одновременно эти же импульсы синхронизации поступают через выход Инкре мент на счетные входы счетчикоэ 23 каждого из сканирующих узлов (фиг.ба блоков 5 сканирования обеих ЭВМ. При этом, так как на входы загрузки счетчиков 23 всех сканирующих узлов, кроме первого, подан логический нуль (в связи с тем, что триггеры 21 были установлены сигналом Установ сканирующей шины низким логическим уровнем), то, несмотря на присутствие на их входах сигналов синхронизации, они не увеличивают своего состояния. Свое состояние увеличивает только счетчик 23 первого сканирующего узла (фиг. бб-д), так как выход его триггера 21 установился в 1 по сигналу Пуск внешний. При этом на выход первого коммутатора начинают последовательно подключаться выходы проверяемых узлов процессора (фиг. 6п). После прохождения первых шестнадцати импульсов на выходе переполнения счетчика первого сканирующего узла 23 возникает сигнал переноса низким логическим уровнем, (фиг.бк), который через элемент И 30 поступает на С-вход триггера 21 режима и устанавливает его инверсный выход высоким логическим уровнем, который поступает на вход разрешения коммутатора 22 и отключает его от шины. Кроме того, переход из О в 1 поступает через элемент И 30 на синхро- вход триггера 21 режима второго сканирующего узла 24.2 и устанавливает его выход низким логическим уровнем,. который, приходя на управляющий вход коммутатора 22 второго сканирующего ; узла, подключает его к сканирующей шине (фиг. 6о), одновременно с выхода этого триггера 21 высокий логический уровень приходит на вход загрузки счетчика 23, устанавливая его в исходное состояние.

1564625

0

0

5

5

По приходу следующих шестнадцати синхроимпульсов по входу Инкремент следующие шестнадцать контролируемых сигналов выдаются на сканирующую шину (фиг. бе-и, р). По приходу 32-го синхроимпульса с выхода счетчика 23 второго сканирующего узла поступает сигнал переноса низким логическим, который отключает этот узел от сканирующей шины (фиг. 6н, о) и подключает третий сканирующий узел и т.д. до тех пор, пока не возникнет несравнение (ошибка в работе контролируемой ЭВМ) или не будут сравнены все контролируемые сигналы. В этом случае на выходе переполнения счетчика 17 контролируемых сигналов возникает сигнал переноса низкого уровня (фиг. 5л), который, проходя через элемент И 19 на выход Установ сканирующей шины блока 3 контроля (фиг. 5в), устанавливает все сканирующие узлы в исходное состояние аналогично описанному, кроме того, этот сигнал, проходя через элемент И 20 на выход Блокировка блока 3 контроля, поступает далее в устройство 6 на управляющие входы регистра 25 адреса микрокоманд и регистра микрокомандного поля, управляющего записью в регистры 28, разрешая изменение адреса микрокоманды и запись в регистры процессора (фиг. 5н). Таким образом, при выпол-, нении m-й микрокоманды проходит синхросигналов, при каждом из которых происходит выдача на сканирующую шину состояния выхода одного из контролируемых узлов. При этом информация в регистры процессора не заносится, , т.е. происходит обработка одной к той же информации, и только при приходе последнего синхроимпульса m-й микрокоманды происходит запись в регист- 5 ры (фиго 5о). Информация о состоянии контролируемых узлов и схем процессоров ЭВМ 1 и 2 поступает по сканирующей шине на первый вход первых коммутаторов 7 блоков контроля ведущей и ве- 0 домой ЭВМ. При этом информация сканирующей шины ведомой ЭВМ, проходя через первый коммутатор 7 блока контроля ведомой ЭВМ (так как для этого блока сигнал Ведущий высокий), пос- с тупает на выход Сканирующая шина Вн и через внешний кабель проходит на второй вход первого коммутатора 7 блока контроля ведущей ЭВМ. С выхо-. да этого коммутатора (так как для

0

5

0

этой схемы контроля сигнал Ведущий низкий) информация сканирующей шины ведомой ЭВМ поступает на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 бпо ка контроля ведущей ЭВМ, на первый вход которой по входу Сканирующая шина, приходит информация сканирующей шины ведущей ЭВМ. Если при выполнении программы проверки состояние выхода какого-либо контролируемого узла ведомой (контролируемой) ЭВМ не совпадает с состоянием этого же узла ведущей (эталонной) ЭВМ (что свидетельствует о возникновении ошиб- ки функционирования), то на выходе Элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 ночника- IЈT высокий логический уровень, кото- , поступая на первый вход элемента И 16, вызывает появление на его йыходе (так как сигнал Проверка высокий) низкого логического уровня (фиг. 5п-с), который устанавливает ыход триггера 18 ошибки в низкий .логический уровень (фиг. 5т) „ Этот Низкий логический уровень, приходя i-ta второй вход элемента И 14 блока онтроля ведущей ЭВМ, запрещает уве- фшение содержимого счетчика контро - фФуемых сигналов и сигнал Инкре- Нент (фиг. 5д-и), а поступая на Первый вход элемента 15 блока контроля ведущей ЭВМ, блокирует поступление синхронизации на выход Синхронизация внешняя этого блока 3 конт- роля и далее в блок 3 контроля ведущей ЭВМ. Тзким образом выполнение Программы прекращается и содержимое счетчика 17 контролируемых сигналов указывает номер узла, в котором про- изошла ошибка, состояние сканирующих шин определяет правильный и ошибочны уровень сигнала, а содержимое регистра 25 микрокоманд содержат адрес микрокоманды, в которой произошла ошиРк Все это полностью локализует неисправный узел в процессоре микропрограммкой ЭВМ. Сигналами Пуск и Останов с пульта управления ведущей ЭВМ запускается и останавливается рабочая программа, которую выполняют обе ЭВМ.

Так как сканирующие узлы 24.1- 24.п располагаются непосредственно на платах процессора, а на выходные разъемы этих плат выходит только три сигнала: Установ сканирующей шины1 , Инкремент, Сканирующая шина, то имеется возможность подключать к

входам этих элементов большое число контролируемых узлов, что обеспечивает высокую степень локализации ошибок Затраты на разработку математического обеспечения функционального контроля минимальны, так как программа представляет собой набор команд для данной микропрограммной ЭВМ.

Формула изобретения

Дуплексная вычислительная система с контролем, содержащая две вычислительные машины5 причем каждая из вычислительных машин содержит пульт управления и устройство обработки данных, отличающаяся тем, что, с цепью повышения достоверности работы системы, каедая вычислительная машина содержит блок сканиро- вания и блок контроля и коммутации, причем в каждой вычислительной машине выходы Проверка, Синхронизация, Установ, Останов. Пуск, Ведущий пульта управления соединены с одноименными входами первой группы входов блока контроля и коммутации, выходы Сканирующая шина внешняя, Проверка внешняя, Синхронизация внешняя, Установ внешний,, Останов внешний, Пуск внешний каждой вычислительной машины являются одноименными выходами блока контроля и коммутации и соединены с одноименными входами другой вычислительной машины, которые являются одноименными входами второй группы входов блока контроля и коммутации, выходы Синхронизация внешняя, Установ внешний, Останов внешний, , Пуск внешний и Блокировка блока контроля и коммутации соединены с. одт поименными входами устройцтва обработки данных в каждой машине, выходы которого соединены с информационными входами блока сканирования9 выходы Инкремент, Пуск внешний и Установ сканирующей шины блока контроля и коммутации соединены с одноименными входами блока сканирования, выход Сканирующая шина которого соединен с одноименным входном блока контроля и коммутации, причем блок контроля и коммутации в каждой вычислительной машине содержит шесть коммутаторов, пять элементов И, счетчик элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и триггер,

выход которого соединен с первыми входами первого и второго элементов И, выход первого элемента И соединен со счетным входом счетчика и является выходом Инкремент блока контроля и коммутации, первые информационные входы с первого по шестой коммутаторов соединены соответственно с входами Сканирующая шина внешняя Проверка внешняя, Синхронизация внешняя, Установ внешний, Останов внешний, Пуск внешний второй группы входов блока контроля и коммутации, второй информационный вход первого коммутатора и первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с входом Сканирующая шина блока контроля и коммутации, вторые информационные входы с второго по шестой коммутаторов соединены соответственно с входами Проверка, Синхронизация, Установ, Останов и Пуск первой группы входов, блока конт- роля и коммутации, вход Ведущий первой группы входов которого соединен с управляющим входами с первого по шестой коммутаторов выход первого коммутатора соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛ и является выходом Сканирующая шина внешняя блока контроля и коммутации, выход второго коммутатора соединен с вторым входом первого элемента И, первыми входами третьего и четвертого элементов И -и является выходом Про--, верка внешняя блока контроля и коммутации выход третьего коммутатора соединен с третьим входом первого и вторым входом второго элементов И, выход четвертого коммутатора соединен с входом сброса счетчика, первым установочным входом триггера, первым входом пятого элемента И и является выходом Установ внешний блока контроля и коммутации, выходы пятого и шестого коммутаторов являются соответственно выходами Останов внешний и Пуск внешний блока контроля и коммутации, выход Синхронизация внешняя которого соединен с выходом второго элемента И, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом третьего элемента И, выход которо

го соединен с вторым установочным вхо10

15

20

25

0

5

0

5

0

5

дом триггера, выход Переполнение счетчика соединен с вторым входом пятого элемента И, выход которого соединен с вторым входом четвертого элемента И и является выходом Установ сканирующей шины блока контроля и коммутации, выход Блокировка которого соединен с выходом четвертого элемента И, причем в каждой вычислительной машине блок сканирования содержит п сканирующих узлов, группы информационных входов которых образуют информационные входы блока сканирования, входы Установ сканирующей шины и ь пкремеит которого подключены соответственно к входам установки и счета с первого по п-и сканирующих узлов, вход Пуск внешний блока сканирования соецине.4 с входом разрешения первого сканирующего узла, выход разрешения 1-го сканирующего узла соединен с одноименным входом (1-И)го сканирующего узла (i , п-1), информационный выход (i+1)-ro сканирующего узла соединен с информационным входом 1-го сканирующего узла, информационный выход первого сканирующего узла является чыходим сканирующей шины блока , сканирования, причем каэдый сканирзто- гаий узел содержит счетчик, элемент И, триггер режима, коммутатор, пер- вый3 второй, третий и четвертый информационные входы счетчика соединены с первым, вторым,третьим и четвертым управляющими входами коммутатора соответственно, инверсный выход триггера режима соединен с информационным входом триггера режима, с входом разрешения коммутатора и является выходом разрешения сканирующего узла, первый вход элемента И соединен с входом рд-зрешения сканирующего узла, выход переноса счетчика соединен с вторым входом элемента И, выход которого соединен с входом синхронизации триггера режима, прямой выход которого соединен с входом записи счетчика, сметный вход которого соединен с входом счета сканирующего узла, выход коммутатора является информационным выходом сканирующего узла,информационные входы коммутатора являются информационными входами сканирующего элемента.

Кювпропирдемм сигналы (из процессора)

U1

СТ Ј

о

IS5 Ul

.ллшишплшш.

i

К блоки сканирования

п п п л n n rmti п п ЛЛШ11 ШЛЛЛЛЛ.

|

JшллJ лJШJUlя..шlrlГlлллл. ,

У

f

i

е ж

i

к II

...

Фиг.5

.ллшишплшш.

i

f

i

е ж

i

к II

...

Фиг.5

,towM™mmm...jimmmim...jmmmji

Номер сканируемо 234567 so сигнала «-«-ч- - - - -

(счетчан Л)

1314 15161718192021 29ЯМЗгЯ& $36

t С I -i 4--t- ... « ... .

| УСТРОЙСТВО ДЛЯ ИЗБИРАТЕЛЬНОГО ВЫЗОВА ТЕЛЕФОННЫХ АППАРАТОВ | 1922 |

|

SU1000A1 |

| M.P.N | |||

| Устройство для введения порошкообразных примесей в металл во время его отливки | 1925 |

|

SU2111A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Центрифуга непрерывного действия для разделения жидкостных смесей | 1926 |

|

SU8000A1 |

| Computer Design, 1981, Jan. | |||

Авторы

Даты

1990-05-15—Публикация

1987-08-10—Подача