Фиг.1

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в синтезаторах частот.

Цель изобретения - повышение симметрии выходнбго сигнала в широком частотном диапазоне.

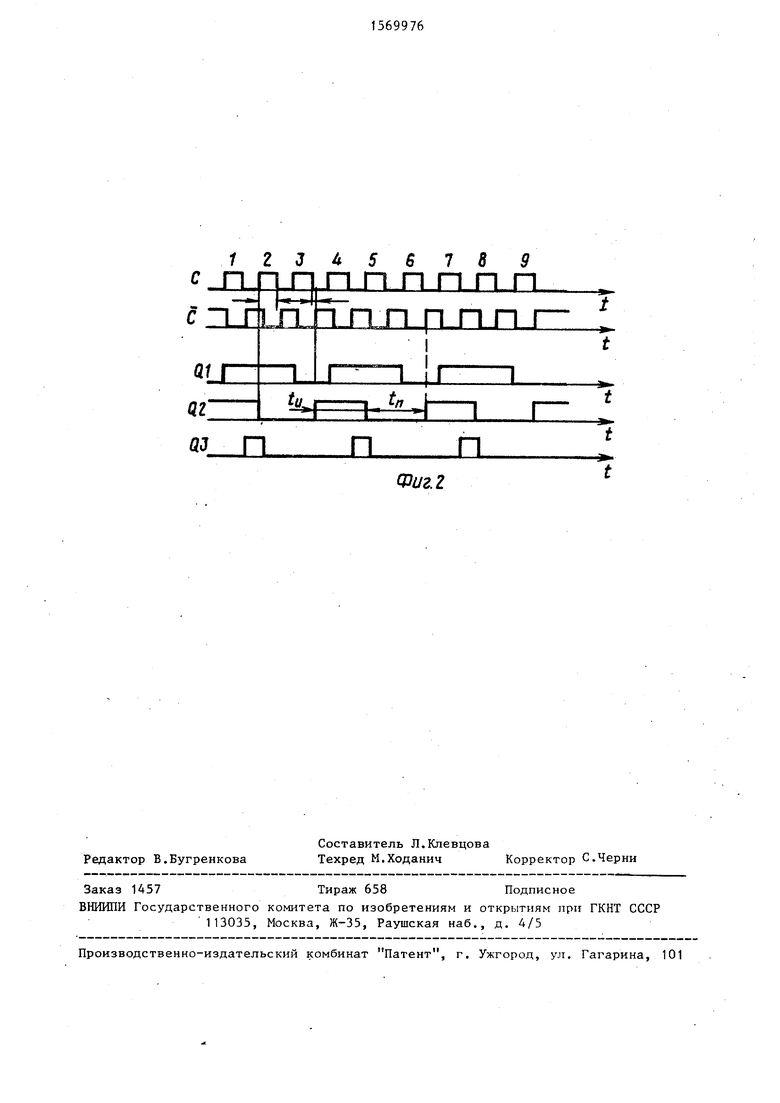

На фиг.1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы его ра- (боты.

Делитель частоты на три содержит D-триггер 1, первый и второй RS-триг- геры 2.и 39 первый и второй элементы И-НЕ 4 и Ь, входную шину 6, подключенную к С-входу D-триггера 1, прямой выход первого RS-триггера 2 подключен к третьему входу второго элемента И-НЕ 5, выход которого подключен к S-входу второго RS-триггера З, R-вход которого подключен к прямому выходу первого RS-триггера 1, содержит также элемент НЕ 7, третий элемент И-НЕ 8, выход которого соединен с S -входом первого RS-триггера 1, первый вход - с инверсным выходом D-триггера 1 и D-входом D-триггера 1, второй вход - с выходом элемента НЕ 7, вход которого подключен к входной шине 6, прямой выход D-триггера 1 подключен к первому входу второго элемента И-НЕ 5, второй вход которого подключен к выходу элемента НЕ 7, причем прямой выход второго RS-триггера З подключен к второ.му входу первого элемента И-НЕ 4, первый вход которого подключен к входной шине 6, а выход подключен к R-входу первого RS-триггера 2, выход которого подключен к выходной шине 9, инверсный выход второго RS-триггера З подключен к S-входу D-триггера 1.

Делитель частоты работает следующим образом.

Пусть триггеры 1 и 3 находятся в нулевом состоянии (0 0 и Q j 3 на фиг. 2). Тогда, при отсутствии счетных импульсов на входной шине 6 (С 0) на выходе инвертора 7 устанавливается единица, которая совместно с единицей, поступающей с инверсного выхода триггера i на дру гой вход элемента И-НЕ 8У приведет к срабатыванию последнего и появлению на его выходе нуля, под воздействием которого триггер 2 установится в состояние 1, которая поступает на выход 9 устройства.

5

0

5

0

5

0

5

0

5

При поступлении в устройство импульсов С, имеющие скважность, равную 2, по положительному фронту первого импульса триггер 1 переключится в состояние 1, при котором на его инверсном выходе устанавливается нулевой потенциал, блокирующий прохождение через первый элемент И-НЕ 8 первого инверсного импульса С на триггер 2. Второй элемент И-НЕ 5 по этому импульсу С срабатывает, так как на его оба разрешающих входа поступают единицы с прямых выходов триггеров 1 и 2, и на его выходе появится О, который триггер 3 установит в состояние 1 по входу S. При этом на его прямом выходе появится единичный потенциал, разрешающий работу третьего элемента И-НЕ 4, а на инверсном выходе - нулевой потенциал, удерживающий триггер 1 по его S-входу в единичном состоянии, при котором продолжается блокирование элемента И-НЕ 8 нулем.с инверсного выхода триггера 1. Поэтому второй импульс С не воздействует на состояние триггера 1, но через элемент И-НЕ 4 сбросит триггер 2, на прямом выходе которого установится О, под воздействием которого установится в О также триггер 3, который заблокирует элемент И-НЕ/4, но снимет нулевой потенциал с S-входа триггера 1, который останется в единичном состоянии, так как срабатывает по фронту счетных импульсов, и сможет вернуться в нулевое состояние только по фронту следующего импульса С.

При поступлении третьего импульса С триггер 1 переключается в О, блокируется элемент И-НЕ 5, но снимается блокировка с элемента И-НЕ 8. Поэтому с приходом третьего инверсного импульса С с выхода инвертора 7 от- ткроется только элемент И-НЕ 8 и переключится в 1 только триггер 2, который будет находиться в единичном состоянии, пока не поступит четвертый импульс С, переключающий аналогично первому импульсу триггер 1 в единичное состояние, разрешающее i сброс второго триггера 2 в О по пятому импульсу С, действующему аналогично второму импульсу С.

Следовательно (фиг. 2), переключения триггера 1 происходят по первому, третьему и четвертому импульсам

-, Тге„ этим тригг , - г.

следования делится на три, но скважность его выходного сигнала не равна двум. Переключения триггера 2 происходят по второму и пятому импульсам С и третьему инверсному импульсу С, т.е. вторым триггером 2 частота следования импульсов С также делится на три, но скважность q его выходного сигнала равна 2.

Для надежной работы устройства при воздействии второго импульса необходимо соблюдение следующего условия:

Ч

ч +

ч +

V

где t - время переключения триггера 1; t - время переключения тригге-

ра 2; t - время переключения триггера 3; t, - время срабатывания третьего

элемента И-НЕ 4.

При соблюдении указанного условия обеспечивается надежная работа триггера 1 и всего делителя частоты на три, что легко выполняется при использовании в качестве триггера 1 уки версального В(Т)-триггера.

Полная симметрия выходного сигнала получается для рассматриваемого и известного устройств при выполнении равенства длительностей импульса t

и паузы tn величине 3tc, при скважности счетных импульсов qc 2, т.е.

п

3tc,

где tc - длительность счетных (входных) импульсов.

Нарушение этой симметрии зависит от величин задержек логических элементов и схемотехники обоих устройств .

Более точный временной анализ устройства по изобретению показывает, что время задержки tL появления единичного уровня на выходе Oj, RS-триг- гера 2 и устройства (Q 1) относительно отрицательного фронта счетных импульсов С определяется суммарным временем срабатывания элементов 7 и 8 и элемента И-НЕ в триггере 2, т.е. имеем }

976

6

а время задержки t ° установления нулевого уровня на этом же выходе (Q2 0) относительно положительного фронта счетных импульсов С определяется суммарным временем срабатывания элемента 4 и двух элементов И-НЕ в триггере 2

в и2-t

- t

2-7

15

Тогда реальная длительность tM выходного импульса будет

tM - 3tc- (t j- tj). (1,1)

а

Из-за технологического разброса Jtcp времен tcp срабатывания логических элементов - -0

t }

at

t 0 и имеем

ср

Э

Так как уменьшение tH приводит к увеличению tn, и наоборот, то отклонение от симметрии выходного сигнала можно оценить величиной

t,I - 2- at

(1.2)

а

относительное рии величиной

отклонение от симметл I tM - tn| 2 Л tcp

- -зГс 3tc

35

т ч.

/at.

(1.3)

так как

qutc

тг

iC, где qc - скважность счетных импульсов, fc - их частота и Тс - период следования.

Временной анализ известного устройства показывает, что для него время задержки t . определяется суммарным временем 2tcp задержки распространения сигнала от входа С до прямого выхода D(T) триггера 1.двумя элемента0

5

ми И-НЕ . о

2t

ср

а время задержки

и определяетсясуммарным временем

распространениясигнала С 0 через

элемент ИЛИ 3 ивход R до выхода триггера 1 и равно

I 3t P

С учетом технологического разброса Atce времен t

-f

ср

(4tcp,i

сср)

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь временных параметров импульсных последовательностей | 1980 |

|

SU900445A1 |

| Преобразователь код-временной интервал | 1985 |

|

SU1298921A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119176A1 |

| Устройство для выделения одиночного импульса | 1984 |

|

SU1256167A1 |

| Селектор верхних и нижних частот | 1990 |

|

SU1732432A1 |

| Ждущий мультивибратор | 1982 |

|

SU1109893A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1990 |

|

SU1723658A2 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Устройство для измерения отношения частот двух сигналов | 1986 |

|

SU1383217A2 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - повышение симметрии выходного сигнала в широком частотном диапазоне. Цель изобретения достигается путем введения элемента НЕ 7, элемента И-НЕ 8 со связями. Устройство также содержит D-триггер 1, RS-триггеры 2, 3, элементы И-НЕ 4, 5, входную 6 и выходную 9 шины. 1 ил.

t;+1. +1

1-1

в известном устройстве реальная длительность выходного импульса будет

tj - 3tc-|(t1 - tj ) + tftp - 3tc + (tcp + dtef),(2.1)

отклонение от симметрии выходного сигнала

|tH - tH | 2 (tcp + -at); (2.2)

а относительное отклонение от симметрии

я 3 q (tfcP + At

(2.3)

Сопоставляя оба устройства по свойствам, можно заключить на основании полученных выражений (1.1-1.3) и (2.1-2.3) следующее:

а)в предлагаемом устройстве при отсутствии технологического разброса временных параметров (dtCp- 0 при точной технологии) возможна полная симметрия входного сигнала, а также

jнаблюдается более слабая зависимость от частоты входных (счетных) импульсов, определяемая величиной 4tcp fc;

б)в известном устройстве существует ассиметрия выходного сигнала из-за наличия постоянной разницы меж ду длительностями импульса и паузы

в две элементарные задержки и поэто- му симметрия этого сигнала невозможна даже при точной технологии, причем нарушение симметрии будет прояв- ляться с ростом частоты входного сигнала намного сильнее, чем у предлагаемого устройства, так как

(tcp + atc, ) -fe Att fc.

-cp

-cp

tp

Таким образом, положительный эффект от использования предлагаемого технологического решения по сравнению с известным устройством заключа- 45

0

5

0

5

о

,.

0

5

ется в достижении более высокой симметричности выходного сигнала и ее сохранении в более широком (в несколько раз, определяемом отношением

t cp + и ..

-) диапазоне рабочих часAtcf

тот. Кроме того, предлагаемое устройство более технологично, так как использует однотипные элементы И-НЕ.

Формула изобретения

Делитель частоты на три, содержащий D-триггер, первый и второй RS- триггеры, первый и второй элементы И-НЕ, входную шину, подключенную к С-входу D-триггера и первому входу первого элемента И-НЕ, прямой выход D-триггера подключен к первому входу второго элемента И-НЕ, отличающийся тем, что, с целью повышения симметрии выходного сигнала в широком частотном диапгзоне, в него введен элемент НЕ, третий элемент И-НЕ, выход которого соединен с S- входом первого RS-триггера, первый вход - с инверсным выходом гера и D-входом D-триггера, второй вход - с выходом элемента НЕ, вход которого подключен к входной шине, а выход - к второму входу второго элемента И-НЕ, третий вход которого подключен к прямому выходу первого RS-триггера, а выход к -входу второго RS-триггера, прямой выход которого подключен к второму входу первого элемента И-НЕ, а инверсный выход - к S-входу D-триггера, при этом прямой выход первого RS-триггера подключен к R-входу второго RS-триггера и выходной шине устройства, а выход первого элемента И-НЕ подключен к li-входу первого RS-триггера.

QJП

П.

Фиг. Z

| Делитель частоты на три | 1979 |

|

SU784004A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты на три | 1986 |

|

SU1354414A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-20—Подача