ел ел

вание группы кодов номеров каналов из блока 13 памяти через регистр 19 на входы демультиплексора 21, преобразующего информацию в унитарные ко- , ды. Эти коды единичными значениями инвертируют состояния входных Т-триг- геров блока 22 каналов формирования кодов, которые с наступлением следующего такта сообщают свои значения выходным D-триггерам блока 22 и соответственно выходам устройства. Блок 13, делитель 12 частоты и коммутатор 15 обеспечивают отсчет интервалов At в f тактах, что повышает информативность и приводит к снижению объема памяти блока 11, 1 ил0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1345322A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1406736A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1439744A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1499438A2 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1429116A1 |

| Устройство для программируемой задержки информации | 1986 |

|

SU1381468A1 |

| Устройство сбора дефектоскопической информации | 1985 |

|

SU1298719A1 |

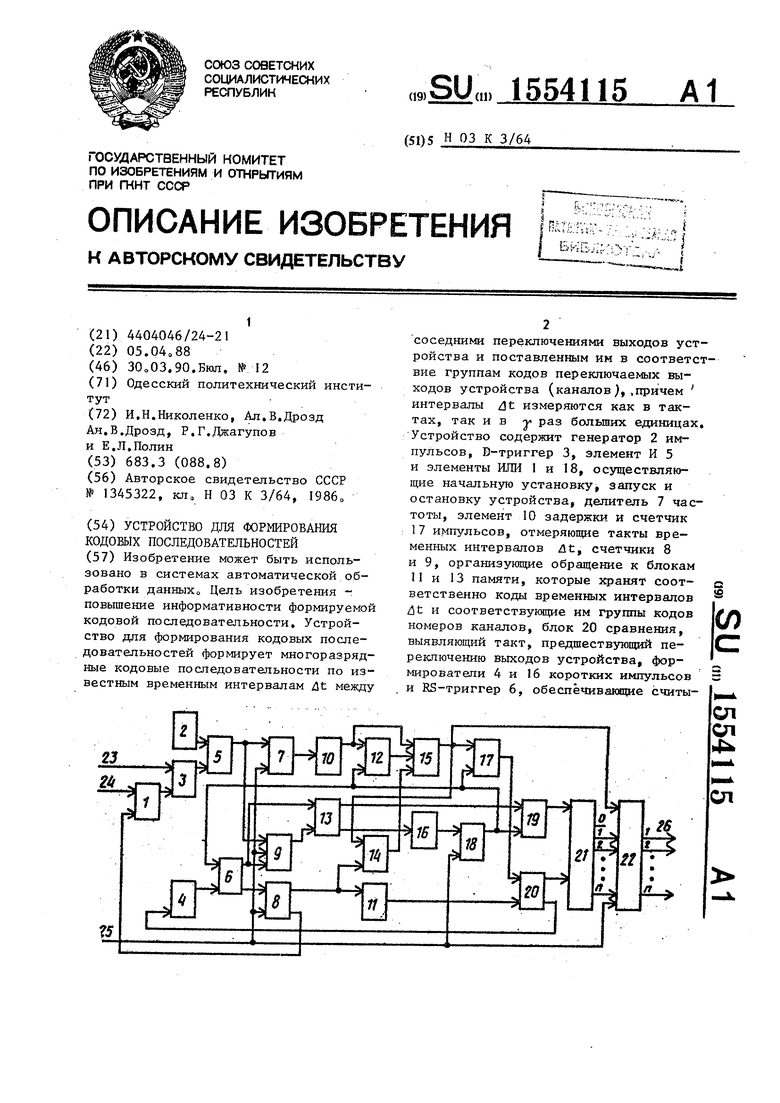

Изобретение может быть использовано в системах автоматической обработки данных. Целью является повышение информативности формируемой кодовой последовательности. Устройство для формирования кодовых последовательностей формирует многоразрядные кодовые последовательности по известным временным интервалам ΔТ между соседними переключениями выходов устройства и поставленным им в соответствие группам кодов переключаемых выходов устройства (каналов), причем интервалы ΔТ измеряются как в тактах, так и в γ раз больших единицах. Устройство содержит генератор импульсов 2, D-триггер 3, элемент И 5 и элементы ИЛИ 1 и 18, осуществляющие начальную установку, запуск и остановку устройства, делитель частоты 7, элемент задержки 10 и счетчик импульсов 17, отмеряющие такты временных интервалов ΔТ, счетчики 8 и 9, организующие обращение к блокам памяти 11 и 13, которые хранят соответственно коды временных интервалов ΔТ и соответствующие им группы кодов номеров каналов, блок сравнения 20, выявляющий такт, предшествующий переключению выходов устройства, формирователи коротких импульсов 4 и 16 и триггер 6, обеспечивающие считывание группы кодов номеров каналов из блока памяти 13 через регистр 19 на входы демультиплексора 21, преобразующего информацию в унитарные коды. Эти коды единичными значениями инвертируют состояния входных Т-триггеров блока 22 каналов формирования кодов, которые с наступлением следующего такта сообщают свои значения выходным D-триггерам блока 22 и соответственно выходам устройства. Блок 13, делитель частоты 12 и коммутатор 15 обеспечивают отсчет интервалов ΔТ в γ тактах, что повышает информативность и приводит к снижению объема памяти блока 11. 1 ил.

Изобретение относится к импульсной технике и может быть использовано в системах автоматической обработки данных.

На чертеже представлена функциональная схема устройства для формирования кодовой последовательности.

Цель изобретения - повышение ин- формативности формируемой кодовой последовательности за счет ее воспро- изведения в больших пределах.

На чертеже показана схема устрой- ства.

Устройство содержит первый элемент ИЛИ I, генератор 2 импульсов, D-триг- гер 3, первый формирователь 4 коротких импульсов, элемент И 5, RS-триг- гер 6, первый делитель 7 частоты, первый счетчик 8 адреса, второй счетчик 9 адреса, элемент 10 задержки, первый блок 11 памяти, второй делитель 12 частоты, второй блок 13 памяти, третий блок 14 памяти, коммутатор 15, второй формирователь 16 коротких импульсов, счетчик 17 импульсов, второй элемент ИЛИ 18, регистр 19, блок 20 сравнения, демультиплек- сор 21, блок 22 каналов формирования кодов, шину 23 запуска, шину 24 останова, шину 25 начальной установки, выходные шины 26. Первый вход элемента ИЛИ 1 соединен с шиной 24 остано- ва, второй вход - с выходом старшего разряда счетчика 8 адреса, а выход соединен с R-входом D-триггера З, синхровход которого соединен с шиной 23 запуска устройства, а выход - с первым входом элемента И 5, второй вход которого соединен с выходом генератора 2 импульсов, а выход - со счетным входом счетчика 9 адреса и входом делителя 7 частоты, установочный вход которого объединен с установочным входом счетчика 9 адреса, входом сброса счетчика 8 адреса-, входом сброса блока 22 каналов формиро5

0

5

Q . 5 -Q

вания кодов, первым входом элемента ИЛИ 18 и подключен к шине 25 начальной установки. Выход делителя 7 частоты соединен с входом элемента 10 задержки выход которого соединен с первым информационным входом коммутатора 15 и с входом делителя 12 частоты, установочный вход которого соединен с выходом элемента ИЛИ 18, входом сброса регистра 19, установочным входом счетчика 17 импульсов, R-входом RS-триггера 6, а выход соединен с вторым информационным входом коммутатора 15, выход которого соединен со счетным входом счетчика 17 импульсов, с синхровходом блока 22 и с синхровходом блока 14 памяти, выход которого соединен с управляющим входом коммутатора 150 Информационные выходы счетчика 17 импульсов соединены с первыми входами блока 20 сравнения, вторые входы которого соединены с выходами блока 11 памяти, адресные входы которого соединены с адресными входами блока 14 памяти и выходами счетчика 8 адреса, счетный вход которого соединен с инверсным выходом RS-триггера 6, прямой выход которого соединен с входом разрешения счета счетчика 9 адреса и входом выборки 13 памяти, адресные входы которого соединены с выходами счетчика 9 адреса, управляющий выход блока 13 памяти через формирователь 16 соединен с вторым входом элемента ИЛИ 18, а выходы блока 13 памяти - с информационными входами регистра 19, выходы которого соединены с адресными входами демультиплексора 21, выходы которого с первого по п-и соединены с соответствующими информационными входами блока 22, а инверсный вход управления демультиплексора 21 соединен с инверсным выходом блока 20 сравнения, прямой выход которого через формирователь 4 соеди

51

нен с S-входом RS-триггера 6, выходы блока 22 являются выходными шинами 26 устройства о Каждый канал блока 22 каналов формирования кодов содержит в себе последовательно соединенные

Т-триггер и D-триггеро Синхровходы D-триггеров каналов подключены к синхровходу блока каналов, R-входы Т-триггера и D-триггера канала подключены к входу сброса блока каналов счетные входы Т-триггеров каналов являются информационными входами блока каналов, а выходы D-триггеров каналов являются выходами блока ка- налов.

Устройство работает следующим образом.

В блоке 11 памяти хранится последовательность кодов временных интер- валов иt между соседними переключениями выходов устройства,

Если временной интервал At лежит в пределах

)

где -р - увеличенное на единицу максимальное значение, принимаемое счетчиком 17; т 2 (а- разрядность счетчика 17 то временной интервал At представляется как At At т+ At ;

&t j; , а в блоке 11 хранятся величины At1 и Atn,

Если временной интервал /3t Ј(jL О то он представляется через несколько интервалов типа At, имеющих вес у, и интервал Например, при v 16 временной интервал At 300 представляется через интервалы At 15, At 3 я At 12, так как 15x16+3x16+ +12 300. В блоке 11 для этого случая хранятся коды величин At

At 3 и dt 12.

В одноразрядном блоке 14 памяти хранится последовательность бит ин- формации, взаимооднозначно соответствующих кодам временных интервалов блока 11 памяти, причем для каждого кода At и At1 бит принимает соответственно нулевое и единичное значения о Взаимооднозначное соответствие устанавливается за счет объединения адресных входов блоков 1 1 и 14 памяти.

) 10

15541

, .,

20в

25

30

35

40

45

rj

55

156

В блоке 13 памяти хранятся после- довательно группы из i кодов (i 1,п), каждая группа содержит коды номеров каналов блока 22 (или, что то же самое, номеров выходных шин 26), изменяющих свои состояния в момент времени, на который указывает соответствующий временной интервал Jt.

Если временной интервал At разбивается на части, то всем полученным интервалом типа At ставятся в соответствие группы, состоящие из одного нулевого кода, а интервалу At назначается группа кодов, относящаяся ко всему временному интервалу t, В группе коды номеров блока 22 каналов перечисляются в произвольном порядке. Код номера канала содержит дополнительный разряд, принимающий в последнем коде каждой группы единичное значение и нулевое значение в других кодах. Этот признак окончания группы кодов считывается с управляющего выхода блока 13 памяти, Перед пуском устройства сигналом Начальная установка, поступающим на шипу 25, сбрасьшается в ноль счетчик 9 адреса, триггеры блока 22 каналов (выходные шины 26), устанавливаются в единичное значение триггеры делителей 7 и 12 частоты и счетчика 9 адреса, а через элемент ИЛИ 18 сбрасывается в тюль т шоке регистр 19, RS-триггер б и устанавливаются в единичное значение все триггеры счетчика 170

Импульс запуска, поступающий по шипе 23 на сихровход D-триггера З, устанавливает его в единичное состояние (информационный вход D-триггера запитан уровнем лог. 1), разрешая прохождение импульсов с генератора 2 импульсов через элемент И 5 на счетный вход счетчика 9 адреса и через делитель 7 частоты - на вход элемента 10 задержки. С выхода элемента 10 задержанные импульсы СИ,- отмеряющие такты работы устройства, поступают на первый информационный вход коммутатора 15, а через делитель 12 частоты - на второй информационный вход коммутатора 15. Первый импульс с выхода элемента 10 задержки поступает одновременно на оба информационных входа коммутатора 15 (делитель 12 частоты под действием первого импульса переходит в

715

нулевое состояние с выработкой на выходе импульса СИ). При этом коммутатор 15 независимо от значения сигнала на управляющем входе передает импульс на счетный вход счетчика 17, устанавливая все его триггеры в следующее нулевое состояние. .Код с выходов счетчика 17 поступает на первые входы блока 20 сравнения, В это время блок 11 памяти считывает по нулевому адресу, поступающему с выходов счетчика 8 адреса, первый код временного интервала t« По тому же адресу с выхода блока 14 памяти считы вается бит В информации, который поступает на управляющий вход коммутатора 15 и обеспечивает подключение на его выход синхросигнала с выхода элемента 10 задержки при и синх- росигнала с выхода делителя 12 частоты при с При этом на счетный вход счегчика 17 поступают синхросигналы СИ в каждом такте работы устройства, если считан код временного интервала типа ut, и синхросигналы СИ с частотой следования в -у раз меньше, чем СИ, если считан код временного интервала типа дс .

Код с выхода блока 11 памяти посту пает на вторые входы блока 20 сравнения, который уменьшает значение кода на единицу младшего разряда и сравнивает полученный результат с кодом счетчика 170 При совпадении сравниваемых кодов сигнал лог. О1 с инверсного выхода блока 20 сравнения поступает на инверсный вход управления демультиплексора 21, а единичный сигнал с прямого выхода блока 20 срав нения поступает на формирователь 40 . При этом формируется короткий единичный импульс, устанавливающий по S-входу RS-триггер 6 в единичное состояние о Единичный сигнал с прямого выхода RS-триггера б подается на вход выборки блока 13 памяти и вход разрешения счета счетчика 9 адреса, который под действием синхроимпульсов поступающих на его счетный вход, начи нает изменять свой состояние формиру на адресном входе блока 13 памяти последовательность значений адреса. По этим адресам с выхода блока 13 через регистр 19 считываются коды номеров каналов блока 22 на адресный вход демультиплексора 21, обеспечивая последовательное инвертирование состояний соответствующих Т-триггеров бло

0

41

, 25

зд ,

45

158

ка 22 каналов (через информационные входы блока 22 каналов).

Одновременно со считыванием из блока 13 памяти последнего кода номера канала блока 22 с управляющего выхода блока 13 памяти снимается единичный сигнал признака окончания группы. Этот сигнал поступает на вход формирователя 16, с выхода которого короткий импульс поступает через элемент ИЛИ 18 на вход сброса регистра 19, R-вход RS-триггера 6 и на входы установки делителя 12 частоты и счетчика 17. При этом происходит обнуление регистра 19, установка в О RS-триггера 6 и установка триггеров делителя 12 частоты и счетчика 17 в единичное состояние Сигналы с прямого и инверсного выходов RS-триггера 6 соответственно останавливают изменение состояний счетчика 9 адреса и переводят в следующее состояние счетчик 8 адреса При этом из блока 11 памяти считывается следующий код временного интервала dt Этот код сравнивается блоком 20 сравнения с кодами, сменяющимися на выходах счет- ч чика 17 од действием синхроимпульсов СИ или СИ (в зависимости от значения считанного из блока 14 памяти бита информации).

Следующий синхроимпульс СИ, появляющийся на выходе элемента 10 задержки, поступает на синхровход блока 22 каналов, обеспечивая перепись информации с его входных Т-триггеров в выходные D-триггеры, с выходов которых сформированные сигналы поступают на шины 26 устройства.

Если временной интервал дс был разбит на несколько интервалов, то для каждого из полученных интервалов типа 3t из блока 13 памяти будет считана группа кодов, состоящая из одного нулевого кода. Под действием . этого кода, переписанного в регистр 19, демультиплексор 21 изменяет свой нулевой выход, неподключенный к информационным входам блока 22 каналов Таким образом, переключений на шинах 26 устройства в точках разбиения временного интервала Ut на части не происходит.

С каждым синхроимпульсом СИ или СИ, появляющимся на счетном выходе счетчика 7, этот счетчик увеличивает значение кода на его выходе на единицу. При достижении кодом эна9 15

чения, на единицу меньшего величины кода ut (типа л t или и t ), блок 20 сравнения устанавливает этот факт и цикл подготовки и изменения значений сигналов на шинах 26 (с приходом следующего соответствующего синхросигнала повторяется

Завершается работа устройства при установке в единичное значение старшего разряда счетчика 8 адреса. Это значение поступает через элемет ИЛИ 1 на R-вход D-триггера 3, который переходит при этом в нулевое состояние, запрещающее прохождение импульсов генератора 2 через элемент И 5. Завершение работы устройства может быть также достигнуто подачей единичного значения на R-вход D-триггера 3 через шину 24 останова и элемент ИЛИ 1.

Таким образом, данное устройство позволяет отсчитывать временные интервалы 41 не только в тактах работы устройства, но также и в -Y раз больших единицах измерения, что приводит к увеличению информативности формируемой кодовой последовательности, а также обеспечивает снижение требуемого объема памяти блока 11 для хранения кодов интервалов At при больших отрезках времени между смежными переключениями сигналов на выходных шинах устройствао

Формула изобретения

Устройство для формирования кодовых последовательностей, содержащее генератор импульсов, первый и второй элементы ИЛИ, D-триггер, RS-триггер, первый и второй формирователи коротких импульсов, элемент И, первый делитель частоты, первый и второй счетчики адреса, элемент задержки,

первый и второй блоки памяти, счетчик импульсов, регистр лок сравнения, демультиплексор, блок, каналов формирования кодов, пер вый вход первого элемента ИЛИ соединен с шиной останова устройства, второй вход первого элемента ИЛИ - с выходом старшего разряда первого счетчика адреса, а выход соединен с R-входом D-триггера, синхровход которого соединен с шиной запуска устройства, а выход - с первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, а выход - со счет

Q 5 0

5 0

5

Q 5

0 5

1510

ным входом второго счетчика адреса и входом первого делителя частоты, установочный вход которого соединен с установочным входом второго счетчика адреса, входом сброса первого счетчика адреса, входом сброса блока каналов формирования кодов, первым вко.-. дом второго элемента ИЛИ и подключен к шине начальной установки устройства, а выход первого делителя . частоты соединен с входом элемента задержки, информационные выходы счетчика импульсов - с первыми входаг ми блока сравнения, вторые входы которого соединены с выходами первого блока памяти, адресные входы которого соединены с выходами первого счетчика адреса, счетный вход которого соединен с инверсным выходом RS-триг- гера, прямой выход которого соединен с входом разрешения счета второго счетчика адреса, выходы которого соединены с адресными входами второго блока памяти, выходы которого соединены с информационными входами регистра, выходы которого соединены с адресными входами демультиплексора, . выходы которого с первого по n-й соединены с соответствующий информационными входами блока каналов формирования кодов, а инверсный вход управления демультиплексора соединен с инверсным выходом блока сравнения, прямой выход которого через первый формирователь коротких импульсов соединен с S-входом RS-триггера, R-вход которого соединен с входом сброса регистра, установочным входом счетчика импульсов и выходом второго элемента ИЛИ, второй вход которого соединен с выходом второго формирователя коротких импульсов, вход которого соединен с управляющим выходом второго блока памяти, выходы блока каналов являются выходными шинами устройства, отличающееся тем, что, с целью повышения информативности формируемой кодовой последовательности, в него введены второй делитель частоты, третий блок памяти и коммутатор, причем адресные входы третьего блока памяти соединены соответственно с адресными входами первого блока памяти, синхровход третьего блока памяти соединен с синхровходом блока каналов формирования кодов, счетным входом счетчика импульсов и выходом коммутатора, а выход - с уп.11155411512

равняющим входом коммутатора, пер-выходом второго элемента ИЛИ, а вы-.

вый информационный вход которого сое-ход - с вторым информационным входом

динен с выходом элемента задержки икоммутатора, прямой выход RS-триггера

входом второго делителя частоты, ус-соединен с входом выборки второго

тановочный вход которого соединен сблока памяти.

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1345322A1 |

Авторы

Даты

1990-03-30—Публикация

1988-04-05—Подача