СП

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок | 1987 |

|

SU1541677A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок в блоках памяти с последовательным доступом | 1987 |

|

SU1510014A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Устройство для обнаружения ошибок в блоках памяти | 1989 |

|

SU1698907A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

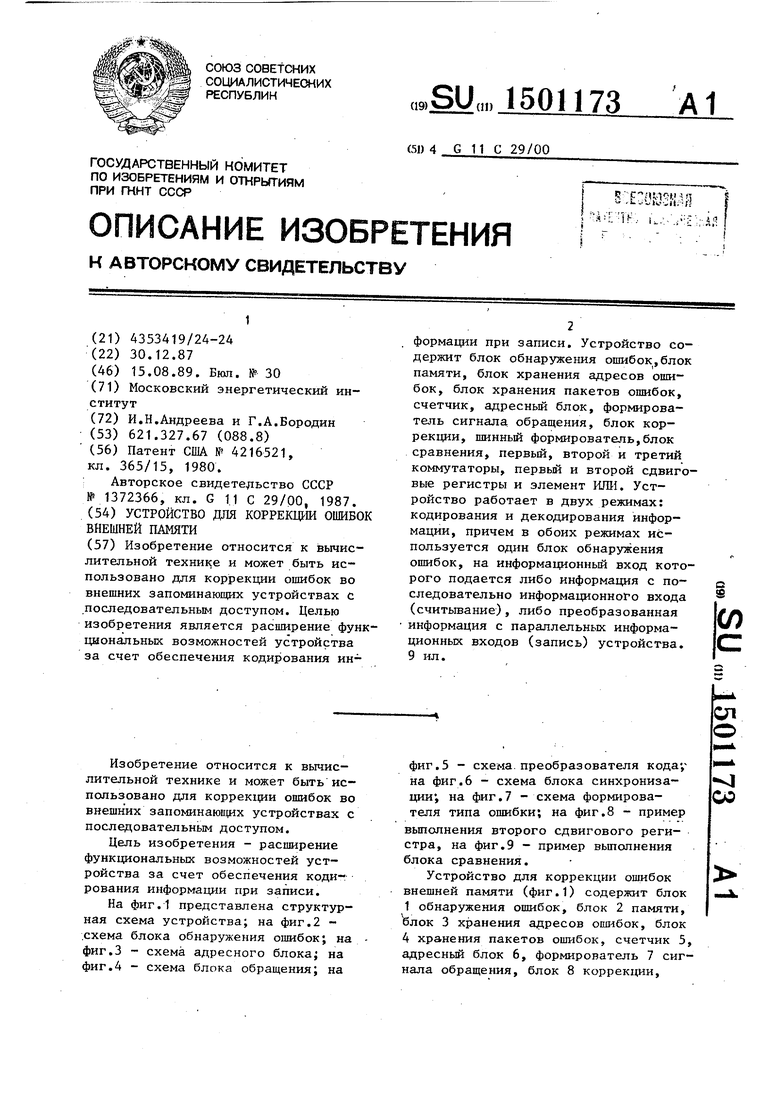

Изобретение относится к вычислительной технике и может быть использовано для коррекции ошибок во внешних запоминающих устройствах с последовательным доступом. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения кодирования информации при записи. Устройство содержит блок обнаружения ошибок, блок памяти, блок хранения адресов ошибок, блок хранения пакетов ошибок, счетчик, адресный блок, формирователь сигнала обращения, блок коррекции, шинный формирователь, блок сравнения, первый, второй и третий коммутаторы, первый и второй сдвиговые регистры и элемент ИЛИ. Устройство работает в двух режимах: кодирования и декодирования информации, причем в обоих режимах используется один блок обнаружения ошибок, на информационный вход которого подается либо информация с последовательно информационного входа (считывание, либо преобразованная информация с параллельных информационных входов (запись) устройства. 9 ил.

Изобретение относится к вычислительной технике и может быть использовано для коррекции ошибок во внешних запоминаюнщх устройствах с последовательным доступом.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения кодиг рования информации при записи.

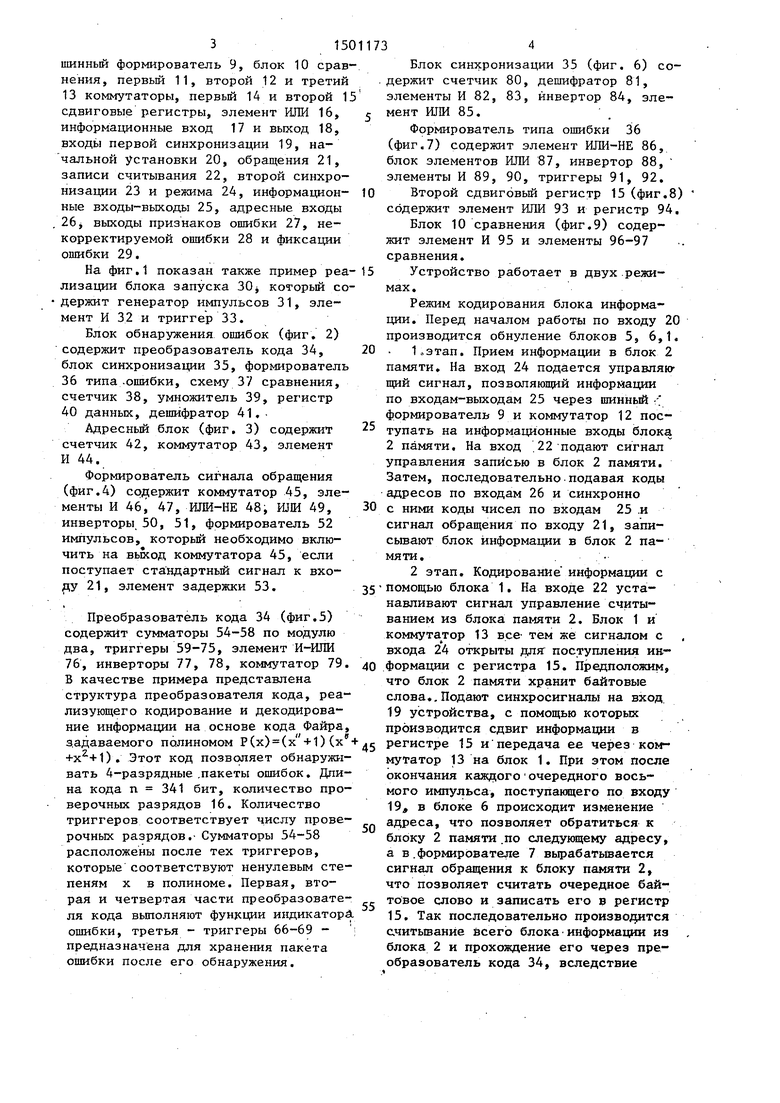

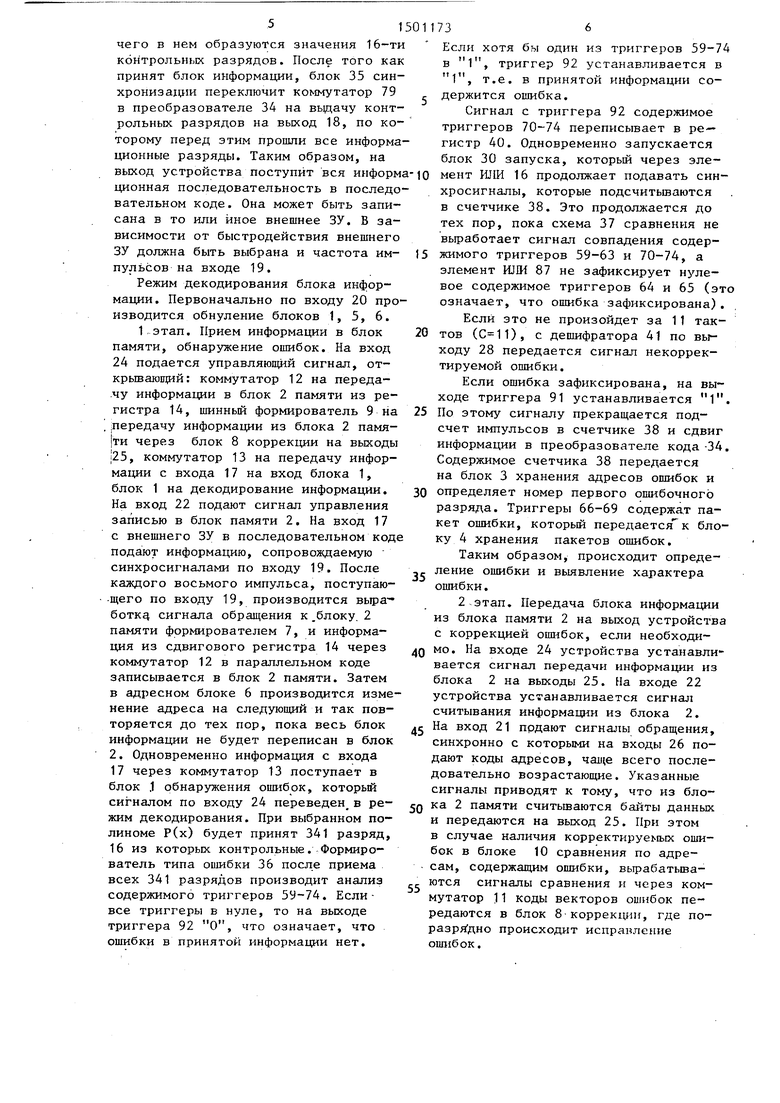

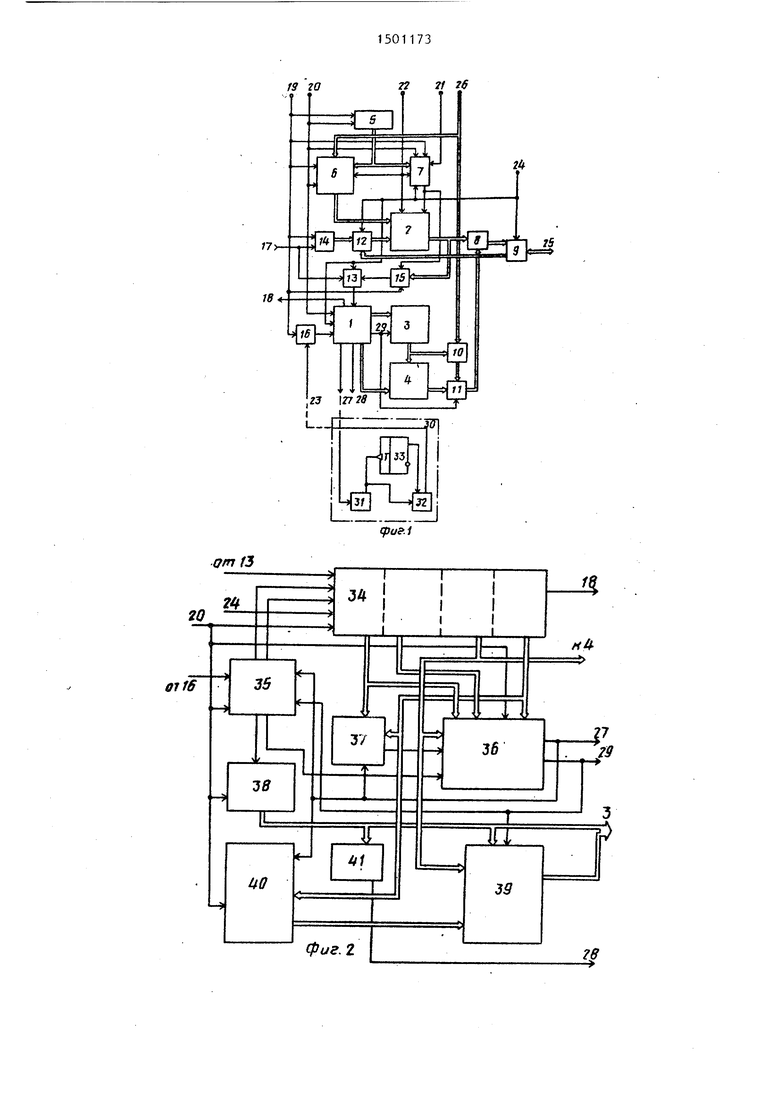

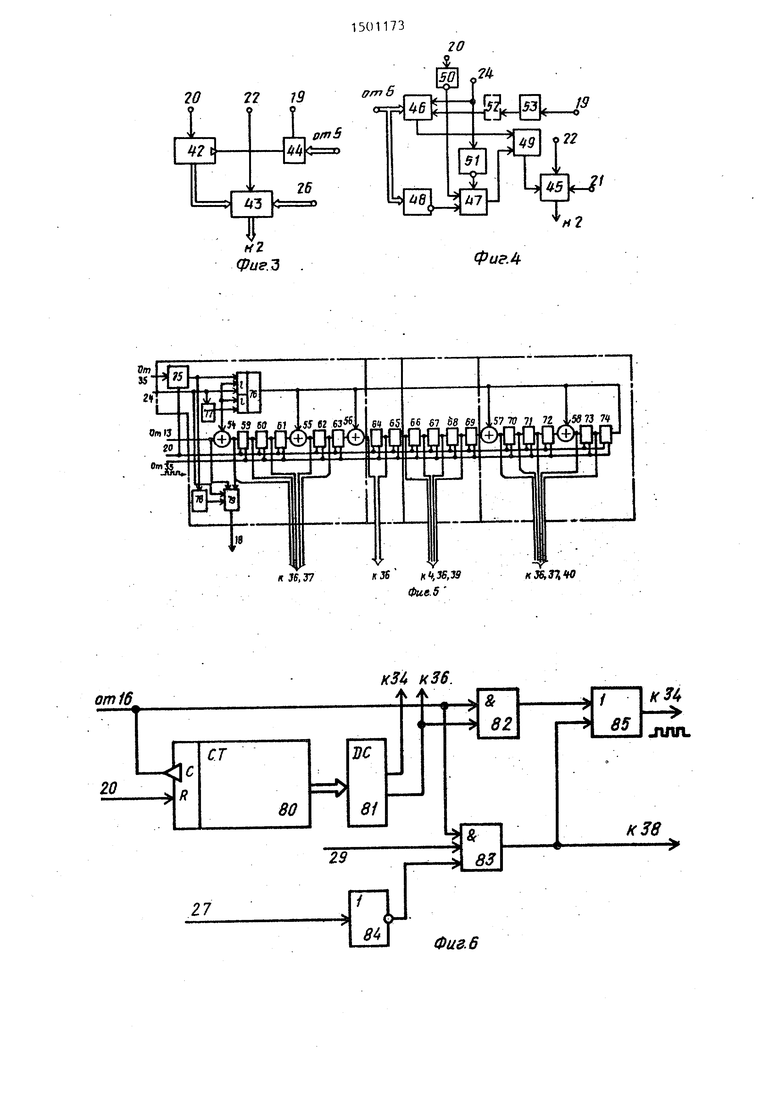

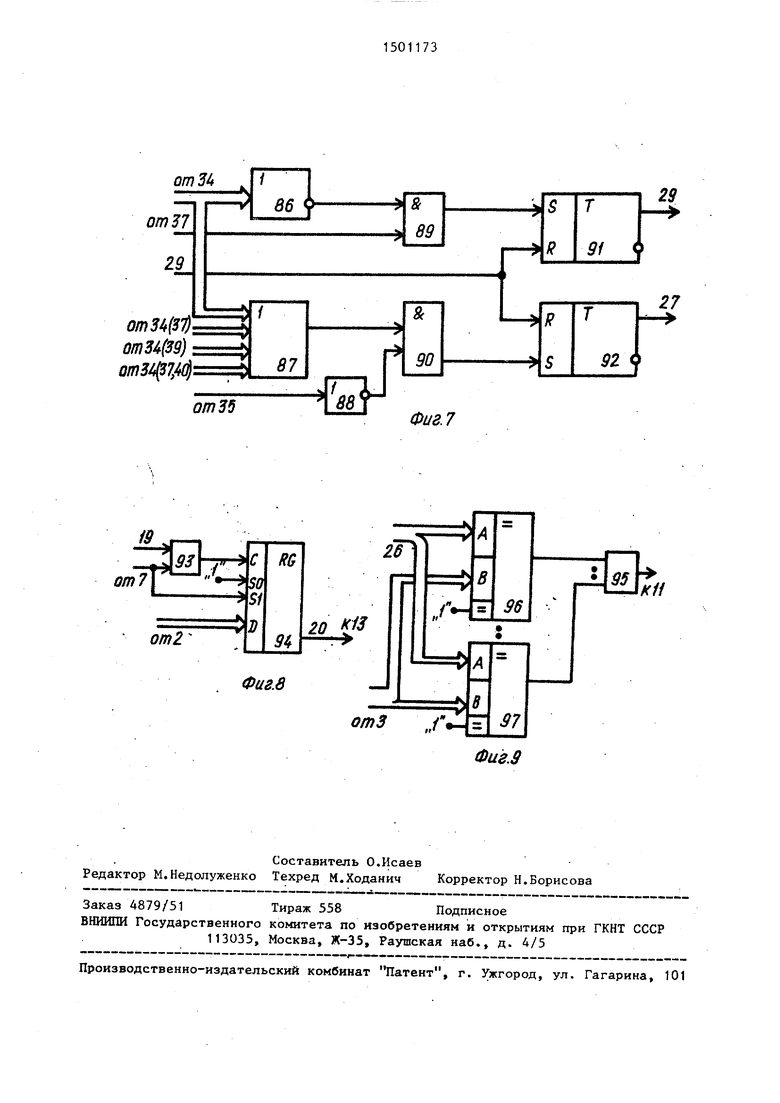

На фиг.1 представлена структурная схема устройства; на фиг.2 - .схема блока обнаружения ошибок; на фиг.З - схема адресного блока; на фиг.4 - схема блока обращения; на

фиг.5 - схема, преобразователя кода;- на фиг.6 - схема блока синхронизации; на фиг.7 - схема формирователя типа ошибки; на фиг.8 - пример выполнения второго сдвигового регистра, на фиг.9 - пример вьтолнения блока сравнения.

Устройство для коррекции ошибок внешней памяти (фиг.1) содержит блок 1 обнаружения ошибок, блок 2 памяти, блок 3 хранения адресов ошибок, блок 4 хранения пакетов ошибок, счетчик 5, адресный блок 6, формирователь 7 сигнала обращения, блок 8 коррекции.

vj

оо

шинньй формирователь 9, блок 10 сравнения, первый 11, второй 12 и третий 13 кoм fyтaтopы, первьй 14 и второй 15 сдвиговые регистры, элемент ИЛИ 16, информационные вход 17 и выход 18, входы первой синхронизации 19, начальной установки 20, обращения 21, записи считывания 22, второй синхронизации 23 и режима 24, информацион- ные входы-выходы 25, адресные входы 26j вькоды признаков ошибки 27, некорректируемой ошибки 28 и фиксации ошибки 29.

На фиг,1 показан также пример pea- лизации блока запуска 30j которьй содержит генератор импульсов 31, элемент И 32 и триггер 33.

Блок обнаружения ошибок (фиг, 2) содержит преобразователь кода 34, блок синхронизации 35, формирователь 36 типа-ошибки, схему 37 сравнения, счетчик 38, умножитель 39, регистр 40 данных, дешифратор 41,

Адресньй блок (фиг, 3) содержит счетчик 42, коммутатор 43, элемент И 44,

Формирователь сигнала обращения (фиг,4) ср;цержит коммутатор 45, элементы И 46, 47, ИЛИ-НЕ 48, ИЛИ 49, инверторы, 50, 51, формирователь 52 импульсов, который необходимо включить на вькод коммутатора 45, если поступает стандартньй сигнал к вхо- 21, элемент задержки 53,

Преобразователь кода 34 (фиг,5) содержит сумматоры 54-58 по модулю два, триггеры 59-75, элемент И-ИЛИ 76, инверторы 77, 78, коммутатор 79, В качестве примера представлена структура преобразователя кода, реализующего кодирование и декодирование информации на основе кода Файра, задаваемого полиномом Р(х) (х + 1)(х ). Этот код позвсшяет обнаруживать 4-разрядные .пакеты ошибок, Дпи- на кода п 341 бит, количество про- верочньсх разрядов 16, Количество триггеров соответствует числу проверочных разрядов,- Сумматоры 54-58 расположены после тех триггеров, которые соответствуют ненулевым степеням X в полиноме. Первая, вторая и четвертая части преобразовате- ля кода выполняют функции индикатора ошибки, третья - триггеры 66-69 - предназначена для хранения пакета ошибки после его обнаружения,

0

5

0 5

О

0

Блок синхронизации 35 (фиг, 6) содержит счетчик 80, дешифратор 81, элементы И 82, 83, инвертор 84, элемент ИЛИ 85,

Формирователь типа ошибки 36 (фиг.7) содержит элемент ИЛИ-НЕ 86, блок элементов ИЛИ 87, инвертор 88, элементы И 89, 90, триггеры 91, 92,

Второй сдвиговьй регистр 15 (фиг,8) содержит элемент ИЛИ 93 и регистр 94,

Блок 10 сравнения (фиг,9) содержит элемент И 95 и элементы 96-97 сравнения.

Устройство работает в двух .режимах.

Режим кодирования блока информации. Перед началом работы по входу 20 производится обнуление блоков 5, 6,1.

1оэтап. Прием информации в блок 2 памяти. На вход 24 подается управляю шзий сигнал, позволяющий информации по входам-выходам 25 через шинный :- формирователь 9 и коммутатор 12 поступать на информационные входы блока 2 памяти. На вход .22 подают сигнал управления записью в блок 2 памяти. Затем, последовательно подавая коды адресов по входам 26 и синхронно

с ними коды чисел по входам 25 .и сигнал обращения по входу 21, запи- сьюают блок информации в блок 2 памяти,.

2этап. Кодирование информации с помощью блока 1, На входе 22 устанавливают сигнал управление считыванием из блока памяти 2, Блок 1 и коммутатор 13 все- тем же сигналом с входа 24 открыты для поступления информации с регистра 15, Предположим, что блок 2 памяти хранит байтовые слова.. Подают синхросигналы на вход 19 устройства, с помощью которых производится сдвиг информации в регистре 15 и передача ее через коммутатор 13 на блок 1, При этом после окончания каждого очередного восьмого импульса, поступающего по входу 19, в блоке 6 происходит изменение адреса, что позволяет обратиться к блоку 2 памяти .по следукщему адресу, а в.формирователе 7 вьфабатьшается сигнал обращения к блоку памяти 2, что позволяет считать очередное байтовое слово и записать его в регистр 15, Так последовательно произво;р1Тся считьшание всего блока информации из блока 2 и прохождение его через преобразователь кода 34, вследствие

чего в нем образуются значения 16-ти кон трольных разрядов. После того как принят блок информации, блок 35 син- хронизащш переключит коммутатор 79 в преобразователе 34 на вьщачу контрольных разрядов на выход 18, по которому перед этим прошли все информационные разряды. Таким образом, на

выход устройства поступит вся информа-ю мент ИЛИ 16 продолжает подавать синционная последовательность в последовательном коде. Она может быть записана в то или иное внешнее ЗУ. В зависимости от быстродействия внешнего ЗУ должна быть выбрана и частота импульсов на входе 19.

Режим декодирования блока информации. Первоначально по входу 20 производится обнуление блоков 1, 5, 6.

1,этап. Прием информации в блок памяти, обнарз жение ошибок. На вход 24 подается управляющий сигнал, от- крываюищй: коммутатор 12 на переда- .чу информации в блок 2 памяти из регистра 14, шинньй формирователь 9 на ;Передачу информации из блока 2 памя- |ти через блок 8 коррекции на выходы 125, коммутатор 13 на передачу информации с входа 17 на вход блока 1, блок 1 на декодирование информации. На вход 22 подают сигнал управления записью в блок памяти 2. На вход 17 с внешнего ЗУ в последовательном код подают информацию, сопровождаемую синхросигналами по входу 19. После каждого восьмого импульса, поступаю- .щего по входу 19, производится выработку сигнала обращения к,блоку. 2 памяти формирователем 7, и информация из сдвигового регистра 14 через коммутатор 12 в параллельном коде записывается в блок 2 памяти. Затем в адресном блоке 6 производится изменение адреса на следующий и так повторяется до тех пор, пока весь блок информации не будет переписан в блок 2. Одновременно информация с входа 17 через коммутатор 13 поступает в блок .1 обнаружения ошибок, который сигналом по входу 24 переведен в режим декодирования. При выбранном полиноме Р(х) будет принят 341 разряд, 16 из которых контрольные. Формирователь типа ошибки 36 после приема всех 341 разрядов производит анализ содержимого триггеров 5У-74. Если- все триггеры в нуле, то на выходе триггера 92 О, что означает, что ошибки в принятой информации нет.

Если хотя бы один из триггеров 59-74 в 1, триггер 92 устанавливается в 1, т.е. в принятой информации содержится ошибка.

Сигнал с триггера 92 содержимое триггеров 70-74 переписывает в регистр 40. Одновременно запускается блок 30 запуска, который через эле0

0

хросигнапы, которые подсчитьшаются в счетчике 38. Это продолжается до тех пор, пока схема 37 сравнения не вьфаботает сигнал совпадения содер- 5 жимого триггеров 59-63 и 70-74, а элемент ИЛИ 87 не зафиксирует нулевое содержимое триггеров 64 и 65 (это означает, что ошибка зафиксирована). Если это не произойдет за 11 тактов (), с дешифратора 41 по выходу 28 передается сигнал некорректируемой ошибки.

Если ошибка зафиксирована, на выходе триггера 91 устанавливается 1. 5 По этому сигналу прекращается подсчет импульсов в счетчике 38 и сдвиг информации в преобразователе кода-34. Содержимое счетчика 38 передается на блок 3 хранения адресов ошибок и определяет номер первого ошибочного разряда. Триггеры 66-69 содержат пакет ошибки, который передается к блоку 4 хранения пакетов ошибок.

Таким образом, происходит определение ошибки и выявление характера ошибки.

2,этап. Передача блока информации из блока памяти 2 на выход устройства с коррекцией ошибок, если необходимо. На входе 24 устройства устанавливается сигнал передачи информации из блока 2 на выходы 25. На входе 22 устройства устанавливается сигнал считывания информации из блока 2. 5 На вход 21 прдают сигналы обращения, синхронно с которыми на входы 26 подают коды адресов, чаще всего последовательно возрастающие. Указанные сигналы приводят к тому, что из блока 2 памяти считьшаются байты данных и передаются на выход 25. При этом в случае наличия корректируемых ошибок в блоке 10 сравнения по адресам, содержащим ошибки, вырабатьша- ются сигналы сравнения и через коммутатор 11 коды векторов ошибок передаются в блок 8-коррекции, где по- разря дно происходит исправление ошибок.

5

0

0

5

ФорАула изобретения

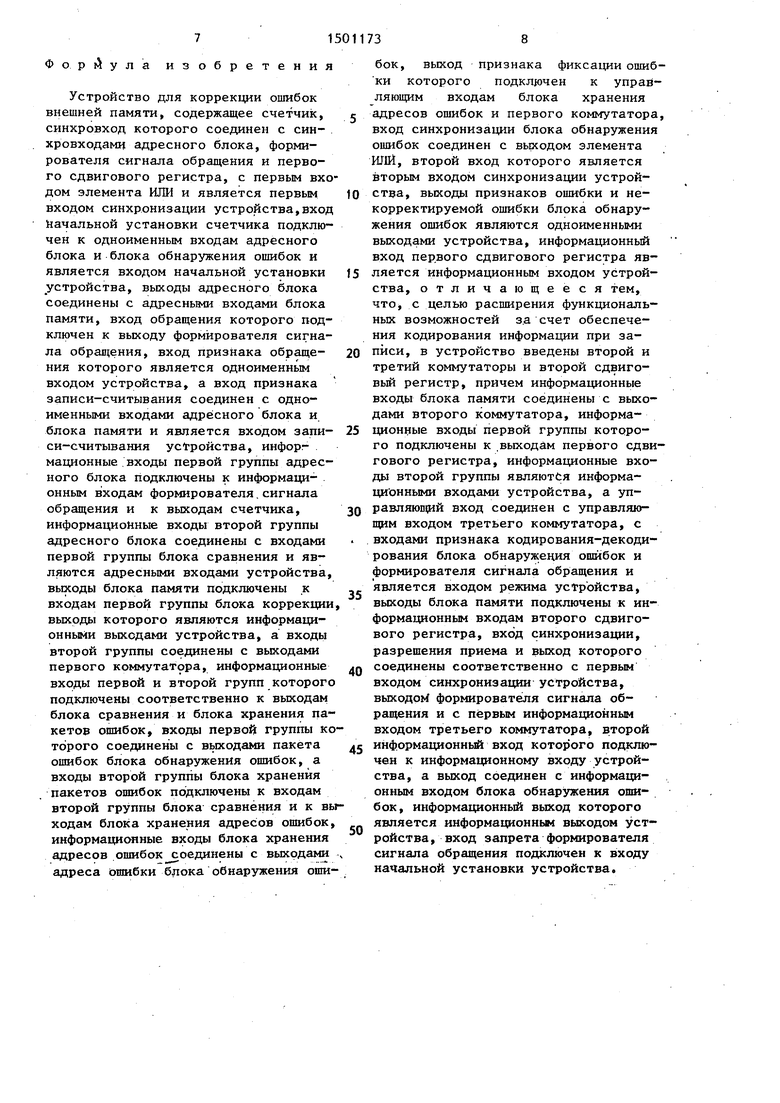

Устройство для коррекции ошибок внешней памяти, содержащее счетчик, синхровход которого соединен с син- хровходами адресного блока, формирователя сигнала обращения и первого сдвигового регистра, с первым входом элемента ИЛИ и является первым входом синхронизации устройства,вход Начальной установки счетчика подключен к одноименным входам адресного блока и блока обнаружения ошибок и является входом начальной установки устройства, выходы адресного блока соединены с адресными входами блока памяти, вход обращения которого подключен к выходу формирователя сигнала обралцения, вход признака обраще- ния которого является одноименньм входом устройства, а вход признака записи-считывания соединен с одноименными входами адресного блока и блока памяти и является входом запи- си-считывания устройства, инфорг- мационные входы первой группы адресного блока подключены к информаци- . онным входам формирователя.сигнала обращения и к выходам счетчика, информационные входы второй группы адресного блока соединены с входами первой группы блока сравнения и являются адресными входами устройства, выходы блока памяти подключены к входам первой группы блока коррекции вькоды которого являются информационными выходами устройства, а входы второй группы соединены с выходами первого коммутатора, информационные входы первой и второй групп которого подключены соответственно к выходам блока сравнения и блока хранения па кетов ошибок, входы первой группы которого соединены с вьгходами пакета ошибок блока обнаружения ошибок, а входы второй группы блока хранения пакетов ошибок подключены к входам второй группы блока сравнения и к выходам блока хранения адресов ошибок, информационные входы блока хранения адресов ошибок соединены с выходами адреса ошибки блока обнаружения ошибок, выход признака фиксации ошиб ки которого подключен к упрай ляющим входам блока хранения адресов ошибок и первого коммутатора вход синхронизации блока обнаружения ошибок соединен с вьгходом элемента ИЛИ, второй вход которого является вторым входом синхронизации устройства, выходы признаков ошибки и некорректируемой ошибки блока обнаружения ошибок являются одноименными выходами устройства, информационный вход первого сдвигового регистра является информационным входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей з.а счет обеспечения кодирования информации при записи, в устройство введены второй и третий коммутаторы и второй сдвиго- вьй регистр, причем информационные входы блока памяти соединены с выходами второго коммутатора, информационные входы первой группы которого подключены к .выходам первого сдвигового регистра, информационные входы второй группы являются информационными входами устройства, а уп- равляюп(ий вход соединен с управляющим входом третьего коммутатора, с входами признака кодирования-декодирования блока обнарузкения ошибок и формирователя сигнала обращения и является входом режима устройства, выходы блока памяти подключены к информационным входам второго сдвигового регистра, вход синхронизагщи, разрешения приема и выход которого соединены соответственно с первым входом синхронизации устройства, выходом формирователя сигнала обращения и с первым информахщонным входом третьего коммутатора, второй информационньй вход которого подключен к информационному входу устройства, а выход соединен с информационным входом блока обнаружения ошибок, информационный выход которого является информационным выходом устройства , вход запрета формирователя сигнала обращения подключен к входу начальной установки устройства.

13 га

от f3

72 л гб

4

я J5,J7

am В

OSjpiUfi

ФигЛ

К 36 кt,3e,39 Фие.5

K36,31W

| Патент США № 4216521, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-08-15—Публикация

1987-12-30—Подача