(54).УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ N-ОЙ СТЕПЕНИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения корня -ой степени | 1973 |

|

SU491946A1 |

| Устройство для извлечения корня @ -й степени | 1984 |

|

SU1223225A2 |

| Устройство для кусочно-линейной интерполяции функций | 1983 |

|

SU1215117A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

Изобретение относится к цифровой вычислительной техники и может быть использовано при построении цифровых вычислительных машин. Известно устройство для вычислеш1 функции Z . Недостатком известного устройства является значительная сложность. Наиболее близким к предлагаемому по технической сущности является устройство для извлечения корня степени, содержащее блок управления, регистр начального коэффициента, регистр аргумента, регистр результата-, коммутатор младшего коэффициента и п-1 сдвиговых регистров 2j. Недостатком известного устройства является зависимость состава оборудования от степени п извлекаемого корня, так как для извлечения корня п-й степени необходимо иметь п-1 взаимносвязанных сдвиговых регистров и сумматоров и с увеличением степени п необходимо соответственно увеличивать количество блоков устройства. Цель изобретения - сокращение аппаратуры при повьшении степени п извлекаемого корня. Поставленная цель достигается тем, что в устройство для извлечения корня п -ой степени, содержащее сдвиговый регистр, вход и выход которого соединены соответственно с выходом и входом сумматора, вход которого соединен с регистром аргумента, вход которого подключен к первому управляющему выходу блока управления, второй и третий управляющие выходы которого соединены соответственно с первыми входами коммутатора результата и коммутатора младшего коэффициента, вторые вхоfsjbt которых подключены к выходу знакового разряда сумматора и выходу регистра результата, входом соединенного с выходом коммутатора результата, четвертый управляющий выход блока управления соединен со входом сдвига сдвигового регистра и первым входом регистра начального коэффициента, выходом подключенного ко входу знакового разряда сумматора, введен формируюищй-коммутатор первый вхрд которого соединен с пятым управляющим выходом блока управления , второй вход - с выходом сдвигового регистра, третий вход - с выходом коммутатора младшего коэффициента, соединенного со входом сумматора, выход формирующего коммутатора подключен ко второму входу регистра начального коэффициента.

При этом, в устройстве формирующий коммутатор содержит элемент НЕ, вход которого является первым входом коммутатора, а выход соединенс первыми входами элементов И первой группы, а вход элемента НЕ - с первыми входами элементов И второй группы и является выходом формирующего коммутатора, вторые входы элементов И первой и второй групп явлг-ются соответственно вторым и третьим входами коммутатора, а их выходы подключены соответственно к первым и вторым входам элементов ИЛИ, выход которых является выходом форми- рующего коммутатора.

Кроме того, блок управления содержит последовательно соединенные мультиплексор, счетчик адреса, блок памяти и дешифратор микрокоманд,выходы с первого по пятый которого являются соответствующими выходами блока управле1т я, выход блока памяти подключен ко входу мультиплексора, . управляющий вхоД которого соединен с выходом счетчика переходов, подключенного входом.к выходу признака перехода блока памяти.

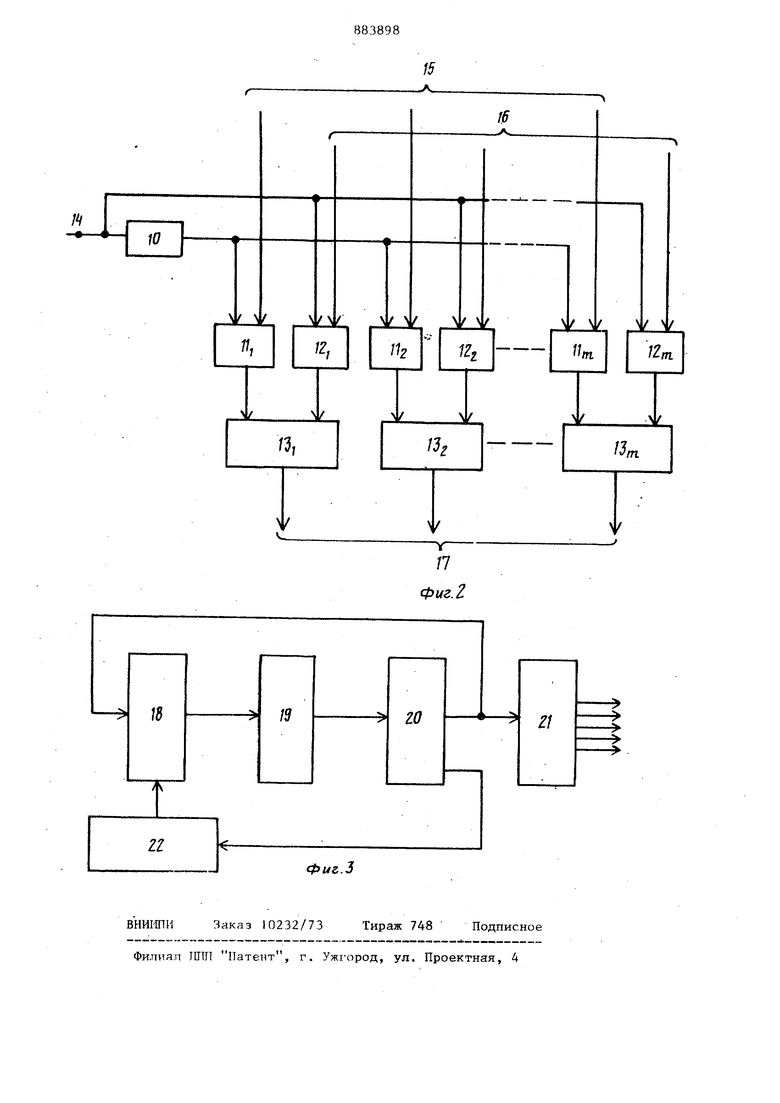

На фиг.1 представлена блок-схема предлагаемого ус-тройства-; на фиг.2пример выполнения формирующего коммутатора; на фиг.З - возможный вариант выполнения блока управления.

Устройство содержит блок 1 управления,регистр 2 начального коэффицйента, регистр 3 аргкмента, регист 4 результата, коммутатор 5 младшего коэффициента, коммутатор 6 результата, формирующий коммутатор 7, сдвиговьш регистр 8, взаимно связанный с сумматором 9.

Формирующий коммутатор (фиг.2), содержит элемент НЕ 10, группы 11 и 12 элементов И, элементы ИЛИ 13,

входы 14 - 16, выход 17 формирующего коммутатора.

Блок управления (фиг.З содержит мультиплексор 18, счетчик 19 адреса, 5 блок 20 памяти, дешифратор 21 микрокоманд, счечтик 22 переходов.

Вычисляем у:

Y , Ц 0,

10 Перед началом работы аргумент 0,438 заносится в регистр 3 аргумента. Количество разрядов m в регистрах и сумматоре предлагаемого устройства выбирают исходя из требуемой точнос)5 ти вычисления искомого значения корня. Дпя определенности положим гп 5.. Вычисление искомого значения корня длится m циклов.

Блок управления работает следую2(j щим образом.

Счетчик адреса 19 наращивается по каждому такту синхросигналов, кроме случая выполнения условного перехода, и формирует очередной

5 адрес для блока 20 памяти. По каждому адресу из блока 20 считывается слово микропрограммы, которое дешифруется на дешифраторе микрокоманд 21. Выходы дешифратора являются выходами блока управления. В случае.наличия в слое микрокоманды признака условного перехода поступление синхросигналов на счетчик 19 адресов блокируется и наращивается счетчик переходов 22, управляющий мультиплексором 18. Одновременно один из адресов условного перехода, поступающий из блока 20 через мультиплексор 18, загружается в счетчик 19 адреса. Таким образом, из. блока 20 извлекается слово микропрограммы, соответствующее адресу условного перехода.

В начале первого цикла блок 1 управления через коммутатор младшего коэффициента 5, формирующий коммутатор 7, записывает единицу в первый справа после запятой разряд регистра 2 начального коэффициента, т.е. заносит код 0,10000. Такой

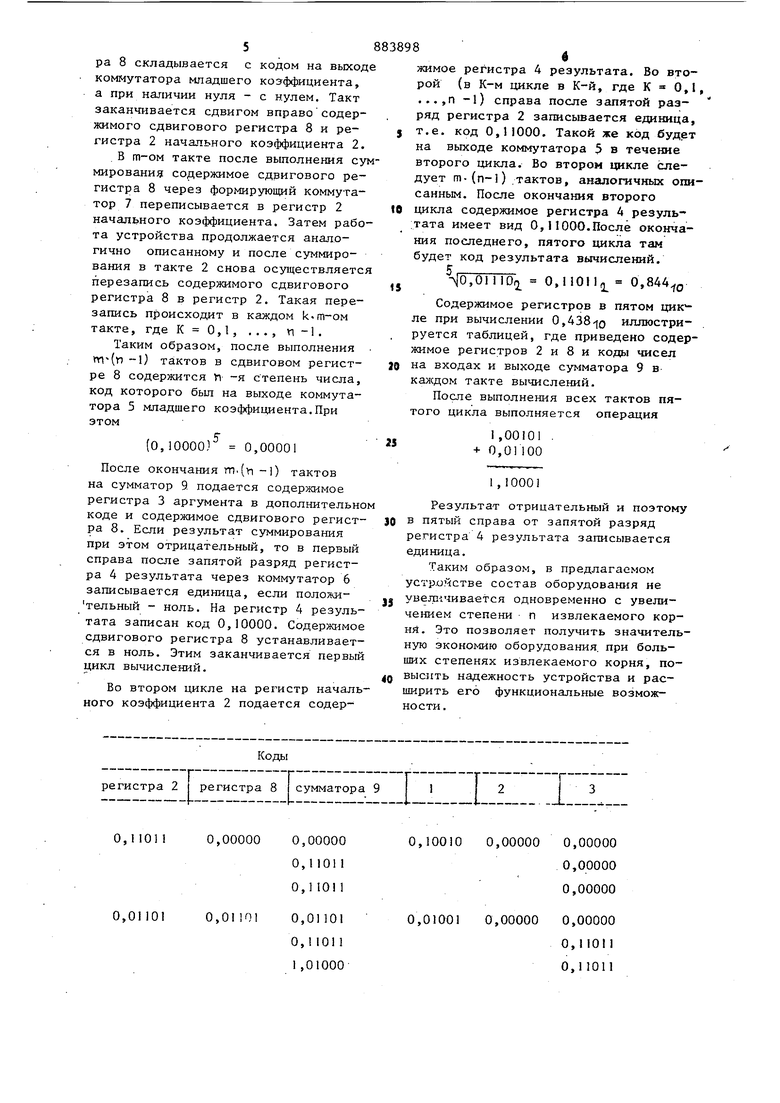

же код будет на выходе коммутатора 5 младшего коэффициента в течение всего первого цикла. Каждый цикл состоит из m.(n-l) тактов. В каждом такте происходит суммирование 5 на сумматоре 9 таким образом, что при наличии единицы в младшем разряде регистра начального коэффициента 2 содержимое сдвигового регист5pa 8 складывается с кодом на выход коммутатора младшего коэффициента, а при наличии нуля - с нулем. Такт заканчивается сдвигом вправо содержимого сдвигового регистра 8 и регистра 2 начального коэффициента 2. В т-ом такте после выполнения су мирования содержимое сдвигового регистра 8 через формирующий коммутатор 7 переписывается в регистр 2 начального коэффициента. Затем рабо та устройства продолжается аналогично описанному и после суммирования в такте 2 снова осу1цествляетс перезапись содержимого сдвигового регистра 8 в регистр 2. Такая перезапись происходит в каждом k-rti-OM такте, где К 0,1, ..., п-1. Таким образом, после выполнения m(n -1) тактов в сдвиговом регистре 8 содержится Vi -я степень числа, код которого был на выходе коммутатора 5 младшего коэффициента.При этом (0,10000) 0,00001 После окончания rri(vi -1) тактов на сумматор 9. подается содержимое регистра 3 аргумента в дополнительн коде и содержимое сдвигового регист ра 8. Если результат суммирования при этом отрицательный, то в первый справа после запятой разряд регистра 4 результата через коммутатор 6 записывается единица, если положительный - ноль. На регистр 4 резуль тата записан код 0,10000. Содержимо сдвигового регистра 8 устанавливает ся в ноль. Этим заканчивается первы цикл вычислений. Во втором цикле на регистр началь ного коэффициента 2 подается содеррегистра 2 регистра 8 сумматора 9

регистра 8

i::::iz:::i 8 жимое регистра 4 результата. Во второй (в К-м цикле в К-й, где К 0,1, ...,п -1) справа после запятой разряд регистра 2 записывается единица, т.е. код 0,11000. Такой же код будет на выходе коммутатора 5 в течение второго цикла. Во втором цикле следует m-{n-l) .тактов, аналогичных описанньм. После окончания второго цикла содержимое регистра А резуль;тата имеет вид 0,11000.После окончания последнего, пятого цикла там будет код результата вычислений. 5, ,01 ПО 0,110112 0, Содержимое регистров в пятом при вычислении 0,43810 иллюстрируется таблицей, где приведено содержимое регистров 2 и 8 и коды чисел на входах и выходе сумматора 9 в каясдом такте вычислений. После выполнения всех тактов пятого цикла выполняется операция 1,00101 . + 0,01100 1,10001 Результат отрицательный и поэтому в пятый справа от запятой разряд регистра 4 результата записывается единица. Таким образом, в предлагаемом устройстве состав оборудования не увелг чивается одновременно с увеличением степени п извлекаемого корня. Это позволяет получить значительную экономию оборудования, при больших степенях извлекаемого корня, повысить надежность устройства и расширить его функциональные возможности.

Формула изобртения 1. Устройство для извлечения кор ня п-ой степени, содержащее сдвиговый регистр, вход и выход которого соединены соответственно с выходом и входом сумматора, вход которого соединен с регистром аргумента, вхо; которого подключен к первому управПродолжение табли1ф1

ляющему выходу блока управления,второй и третий управляющие выходы которого соединены соответственно с первыми входами коммутатора результата и коммутатора младшего коэффициента, вторые входы которых подключены к выходу знакового разряда сумматора и выходу регистра результата, входом соединенного с выходом коммутатора результата, четвертый управлягаций выход блока управления соединен со входом сдвига сдвигового регистра и первым входом регистра начального коэффициента,выходом подключенного ко входу знакового разряда сумматора, о т л ичающее с я тем, что с целью сокращения аппаратуры при повышении степени rt извлекаемого корня, в него введен формирующий коммутатор, первьй вход которого соединен с пятым управляющим выходом блока управления, второй вход - с выходом сдвигового регистра, третий вход - с выходом коммутатора мпадшего коэффициента, соединенного со входом сумматора, выход формирующего коммутатора подк 1ючен ко второму входу регистра начального коэффициента.

выходом формирующего коммутатора, вторые входы элементов И первой и второй групп являются соответственно вторым и третьим входами коммутатора, а их выходы подключены соответственно к первым и вторым входам элементов ИЛИ, выход которых является -выходом формирующего коммутатора.

to 3. Устройство по п.1,0 тли ч аю щ е е с я тем, что блок управления содержит последовательно соединенные мультиплексор, счетчик адреса, блок памяти и дешифратор микрокоманд, 15 выходы с первого по пятый которого являются соответствующими выходами блока управления, выход блока памяти подключен ко входу мультиплексора, управляющий вход которого соединен 20 выходом счетчика переходов, подключенного входом к выходу признака перехода блока памяти.

Источники информации, принятые во внимание при экспертизе

13

/5

15

А

фиг. 2

-

20

//

Авторы

Даты

1981-11-23—Публикация

1979-12-27—Подача