СП

1

оо со ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| Устройство для управления ленточным перфоратором | 1987 |

|

SU1451737A1 |

| Устройство для контроля считываемой информации | 1982 |

|

SU1056200A1 |

| Измерительная система | 1987 |

|

SU1474718A1 |

| Устройство для ввода информации | 1983 |

|

SU1113795A1 |

| Устройство для регистрации данных по табельному учету | 1982 |

|

SU1027746A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Устройство для отсчета времени | 1990 |

|

SU1817085A1 |

Изобретение относится к цифровой регистрации энергетических параметров в системах энергоснабжения промышленных предприятий и позволяет повысить достоверность регистрации. В устройство введены последовательно соединенные преобразователь 6 аналогового сигнала в частоту и первый счетчик 7 в каждый измерительный канал 2. Измеряемый параметр преобразуется в аналоговый сигнал и далее в частоту импульсов. Информация в параллельном коде поступает с выходов первого счетчика 7 каждого измерительного канала на соответствующие информационные входы блока 3 коммутатора каналов. Блок 4 синхронизации находится в одном из трех режимов работы: режим ожидания, режим запуска двигателя перфоратора и режим перфорации. 5 з.п.ф-лы, 6 ил.

Фиг.1

Изобретение относится к цифровой регистрации энергетических параметров (величины тока, напряжения, активной и реактивной мощности, частоты переменного напряжения, показателей качества электроэнергии, давления и температуры жидкостей и газов,расхода и уровня жидкостей) в системах энергоснабжения промышленных предприятий.

Цель изобретения - повышение достоверности измерения.

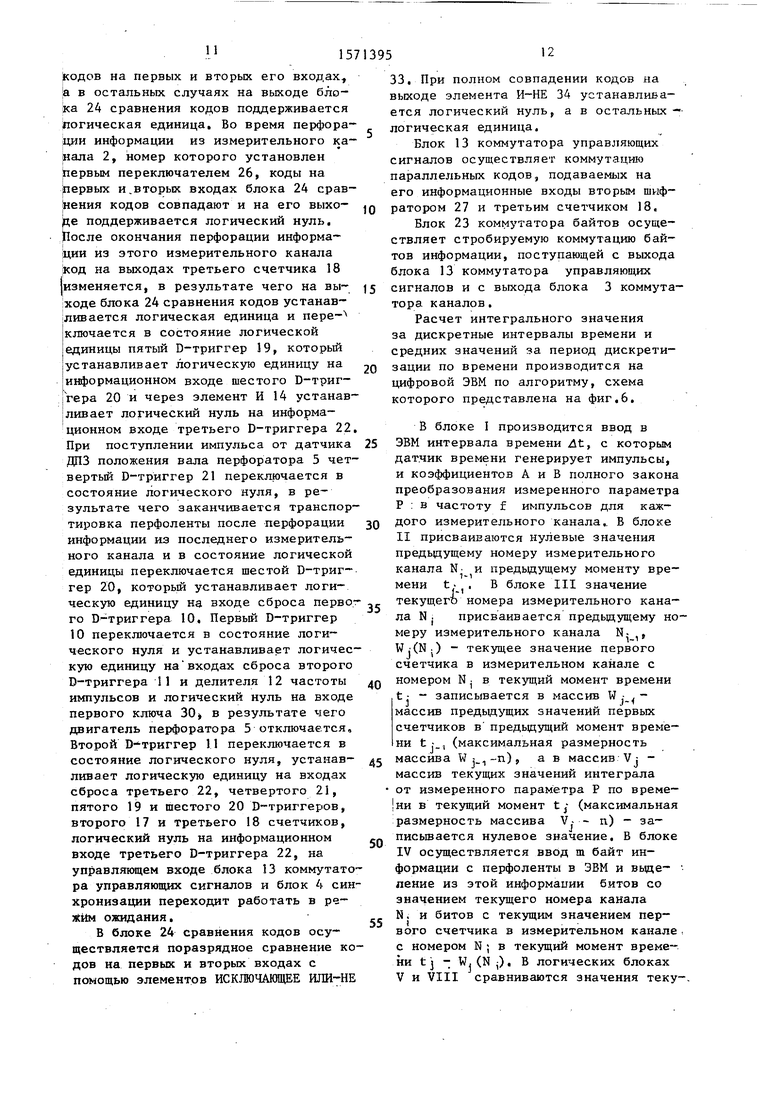

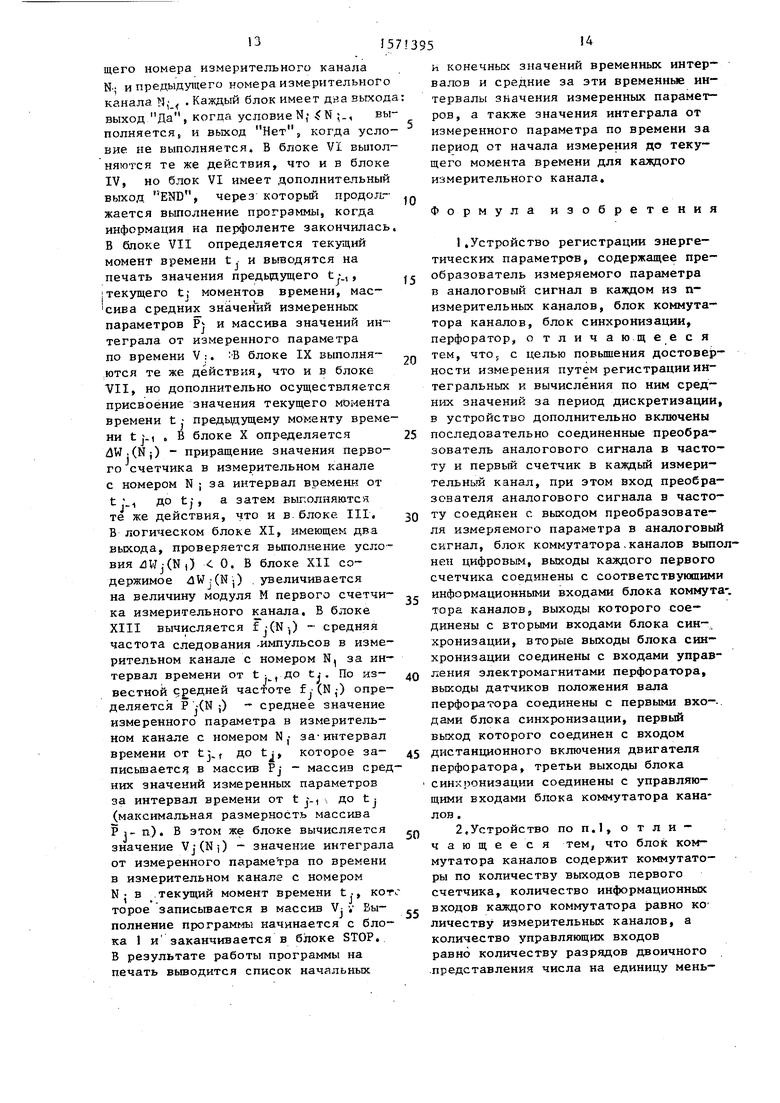

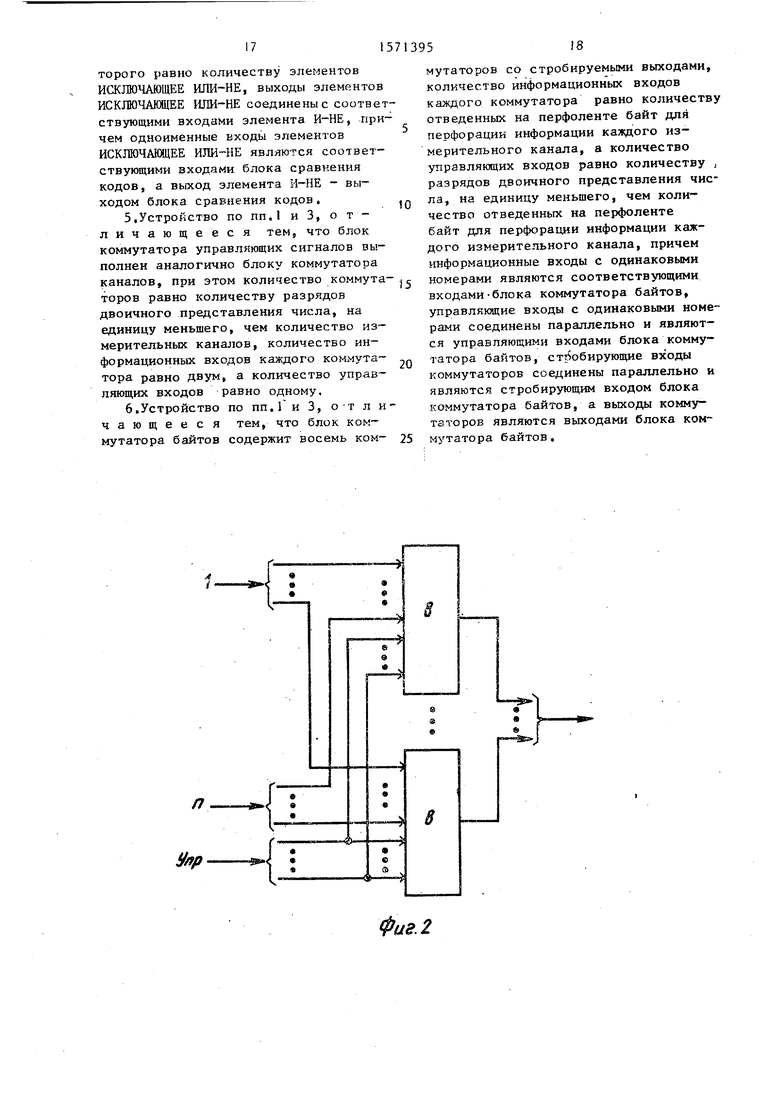

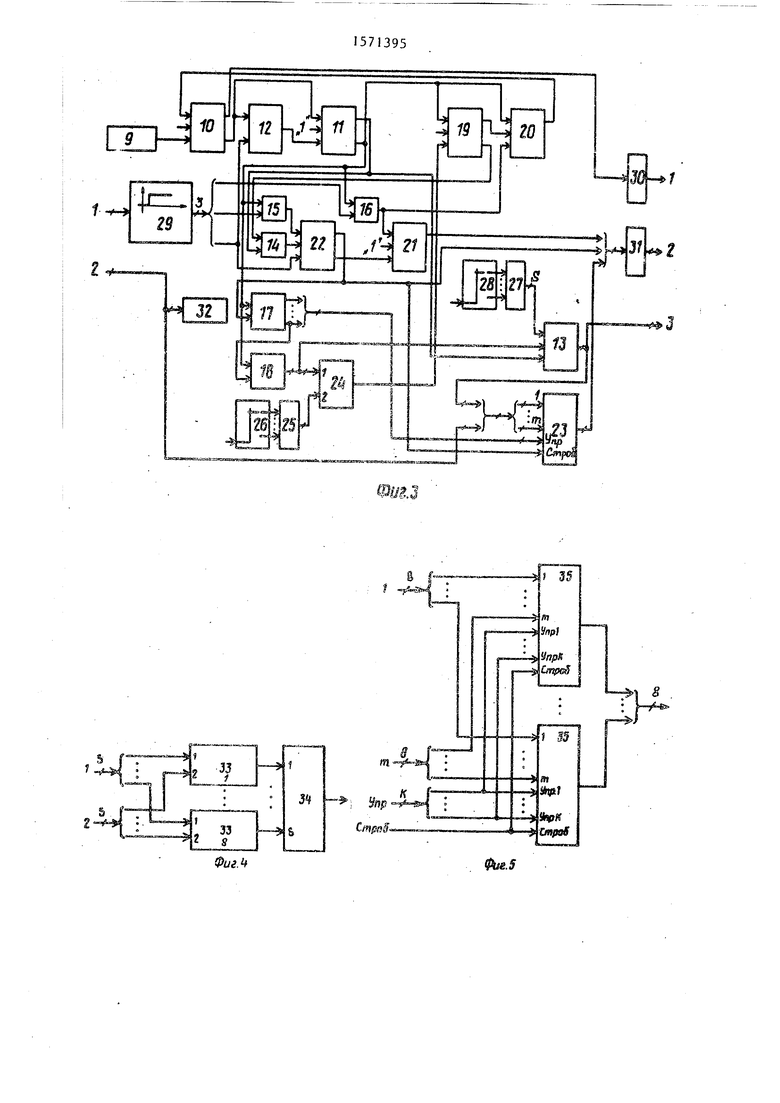

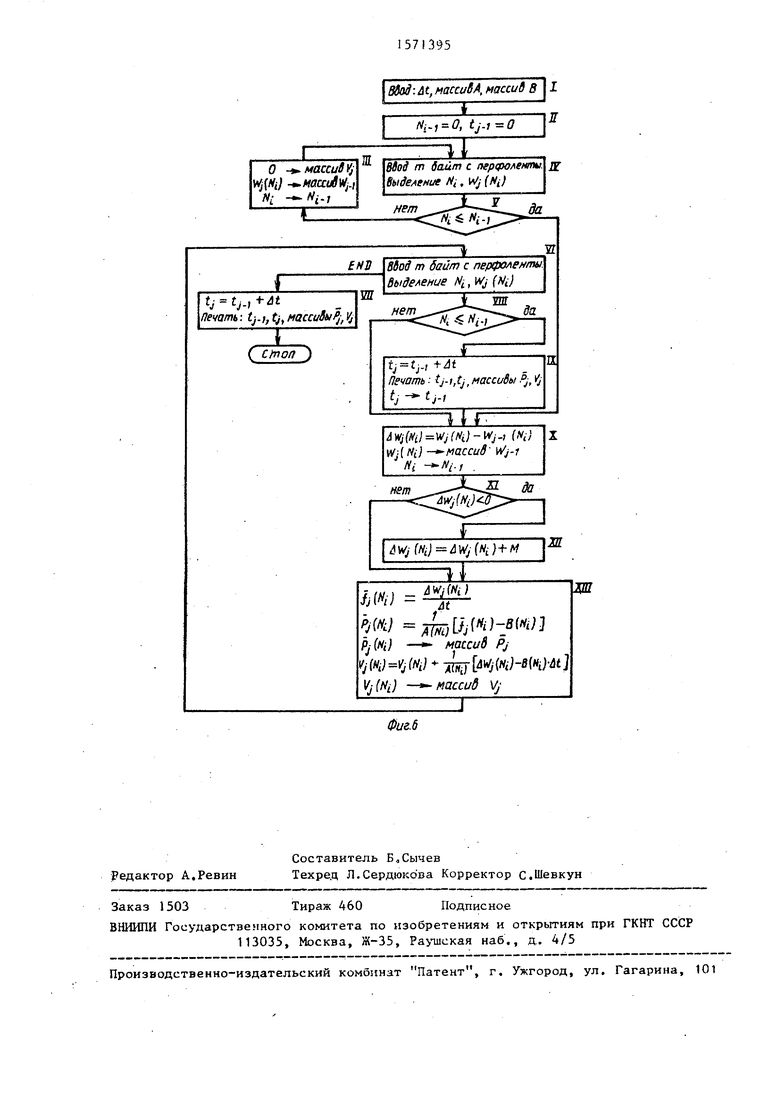

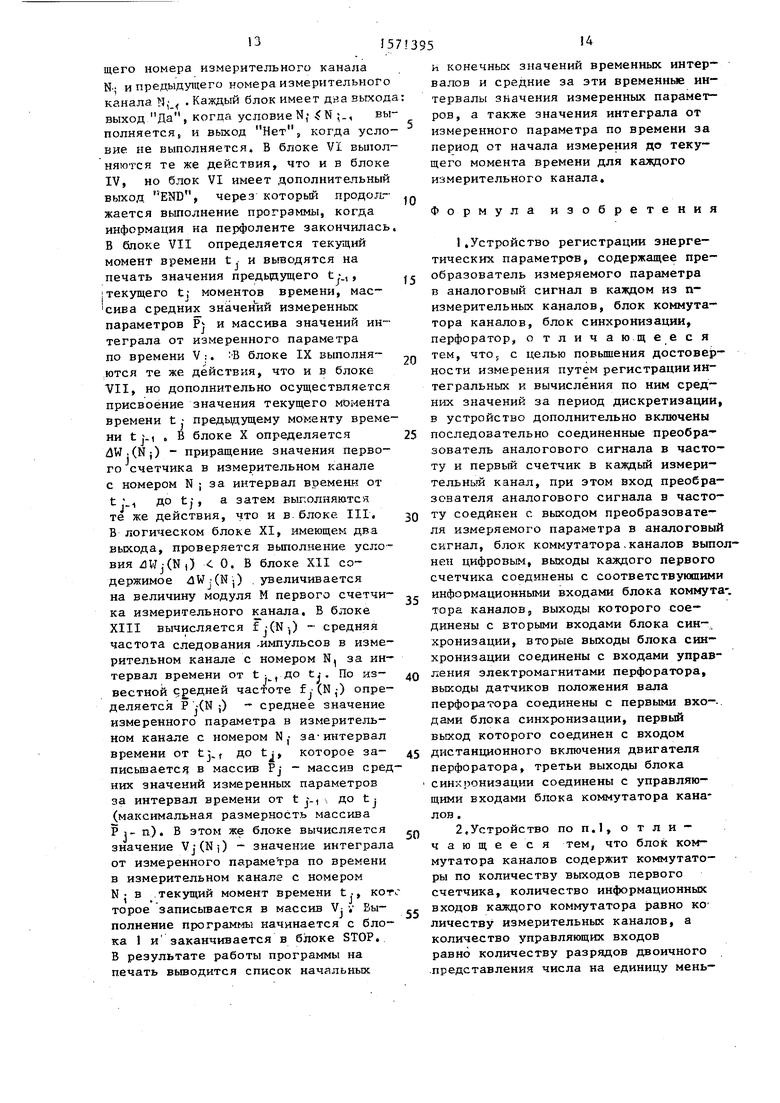

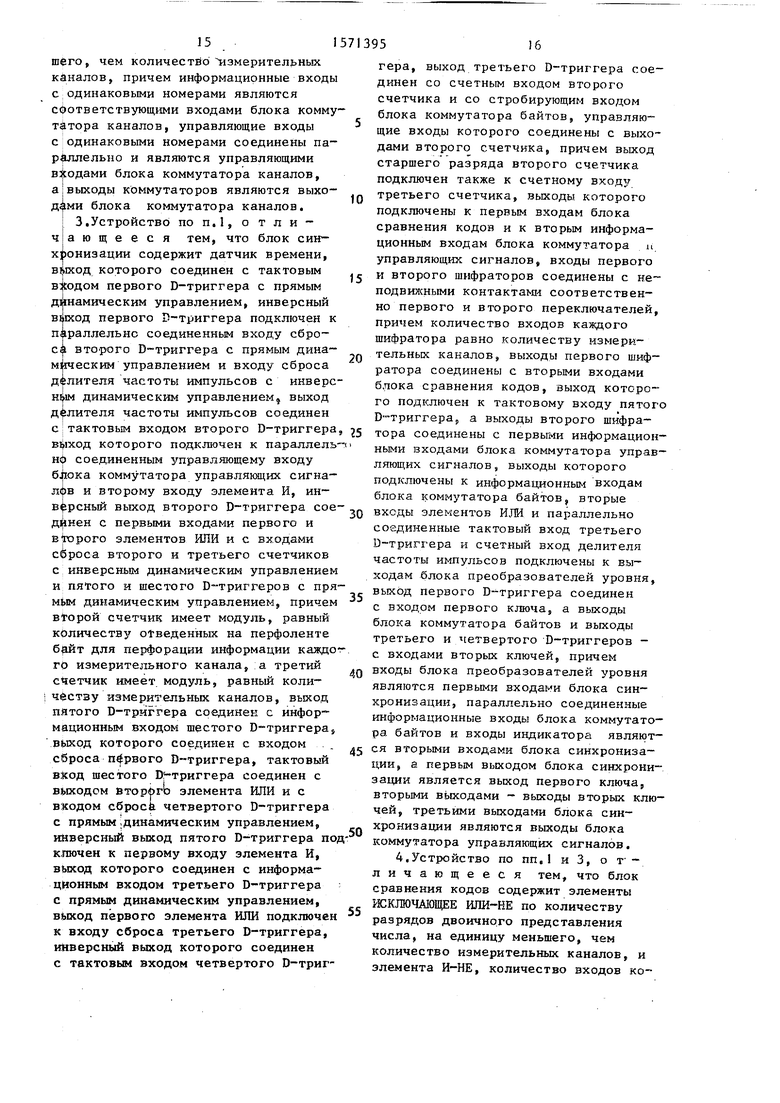

На фиг.1 изображена схема предлагаемого устройства; на фиг.2 - схема блока коммутатора каналов; на фиг.З - схема блока синхронизации; на фиг.4 - схема блока сравнения кодов; на фиг,5 - схема блока коммутатора байтов; на фиг.6 - схема алгоритма программы расчета на цифровой ЭВМ интегрального значения за дискретные интервалы времени и средних значений за период дискретизации по времени.

На фиг.4 - фиг.6 приняты следующие обозначения:

п - количество измерительных каг налов (п 2) ;

S - количество разрядов двоично- ного представления числа п-1;

q - количество разрядов первого счетчика в измерительном канале ;

TS+qJK „

т д 1 количество байт, отводимых

на перфоленте для перфорации информации каждого измерительного канала (т 2), где символ означает округление до ближайшего большего целого числа; К количество разрядов двоичного

представления числа m - 1. Устройство содержит преобразователь 1 измеряемого параметра в аналоговый сигнал в каждом измерительном канале 2, блок 3 коммутатора, блок 4 синхронизации и перфоратор 5 (например, перфоратор ПЛ-80). В устройство дополнительно включены последовательно соединенные преобразователь 6 аналогового сигнала в частоту и первый счетчик 7 в каждый измерительный канал 2. Вход преобразователя 6 аналогового сигнала в частоту соединен с выходом преобразователя 1 измеряемого параметра в аналоговый сигнал. Блок 3 коммутатора каналов выполнен цифровым. Выходы

каждого первого счетчика 7 соединены с соответствующими информационными входами блока 3 коммутатора каналов, выходы которого соединены со вторыми входами блока 4 синхронизации. Вторые выходы блока 4 синхронизации соединены с входами управления электромагнитами перфоратора 5. Выходы датчиков положения вала перфоратора 5 соединены с первыми входами блока 4 синхронизации, первый выход которого соединен со входом дистанционного включения двигателя перфоратора

Блок 3 коммутатора каналов содержит коммутаторы 8 по количеству q

0 выходов первого счетчика 7. Количество информационных входов каждого коммутатора 8 равно количеству п измерительных каналов 2, а количество управляющих входов равно количеству S

5 разрядов двоичного представления

числа, на единицу меньшего, чем количество п измерительных каналов 2. Информационные входы с одинаковыми номерами являются соответствующими

0 входами блока 3 коммутатора каналов, а управляющие входы с одинаковыми номерами соединены параллельно и являются управляющими входами блока 3 коммутатора каналов, Выходы коммутаторов 8

с являются выходами блока 3 коммутатора каналов.

Блок 4 синхронизации содержит датчик 9 времени, выход которого соединен с тактовым входом первого D-триг0 гера 10 с прямым динамическим управлением, Инверсный выход первого D- триггера 10 подключен к параллельно соединенным входу сброса второго D- триггера 11 с прямым динамическим

управлением и входу сброса делителя 12 частоты импульсов с инверсным динамическим управлением. Выход делитеп- ля 12 частоты импульсов соединен с тактовым входом второго D-триггера

o 11, выход которого подключен параллельно соединенным управляющему входу блока 13 коммутатора управляющих сигналов и второму входу элемента И 14. Инверсный выход второго Ь-триг- гера 11 соединен с первым входом первого элемента ИЛИ 15, с первым входом второго элемента ИЛИ 16, с входом сброса второго счетчика 17 с инверсным динамическим управлением, с вхо-

5

дом сброса третьего счетчика 18 с инверсным динамическим управлением, с входом сброса пятого D-триггера 19 с прямым динамическим управлением и с входом сброса шестого D-триггера 20 с прямым динамическим управлением Второй счзтчик 17 имеет модуль, равный количеству гя отведенных на перфоленте байт для перфорации информации каждого измерительного канала, а третий счетчик 8 имеет модуль, равный количеству измерительных каналов. Выход пятого D-триггера 19 соединен с информационным входом шестого D-триггера 20, выход которого соединен с входом сброса первого D-триггера 10. Тактовый вход шестого D триггера 20 соединен с выходом второго элемента ИЛИ 16 и с входов сброса четвертого D-триггера 21 с прямым динамическим управлением. Инверсный выход пятого D-триггера 9 подключен к первому входу элемента И 14j выход которого соединен с ин-

формационным входом третьего D-триг- гера 22 с прямым динамическим управлением. Выход первого элемента ИЛИ 15 подключен к входу сброса третьего D-триггера 22, инверсный выход которого соединен с тактовым входом четвертого D-тркггера 21, Выход третьего D-триггера 22 соединен со счетным входом второго счетчика 17 и со стробирующим входом блока 23 коммутатора байтов, управляющие входы которого соединены с выходами второго счетчика 17„ Выход старшего разряда второго счетчика 17 подключен также к счетному входу третьего счетчика 18, выходы которого подключены к первым входам блока 24 сравнения кодов и к вторым информационным входам блока 13 коммутатора управляющих сигналов, Входы первого 25 и второго 27 шифраторов соединены с неподвижными контактами соответственно первого 26 и второго 28 переключателей, причем количество входов каждого шифратора равно количеству п измерительных каналов. Выходы первого шифратора 25 соединены со вторыми входами блока 24 сравнения кодов, выход которого подключен к тактовому входу пятого D-триггера 199 а выходы второго шифратора 27 соединены с первыми информационными входами блока 13 коммутатора управляющих сигналов, выходы которого подключены к инфор . 10

15

,

5713956

мационным входам блока 23 коммутатора байтов. Второй вход первого элемента ИЛИ 15, второй вход второго элемента ИЛИ 16 и параллельно соединенные тактовый вход третьего D-триггера 22 и счетный вход делителя 12 частоты импульсов подключены к выходам блока 29 преобразователей уровня. Выход первого D-триггера 10 соединен с входом первого ключа 30, а выходы блока 23 коммутатора байтов, выход третьего D-триггера 22 и выход четвертого D-триггера 21 - с входами вторых ключей 31. На информационные входы первого 10, второго 11, четвертого 21 и пятого 19 D-триггеров и на скользящие контакты первого 26 и второго 28 переклю-

20 члтелей подается сигнал логической единицы. Входы блока 29 преобразователей уровня являются первыми входами блока 4 синхронизации, параллельно , соединенные информационные входы

25 блока 23 коммутатора байтов и входы индикатора 32 являются вторыми входа™ ми блока 4 синхронизации. Первым выходом блока 4 синхронизации явлчет- ся выход первого ключа 30, вторыми

30 выходами - выходы вторых ключей 31, третьими выходами блока ч синхрониза- ции являются выходы блока 3 коммутатора управляющих сигналов.

Блок сравнения кодов 24 содержит

35 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 33 по

количеству S разрядов двоичного представления числа, на единицу меньшего, чем количество п измерительных каналов, и элемента И-НЕ 34, количество

40 входов которого равно количеству

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 33. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 33 соединены с соответствующими входами элемента И-НЕ 34„ Одноименные входы

45 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 33 являются соответствующими входами блока 24 сравнения кодов. Выход элемента И-НЕ 34 является выходом блока 24 сравнения кодов.

Блок 13 коммутатора управляющих сигналов выполнен аналогично блоку коммутатора каналов, при этом количество коммутаторов равно количеству S разрядов двоичного представления числа, на единицу меньшего, чем количество п измерительных каналов. Количество информационных входов каям дого коммутатора равно двум, а количество управляющих входов равно одному.

Блок 23 коммутатора байтов содержит восемь коммутаторов 35 со строби- руемыми выходами. Количество информационных входов каждого коммутатора 35 равно количеству m отведенных на перфоленте байт для перфорации информации каждого измерительного канала, а количество управляющих входов равно количеству К разрядов двоичного представления числа, на единицу меньшего, чем количество га отведенных на перфоленте байт для перфорации информации каждого измерительного канала. Информационные входы с одинаковыми номерами являются соответствующими . входами блока 23 коммутатора байтов, управляющие входы с одинаковыми номерами соединены параллельно и являются управляющими входами блока 23 коммутатора байтов, стробирующие входы коммутаторов 35 соединены параллельно и являются стробирующим входом блока 23 коммутатора байтов. Выходы коммутаторов 35 являются выходами блока 23 коммутатора байтов.

Устройство работает следующим образом.

Измеряемый параметр Р преобразуется преобразователем 1 измеряемого параметра в аналоговый сигнал по закону U а-Р + Ь, где а,Ь - коэффициенты преобразования преобразователя 1 измеряемого параметра в аналоговый сигнал. Затем этот аналоговый сигнал преобразуется преобразователем

6аналогового сигнала в частоту импульсов по закону f c-U + d,

где с, d - коэффициенты преобразования преобразователя 6 аналогового сигнала в частоту. Полный закон преобразования измеряемого параметра Р в частоту f импульсов на входе первог го счетчика 7 определяется соотношением f « А-Р + В. Коэффициенты А и В преобразования соответственно равны А а-с; В я b-c + d. Первый счетчик

7считает количество импульсов, поступивших на его вход, и подает информацию в параллельном коде на соответствующие информационные входы блока 3 коммутатора каналов. Информация на выходах первого счетчика 7 является значением интеграла от измеряемого параметра Р по времени, представленным в цифровом виде.

На выход блока 3 коммутатора каналов проходит значение интеграла того измерительного канала 2, код которого подан на управляющие входы блока

3 коммутатора каналов. Значение интеграла индицируется индикатором 32, который служит для визуальной провер ки работоспособности измерительных каналов 2. Блок 4 синхронизации нахоQ дится в одном из трех режимов работы: режим ожидания, режим запуска двигателя перфоратора и режим перфорации, В режиме ожидания на первом и вторых выходах блока 4 синхронизации сигна-

5 лы отсутствуют и перфоратор 5 находится в отключенном состоянии. Сигнал на третьих выходах блока 4 синхронизации изменяется в соответствии с положением второго переключателя

0 28, управляемого вручную. По фронту импульса, поступившего от датчика 9 времени, блок 4 синхронизации переходит работать в режим запуска двигателя перфоратора 5. На первом выходе

5 блока 4 синхронизации появляется сигнал и перфоратор 5 включает двигатель. Датчики положения вала перфоратора 5 вырабатывают импульсы, которые поступают на первые входы блока 4 син-

0 хронизации. Состояние вторых и

третьих выходов блока 4 синхронизации такое же, как и в режиме ожидания. Через интервал времени, необходимый для разворота двигателя перфо- v

5 ратора 5, блок 4 синхронизации переходит работать в режим перфорации. На первом выходе блока 4 синхронизации сохраняется сигнал включения двиг гателя перфоратора 5, а через вторые

о выходы блок 4 синхронизации синхронно с выходными импульсами от датчиков положения вала перфоратора 5 управляет работой электромагнитов перфоратора 5, На третьих выходах блока

5 4 синхронизации автоматически вырабатывается сигнал, который управляет работой блока 3 коммутатора каналов. На выходы блока 3 коммутатора каналов поступает информация с выходов пер-

0 рых счетчиков 7 измерительных каналов 2 последовательно, начиная с первого канала. После перфорации перфоратором 5 информации измерительных каналов 2, количество которых установлено

5 первым переключателем 26, блок 4 синхронизации переходит работать в режим ожидания.

Блок 3 коммутатора каналов осуществляет коммутацию параллельных кодов,

гюдаваемьгх на его информационные вх ДВ1 первыми счетчиками 7 кзмеритель ных каналов 2,

Блок 4 синхронизации работает следующим образомо В режиме ожидания первый D-триггер 10 находится в состоянии логического нуля, первый ключ 30 закрыт. Логическая единица с инверсного выхода первого D-триг- гера 10 подается на входы сброса второго D-триггера 11 и делителя 12 частоты импульсов, работа которых тем самым блокируется. Логическая единица с инверсного выхода второго D- триггера 11, подаваемая на входы сброса второго 17 и третьего 18 счетчиков, на входы сброса пятого 19 и шестого 20 D-триггеров и чгрез первый элемент ИЛИ 15 и второй зле- мент ИЛИ 16 на входы сброса третьего 22 и четвертого 21 D-триггеров соответственно, блокирует работу этих элементов, Логический нуль с выхода третьего D-триггера 22 подается на стробирующий вход блока 23 коммутатора байтов, запрещая прохождение информации с информационных входов блока 23 коммутатора байтов на его выходы. Вторые ключи 31 закрыты. Лог гический нуль с выхода второго D- триггера 11, подаваемый на управляющий вход блока 33 коммутатора управляющих сигналов з разрешает прохождение информации с первых информационных входов блока 3 коммутатора упра лящщих сигналов на его выход„ Таких образом, в режиме ожидания на первом и вторых выходах блока 4 синхронизации сигналы отсутствуют, а инфор- мация на его третьих выходах изменяется в соответствии с изменением положения второго переключателя 28. По фронту импульса, поступившего от датчика 9 времени, первый D-триггер 10 переключается в состояние логической единицы и снимает блокирующий сигнал со входов сброса второго D- триггера 11 и делителя 12 частоты импульсов, разрешая их работу Тем самым блок 4 синхронизации переходит работать в режим запуска двигателя перфоратора 5„ На первом выходе блока 4 синхронизации появляется сигнал двигатель перфоратора 5 включается и на выходах датчиков положения вала перфоратора 5 появляются импульсы, которые после преобразования их уровня поступают на счетный вход делите-

,д рд 25 зо Q 45 --,

35

5

ля 12 частоты импульсов. Через время, необходимое для того, чтобы скорость вращения двигателя перфоратора 5 достигла своего номинального значения, на выходе делителя 12 частоты имлуль- сов появляется импульс, который переключает второй D-триггер 11 в состояние логической единицы, и блок

4синхронизации переходит работать в режим перфорации. Второй D-триггер 11 снимает блокирующий сигнал со входов сброса третьего 22, четвертого 21, пятого 19, шестого 20 D-триггеров, второго 17 и третьего

18 счетчиков и устанавливает логическую единицу на управляющем входе блока S3 коммутатора управляющих сигналов и через элемент И 1& на информационном входе третьего D-тркггера 20. Блок коммутатора управляющих сигналов переключается на прохождение информации со вторых информационных входов на его выходы. Третий D-триг- гер 22 управляет работой электромагнита ЭМ9 синхродорожки перфоратора

5и управляет появлением информации на выходах блока 23 коммутатора байтов Четвертый D-триггер 2 управляет работой транспортного электромагнита ЭМ10 перфоратора 5в Третий В--триггер 22 переключается в состоя- чче логической единицы по фронту импульса от датчика ДП2 положения вала перфоратора 5 и переключается

в состояние логического нуля при поступлении импульса от датчика ДПП положения вала перфоратора 5, а четвертый D-триггер 21 переключается в состояние логической единицы при возврате третьего D-триггера 22 в состояние .логического нуля и пере- клю ается в состояние логического нуля при поступлении импульса от датчика ДПЗ положения вала перфоратора 5, что соответствует цикловой диаграмме работы перфоратора ГШ-80. Второй счетчик 17 считает количество выведенных на перфорацию байт каждого измерительного канала и управляет переключением бпока 23 коммутатора байтов. Третий счетчик 18 считает количество каналов,информация из которых выведена ч& перфоленту, и через блок 13 коммутатора управляющих сигналов управляет переключением блока 3 коммутатора каналов. Логический нуль на выходе блока 24 сравнения ко- . дов появляется в случае равенства

кодов на первых и вторых его входах, а в остальных случаях на выходе блока 24 сравнения кодов поддерживается логическая единица. Во время перфорации информации из измерительного канала 2, номер которого установлен первым переключателем 26, коды на первых и,вторых входах блока 24 сравнения кодов совпадают и на его выхо- Де поддерживается логический нуль. После окончания перфорации информации из этого измерительного канала код на выходах третьего счетчика 18 (изменяется, в результате чего на выходе блока 24 сравнения кодов устанавливается логическая единица и пере-4 ключается в состояние логической единицы пятый D-триггер 19, который устанавливает логическую единицу на информационном входе шестого D-триг- гера 20 и через элемент И 14 устанавливает логический нуль на информационном входе третьего D-триггера 22. При поступлении импульса от датчика ДПЗ положения вала перфоратора 5 четвертый D-триггер 21 переключается в состояние логического нуля, в результате чего заканчивается транспортировка перфоленты после перфорации информации из последнего измерительного канала и в состояние логической единицы переключается шестой D-триг- гер 20, который устанавливает логи ческую единицу на входе сброса первого D-триггера 10. Первый D-триггер 10 переключается в состояние логического нуля и устанавливает логическую единицу на входах сброса второго D-триггера 1 и делителя 12 частоты импульсов и логический нуль на входе первого ключа 30, в результате чего двигатель перфоратора 5 отключается. Второй D-триггер 11 переключается в состояние логического нуля, устанавливает логическую единицу на входах сброса третьего 22, четвертого 21, пятого 19 и шестого 20 D-триггеров, второго 17 и третьего 18 счетчиков, логический нуль на информационном входе третьего D-триггера 22, на управляющем входе блока 13 коммутатора управляющих сигналов и блок 4 синхронизации переходит работать в режим ожидания.

В блоке 24 сравнения кодов осуществляется поразрядное сравнение кодов на первых и вторых входах с помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ

33, При полном совпадении кодов на выходе элемента И-НЕ 34 устанавливается логический нуль, а в остальных -

логическая единица.

Блок 13 коммутатора управляющих сигналов осуществляет коммутацию параллельных кодов, подаваемых на его информационные входы вторым шиф-

ратором 27 и третьим счетчиком 18.

Блок 23 коммутатора байтов осуществляет стробируемую коммутацию байтов информации, поступающей с выхода блока 13 коммутатора управляющих

5 сигналов и с выхода блока 3 коммутатора каналов.

Расчет интегрального значения за дискретные интервалы времени и средних значений за период дискрети-

0 зации по времени производится на цифровой ЭВМ по алгоритму, схема которого представлена на фиг.6.

В блоке I производится ввод в ЭВМ интервала времени At, с которым датчик времени генерирует импульсы, и коэффициентов А и В полного закона преобразования измеренного параметра Р в частоту f импульсов для каждого измерительного канала. В блоке II присваиваются нулевые значения предыдущему номеру измерительного канала N и предыдущему моменту времени t . В блоке III значение текущего номера измерительного канала N, присваивается предыдущему но0

0

5

меру измерительного канала Ni-1

W:(Nj) - текущее значение первого счетчика в измерительном канале с номером N в текущий момент времени t.- - записывается в массив W - массив предыдущих значений первых счетчиков в предыдущий момент времени t : , (максимальная размерность 5 массива W.-,-n), а в массив V; - массив текущих значений интеграла от измеренного параметра Р по време- ни в текущий момент t (максимальная размерность массива V- - п) - записывается нулевое значение. В блоке

IVосуществляется ввод m байт информации с перфоленты в ЭВМ и выде- пение из этой информации битов со значением текущего номера канала

N. и битов с текущим значением первого счетчика в измерительном канале с номером N ; в текущий момент времени t j - W, (N j). В логических блоках

Vи VIII сравниваются значения теку-.

щего номера измерительного канала N- и предыдущего номера измерительного канала N; . Каждый блок имеет дйа выхода выход Да, когда условие N,- ЈN ;., выполняется, и выход Нет, когда условие не выполняется В блоке VI выполняются те же действия, что и в блоке IV, но блок VI имеет дополнительный выход END, через который продолжается выполнение программы, когда информация на перфоленте закончилась В блоке VII определяется текущий момент времени t, и выводятся на

J

-)|текущего t; моментов времени, мае- сива средних значений измеренных параметров PJ и массива значений интеграла от измеренного параметра по времени V :. :-В блоке IX выполняются те же действия, что и в блоке VII, но дополнительно осуществляется присвоение значения текущего момента времени t предыдущему моменту времени tj-, . В блоке X определяется 4W-(Nj) - приращение значения первого счетчика в измерительном канале с номером N ; за интервал времени от t 1 до tj, а затем выполняются те же действия, что и в блоке III. В логическом блоке XI, имеющем два выхода, проверяется выполнение условия dWj(N,) 0. В блоке XII содержимое dW;(Nj) увеличивается на величину модуля М первого счетчика измерительного канала. В блоке XIII вычисляется f ;(N-,) - средняя частота следования -импульсов в измерительном канале с номером N за ин-

тервал времени от t; . до

t.-. По известной СЈедней частоте f,- (N ,-) определяется Р -(N ;) - среднее значение измеренного параметра в измерительном канале с номером N , за-интервал времени от tj.t до tj, которое за- писываетсд в массив PJ - массив средних значений измеренных параметров за интервал времени от t ;-, до t : (максимальная размерность массива Р 1- п). В этом же блоке вычисляется значение Vj(Nj) - значение интеграла от измеренного параметра по времени в измерительном канале с номером

текущий момент времени t., кот

J

N j в

торое записывается в массив V:у Выполнение программы начинается с блока 1 и заканчивается в блоке STOP. В результате работы программы на печать выводится список начальных

а:

10

15

20

25

30

35

е

40

45

50

55

и конечных значений временных интервалов и средние за эти временные интервалы значения измеренных параметров, а также значения интеграла от измеренного параметра по времени за период от начала измерения до текущего момента времени для каждого измерительного канала.

Формула изобретения

2,Устройство по п.1, отличающееся тем, что блок коммутатора каналов содержит коммутаторы по количеству выходов первого счетчика, количество информационных входов каждого коммутатора равно ко личеству измерительных каналов, а количество управляющих входов равно количеству разрядов двоичного представления числа на единицу мень-

15

шбго, чем количество измерительных каналов, причем информационные входы с одинаковыми номерами являются соответствующими входами блока коммутатора каналов, управляющие входы с одинаковыми номерами соединены па- р ллельно и являются управляющими входами блока коммутатора каналов,

а выходы коммутаторов являются выходами блока коммутатора каналов.

20 тельных каналов, выходы первого шифратора соединены с вторыми входами блока сравнения кодов, выход которого подключен к тактовому входу пятого Dтриггера, а выходы второго шифрас тактовым входом второго D-триггера, 5 тора соединены с первыми информационвыход которого подключен к параллель-t

ни соединенным управляющему входу

бЛока коммутатора управляющих сигнал рв и второму входу элемента И, ин

вареный выход второго D-триггера сое-3() вхсды элементов ЙЛЙ и параллельно

с первыми входами первого и соединенные тактовый вход третьего

второго элементов ИЛИ и с входами

сброса второго и третьего счетчиков

с инверсным динамическим управлением

и пятого и шестого D-триггеров с пря- выход первого D-триггера соединен

мым динамическим управлением, причем с нходом первого ключа, а выходы

второй счетчик имеет модуль, равный

ными входами блока коммутатора управляющих сигналов, выходы которого подключены к информационным входам блока коммутатора байтов, вторые

U-триггера и счетный вход делителя частоты импульсов подключены к выходам блока преобразователей уровня,

блока коммутатора байтов и выходы третьего и четвертого D-триггеров - с входами вторых ключей, причем

количеству отведенных на перфоленте байт для перфорации информации каждого измерительного канала, а третий счетчик имеет модуль, равный коли- чфстзу измерительных каналов, выход пятого D-триггера соединен с инфор мационным входом шестого D-триггераs выход которого соединен с входом сброса первого D-триггера, тактовый в1сод шестого О -триггера соединен с выходом второго элемента ИЛИ и с

45 ся вторыми входами блока синхрони ции, а первым выходом блока синхр зации является выход первого ключ вторыми выходами - выходы вторых чей, третьими выходами блока син хронизации являются выходы блока

„50

вкодом сброса четвертого D-триггера с прямым динамическим управлением, инверсный выход пятого D-триггера под ключей к первому входу элемента И, выход которого соединен с информационным входом третьего D-триггера с прямым динамическим управлением,

выход первого элемента ИЛИ подключен 55 разрядов двоичного представления к входу сброса третьего D-триггера, числа, на единицу меньшего, чем инверсный выход которого соединен с тактовым входом четвертого D-тригкоммутатора управляющих сигналов

4,Устройство по пп,1 и 3, о т личающееся тем, что бл сравнения кодов содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ по количеству

количество измерительных каналов элемента И-НЕ, количество входов

16

гера, выход третьего D-триггера соединен со счетным входом второго счетчика и со стробирующим входом блока коммутатора байтов, управляющие входы которого соединены с выходами второго счетчика, причем выход старшего разряда второго счетчика подключен также к счетному входу

третьего счетчика, выходы которого подключены к первым входам блока сравнения кодов и к вторым информационным входам блока коммутатора а управляющих сигналов, входы первого

и второго шифраторов соединены с не подвижными контактами соответственно первого и второго переключателей, причем количество входов каждого шифратора равно количеству измерительных каналов, выходы первого шифратора соединены с вторыми входами блока сравнения кодов, выход которого подключен к тактовому входу пятого Dтриггера, а выходы второго шифратора соединены с первыми информационвхсды элементов ЙЛЙ и параллельно

ными входами блока коммутатора управляющих сигналов, выходы которого подключены к информационным входам блока коммутатора байтов, вторые

выход первого D-триггера соединен

U-триггера и счетный вход делителя частоты импульсов подключены к выходам блока преобразователей уровня,

блока коммутатора байтов и выходы третьего и четвертого D-триггеров - с входами вторых ключей, причем

дд входы блока преобразователей уровня являются первыми входами блока синхронизации, параллельно соединенные информационные входы блока коммутатора байтов и входы индикаторе являют-

45 ся вторыми входами блока синхронизации, а первым выходом блока синхронизации является выход первого ключа, вторыми выходами - выходы вторых ключей, третьими выходами блока синхронизации являются выходы блока

50

55 разрядов двоичного представления числа, на единицу меньшего, чем

коммутатора управляющих сигналов.

4,Устройство по пп,1 и 3, о т - личающееся тем, что блок сравнения кодов содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ по количеству

разрядов двоичного представления числа, на единицу меньшего, чем

количество измерительных каналов, и элемента И-НЕ, количество входов ко

торого равно количеству элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ соединены с соответствующими входами элемента И-НЕ, причем одноименные входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ являются соответствующими входами блока сравнения кодов, а выход элемента И-НЕ - выходом блока сравнения кодов,

5,Устройство по пп.1 и 3, о т - личающееся тем, что блок коммутатора управляющих сигналов выполнен аналогично блоку коммутатора каналов, при этом количество коммутаторов равно количеству разрядов двоичного представления числа, на единицу меньшего, чем количество измерительных каналов, количество информационных входов каждого коммутатора равно двум, а количество управляющих входов равно одному,

6,Устройство по пп.1 и 3, о т л и чающееся тем, что блок коммутатора байтов содержит восемь ком-

А

9

0

5

5

0

мутаторов со стробируемыми выходами, количество информационных входов каждого коммутатора равно количеству отведенных на перфоленте байт для перфорации информации каждого измерительного канала, а количество управляющих входов равно количеству , разрядов двоичного представления числа, на единицу меньшего, чем коли- чество отведенных на перфоленте байт для перфорации информации каждого измерительного канала, причем информационные входы с одинаковыми номерами являются соответствующими входами-блока коммутатора байтов, управляющие входы с одинаковыми номерами соединены параллельно и являются управляющими входами блока коммутатора байтов, стт обирующие входы коммутаторов соединены параллельно и являются стробирующим входом блока коммутатора байтов, а выходы коммутаторов являются выходами блока коммутатора байтов.

Фиг. 2

ФигЬ

35

m

Упр)

УпрХ LfftyoS

8

5%

I topi

УпрК

Фие.5

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматический многоканальный регистратор электрических нагрузок.- Промышленная энергетика, 1979, № 2, с.33-35. | |||

Авторы

Даты

1990-06-15—Публикация

1987-06-02—Подача