Изобретение относится к импульсной технике и может быть использовано в составе различных устройств, работающих в условиях воздействия электромагнитных помех и разрядов статического электричества.

Цель изобретения повышение помехоустойчивости устройства по шине сброса и расширение его функциональных возможностей путем обеспечения возможности предварительной параллельной записи информации в устройство.

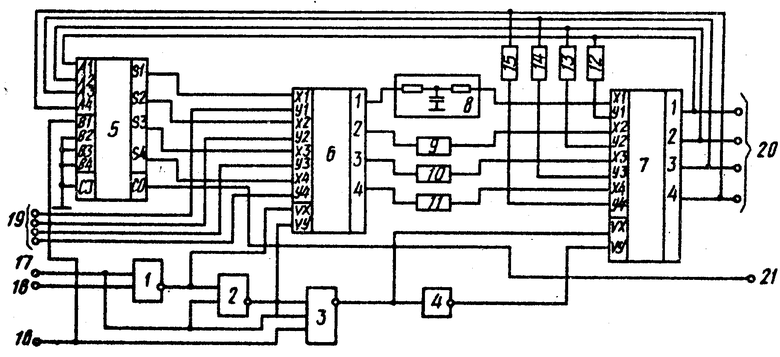

На чертеже приведена принципиальная схема предлагаемого устройства.

Устройство содержит элементы ИЛИ-НЕ 1-3, инвертор 4, четырехразрядный комбинационный сумматор 5, двухканальные четырехразрядные мультиплексоры 6,7 и элементы 8-15 задержки, выполненные в виде RC-цепей. Первый вход элемента ИЛИ-НЕ 2 соединен с выходом элемента ИЛИ-НЕ 1 и с первым управляющим входом мультиплексора 6, первый вход элемента ИЛИ-НЕ 3 соединен с входной шиной 16 и входом младшего разряда первого слагаемого комбинационного сумматора 5, входы остальных разрядов первого слагаемого которого соединены с общей шиной. Вторые входы элементов ИЛИ-НЕ 2 и 3 объединены и соединены с шиной 17 сброса и первым входом элемента ИЛИ-НЕ 1, второй вход которого соединен с шиной 18 команды записи. Третий вход элемента ИЛИ-НЕ 3 соединен с выходом элемента ИЛИ-НЕ 2 и вторым управляющим входом мультиплексора 6. Выход элемента ИЛИ-НЕ 3 соединен с первым управляющим входом мультиплексора 7 и с входом инвертора 4. Выход инвертора 4 соединен с вторым управляющим входом мультиплексора 7. Входы разрядов первого канала мультиплексора 6 соединены с соответствующими выходами разрядов комбинационного сумматора 5, входы разрядов второго канала с соответствующими кодовыми шинами 19, а выходы с входами элементов 8-11 задержки. Входы разрядов первого канала мультиплексора 7 соединены с выходами соответствующих элементов задержки 8-11, входы разрядов второго канала с выходами соответствующих элементов 12-15 задержки, а выходы разрядов с входами соответствующих элементов 12-15 задержки, с соответствующими выходными шинами 20 и входами разрядов второго слагаемого комбинационного сумматора 5, выход переноса которого соединен с выходной шиной 21.

Постоянная времени RC-цепей элементов 8-15 задержки устройства одинаковая и выбирается исходя из требуемого уровня помехозащиты устройства. Резисторы на выходах RC-цепей элементов задержки не являются обязательными элементами схемы и нужны лишь в частных случаях, например для защиты отдельных серий микросхем от так называемого тиристорного эффекта при больших значениях емкостей на входах этих микросхем.

Построение предлагаемого устройства с количеством разрядов более четырех, т. е. большим, чем показано на чертеже, осуществляется путем простого увеличения разрядов комбинационного сумматора 5, мультиплексоров 6,7 и количества элементов задержки.

Устройство работает следующим образом.

После включения питания устройства при отсутствии управляющих сигналов, т. е. когда на шинах входной 16, сброса 17 и команды записи 18 присутствуют уровни логического "0", конденсаторы элементов 8-15 задержки разряжены, на всех разрядных входах первого слагаемого комбинационного сумматора 5 уровни логического "0", на выходах элементов ИЛИ-НЕ 1,3 и на первых управляющих входах мультиплексоров 6,7 уровни логической "1", на выходах элемента ИЛИ-НЕ 2, инвертора 4 и вторых управляющих входах мультиплексоров 6,7 уровни логического "0". При такой комбинации сигналов на управляющих входах мультиплексоров 6,7 на их разрядные выходы поступает информация с соответствующих разрядных входов первого канала (в мультиплексорах 6,7 активно формируются уровни выходных сигналов "0" или "1", повторяющие логические уровни сигналов на входах, в данном случае первого канала). Таким образом, на разрядных выходах мультиплексора 7 присутствуют уровни логического "0", так как конденсаторы элементов 8-11 задержки разряжены. Уровни логического "0" на разрядных выходах мультиплексора 7 поддерживают в разряженном состоянии конденсаторы элементов 12-15 задержки и поступают на выходные шины 20,

на разрядные входы второго слагаемого комбинационного сумматора 5, а поскольку на входах первого слагаемого последнего при этом уровни логического "0", то на его разрядных выходах, а значит и на разрядных выходах мультиплексора 6 будут уровни логического "0", чем поддерживается разряженное состояние конденсаторов элементов 8-11 задержки. Такое состояние устройства, когда конденсаторы всех элементов 8-15 задержки разряжены, а на разрядных выходах комбинационного сумматора 5 и мультиплексоров 6,7 уровни логического "0", является исходным и сохраняется до появления импульса на шине 18 команды записи или на входной шине 16 (появление импульса на шине 17 приводит только к изменению уровней сигналов на выходах элементов ИЛИ-НЕ 1,3 и инвертора 4).

Необходимо отметить, что устройство при включении питания при разряженных конденсаторах элементов 8-11 задержки само устанавливается в исходное состояние и не нуждается в начальном сбросе.

Предварительная установка устройства, т. е. запись в него необходимой информации, производится подачей импульсного сигнала с уровнем логической "1" на шину 18 команды записи, при этом на кодовые шины 19 должен подаваться код числа, вводимого в устройство, который может быть соответствующей комбинацией как статических, так и импульсных сигналов. При этом длительность импульсных сигналов на кодовых шинах 19 должна быть такой, чтобы к моменту поступления среза импульса команды записи на конденсаторах элементов 8-11 задержки успел записаться код вводимой информации. Допустим, что на кодовые шины 19 подан двоичный код числа 5 (0101) (младший разряд кода здесь и далее в тексте справа). В течение длительности импульса команды записи на выходах элементов ИЛИ-НЕ 1,3 и на первых управляющих входах мультиплексоров 6,7 уровни логического "0", на выходах элемента ИЛИ-НЕ 2, инвертора 4 и на вторых управляющих входах мультиплексоров 6,7 уровни логической "1". При такой комбинации сигналов на управляющих входах мультиплексоров 6,7 на их разрядные выходы поступает информация с соответствующих разрядных входов второго канала,

т. е. с кодовых шин 19 у мультиплексора 6 и с конденсаторов элементов 12-15 задержки у мультиплексора 7. Так как на кодовые шины 19 подан код 0101,

на выходах первого и третьего разрядов мультиплексора 6 уровень логической "1", поэтому конденсаторы элементов 8 и 10 задержки заряжаются (предполагается, что до поступления импульса команды записи устройство находится в исходном состоянии, хотя оно может находиться в любом из 16 возможных состояний), а конденсаторы элементов задержки 9 и 11 поддерживаются в разряженном состоянии уровнем логического "0" на выходах второго и четвертого разрядов мультиплексора 6. Постоянная времени RC-цепей элементов 8-11 задержки выбирается таким образом, чтобы конденсатор до среза любого входного импульса успел зарядиться до уровня логической "1" или разрядиться до уровня логического "0". Поскольку к моменту прихода импульса команды записи устройство находится в исходном состоянии, то конденсаторы элементов 12-15 задержки разряжены, поэтому на разрядных выходах мультиплексора 7 уровни логического "0", соответствующие предыдущему состоянию устройства. Уровни логического "0" на выходах мультиплексора 7 поддерживают в разряженном состоянии конденсаторы элементов 12-15 задержки и поступают на разрядные входы второго слагаемого комбинационного сумматора 5,

на всех разрядных входах первого слагаемого которого также уровни логического "0", поэтому на выходах комбинационного сумматора 5 уровни логического "0". Описанное состояние устройства сохраняется до снятия импульса команды записи. Таким образом, к концу импульса команды записи код нового состояния (0101), соответствующий записываемой в устройство информации, запоминается на конденсаторах элементов 8-11 задержки, а конденсаторы элементов 12-15 задержки в это время хранят код предыдущего состояния (0000).

После окончания импульса команды записи на выходах элементов ИЛИ-НЕ 1,3 и на первых управляющих входах мультиплексоров 6,7 уровни логической "1", на выходах элемента ИЛИ-НЕ 2, инвертора 4 и вторых управляющих входах мультиплексоров 6,7 уровни логического "0", что соответствует, как было указано выше, поступлению на разрядные выходы мультиплексора 6 информации с соответствующих разрядных выходов комбинационного сумматора 5, а на разрядные выходы мультиплексора 7 с конденсаторов соответствующих элементов 8-11 задержки. Поэтому на разрядных выходах мультиплексора 7 появляется код числа 5 (0101), начинается заряд конденсаторов элементов 12, 14,

а на конденсаторах элементов 13-15 задержки поддерживается уровень логического "0", т.е. начинается запись кода нового состояния, соответствующего записанной в устройство информации, в элементы 12-15 задержки. Одновременно на разрядных входах второго слагаемого комбинационного сумматора 5 появляется код числа 5 (0101), на разрядных входах первого слагаемого которого уровни логического "0", поэтому на разрядных выходах комбинационного сумматора 5 и на разрядных выходах мультиплексора 6 появляется код числа 5 (0101) и в конденсаторах элементов 8-11 задержки поддерживается этот же код, записанный в них в течение длительности импульса команды записи.

Таким образом, после окончания импульса команды записи устройство переключается в состояние, соответствующее информации, присутствовавшей на кодовых шинах 19 в течение длительности импульса команды записи, при этом конденсаторы элементов 8-11 задержки хранят код нового состояния, а конденсаторы элементов 12-15 задержки записывают код нового состояния. После окончания процессов перезаряда конденсаторов элементов 12-15 задержки состояние устройства не изменяется до появления импульса на одной из управляющих шин.

В исходное состояние устройство приводится подачей импульсного сигнала с уровнем логической "1" по шине 17 сброса. В течение длительности импульса сброса на выходах элементов ИЛИ-НЕ 1.3, на первом и втором управляющих входах мультиплексора 6 и на первом управляющем входе мультиплексора 7 уровень логического "0", на выходе инвертора 4 и на втором управляющем входе мультиплексора 7 уровень логической "1". При указанной комбинации сигналов на управляющих входах мультиплексора 7 на его разрядные выходы поступает информация с конденсаторов элементов 12-15 задержки, хранящих информацию о предыдущем состоянии устройства,

и поддерживает их соответствующее заряженное или разряженное состояние. При наличии уровня логического "0" на обоих управляющих входах мультиплексора 6 на его разрядных выходах независимо от уровней сигналов на разрядных входах обоих каналов, т.е. независимо от уровней сигналов на разрядных выходах комбинационного сумматора 5 и кодовых шинах 19, присутствует уровень логического "0". Поэтому конденсаторы элементов 8-11 задержки начинают разряжаться (если до этого были заряжены) через малые выходные сопротивления разрядных выходов мультиплексора 6.

Таким образом, к концу импульса сброса код нового исходного нулевого состояния запоминается на конденсаторах элементов 8-11 задержки, а конденсаторы элементов 12-15 задержки в это же время хранят код предыдущего состояния устройства.

После окончания импульса сброса на выходах элементов ИЛИ-НЕ 1, 3 и на первых управляющих входах мультиплексоров 6, 7 уровни логической "1", на выходах элементов ИЛИ-НЕ 2, инвертора 4 и на вторых управляющих входах мультиплексоров 6, 7 уровни логического "0". При этом, как указывалось выше, на разрядные выходы мультиплексора 6 поступает информация с соответствующих разрядных выходов комбинационного сумматора 5, а на разрядные выходы мультиплексора 7 с разряженных конденсаторов соответствующих элементов 8-11 задержки. Поэтому на разрядных выходах мультиплексора 7 появляются уровни логического "0", начинается разряд конденсаторов (если они до этого были заряжены) элементов 12-15 задержки, т.е. начинается запись кода нового (исходного нулевого) состояния в элементы 12-15 задержки. Одновременно на разрядных входах второго слагаемого комбинационного сумматора 5 появляются уровни логического "0", на разрядных входах первого слагаемого комбинационного сумматора 5 уровни логического "0" сохраняются,

поэтому на разрядных выходах комбинационного сумматора 5 и мультиплексора 6 появляются уровни логического "0", следовательно будет поддерживаться разряженное состояние конденсаторов элементов 8-11 задержки.

Таким образом, после окончания импульса сброса устройство переключается в исходное нулевое состояние, при этом, как и после окончания импульса команды записи, конденсаторы, элементов 8-11 задержки хранят код нового состояния устройства, а конденсаторы элементов 12-15 задержки записывают этот код, а после окончания процесса перезаряда конденсаторов элементов 12-15 задержки состояние устройства не изменяется до появления импульса на одной из управляющих шин.

Рассмотрим работу устройства в режиме счета. Счетные импульсы подаются на входную шину 16 в виде импульсного сигнала с уровнем логической "1". Допустим, что до поступления первого счетного импульса устройство находится в исходном нулевом состоянии, т.е. конденсаторы элементов 8-15 задержки разряжены и поддерживаются в этом состоянии. При поступлении первого счетного импульса на выходе элемента ИЛИ-НЕ 1 и на первом управляющем входе мультиплексора 6 уровень логической "1", на выходе элемента ИЛИ-НЕ 2 и на втором управляющем входе мультиплексора 6 уровень логического "0", на первом управляющем входе мультиплексора 7 и на выходе элемента ИЛИ-НЕ 3 уровень логического "0", на втором управляющем входе мультиплексора 7 и на выходе инвертора 4

уровень логической "1". При такой комбинации сигналов на управляющих входах мультиплексоров 6, 7 на разрядные выходы мультиплексора 6 поступает информация с соответствующих разрядных выходов комбинационного сумматора 5, а на разрядные выходы мультиплексора 7 с конденсаторов соответствующих элементов 12-15 задержки, хранящих информацию о предыдущем (исходном нулевом) состоянии устройства, и поддерживает их разряженное состояние.

Уровни логического "0", т. е. код числа 0 (0000) с разрядных выходов мультиплексора 7 поступает на соответствующие разрядные входы второго слагаемого комбинационного сумматора 5, на разрядные входы первого слагаемого которого поступает двоичный код числа 1 (0001), так как на вход младшего разряда первого слагаемого подается счетный импульс, а входы остальных разрядов первого слагаемого соединены с общей шиной, имеющей уровень логического "0". Поэтому на разрядных выходах комбинационного сумматора 5, следовательно, и на разрядных выходах мультиплексора 6 присутствует код числа 1 (0001), что обеспечивается выше указанной комбинацией сигналов на управляющих входах мультиплексора 6.

Следовательно, поддерживается разряженное состояние конденсаторов элементов 9-11 задержки и заряжается конденсатор элемента 8 задержки. Таким образом, к концу первого счетного импульса код нового состояния устройства, соответствующий коду числа 1 (0001), запоминается на конденсаторах элементов 8-11 задержки, а конденсаторы элементов 12.15 задержки в это время хранят код предыдущего (исходного) состояния устройства (0000).

После окончания первого счетного импульса на выходах элементов ИЛИ-НЕ 1, 3 и на первых управляющих входах мультиплексоров 6, 7 уровни логической "1", на выходах элемента ИЛИ-НЕ 2, инвертора 4 и вторых управляющих входах мультиплексоров 6,7 уровни логического "0". При такой комбинации сигналов на управляющих входах мультиплексоров 6, 7 на их разрядные выходы поступает информация с соответствующих разрядных входов первого канала,

т.е. с разрядных выходов комбинационного сумматора 5 у мультиплексора 6, с конденсаторов элементов 8-11 задержки у мультиплексора 7. Поэтому на разрядных выходах мультиплексора 7 появится код числа 1 (0001), записанный в течение счетного импульса на конденсаторах элементов 8-1 задержки. Этот код поступает на входы второго слагаемого комбинационного сумматора 5, а так как на всех входах первого слагаемого последнего в это время уровни логического "0", то на его разрядных выходах, а значит и на разрядных выходах мультиплексора 6 будет тот же код числа 1 (0001), который поддерживает запомненный после первого счетного импульса на конденсаторах элементов 8-11 задержки код числа 1 (0001).

При появлении кода числа 1 (0001) на разрядных выходах мультиплексора 7 после первого счетного импульса начинается заряд конденсатора элемента 12 задержки, подключенного к выходу младшего разряда мультиплексора 7. Постоянная временная RC-цепей элементов 12-15 задержки выбирается таким образом, чтобы между счетными импульсами конденсаторы последних успели перезарядиться. Таким образом, после окончания первого счетного импульса устройство переключается в состояние,

соответствующее двоичному коду числа 1 0001, при этом, как и после окончания команды записи или импульса сброса, конденсаторы элементов 8-11 хранят код нового состояния (в рассматриваемом случае это код числа 1) устройства, а конденсаторы элементов 12-15 записывают этот код, после окончания заряда конденсатора элемента 12 код нового состояния записывается на конденсаторах элементов 8-11 и 12-15.

При поступлении очередного счетного импульса (в данном случае второго) устройство работает аналогично: в течение длительности счетного импульса код числа 1 (0001), соответствующий состоянию устройства после первого счетного импульса, хранится на конденсаторах элементов 12-15 и через мультиплексор 7 подается на входы второго слагаемого комбинационного сумматора 5, на входы первого слагаемого подается код счетного импульса код числа 1 (0001). В результате на разрядных выходах комбинационного сумматора 5 и мультиплексора 6 в течение второго счетного импульса присутствует код числа 2 (0010), при этом разряжается конденсатор элемента 8 и заряжается конденсатор элемента 9, т. е. конденсаторы элементов задержки 8-11 записывают код нового состояния устройства код числа 2 (0010). После окончания второго счетного импульса код числа 2 (0010), запомненный на конденсаторах элементов 8-11,

через мультиплексор 7, комбинационный сумматор 5 и мультиплексор 6 поддерживает сам себя и одновременно через мультиплексор 7 записывается на конденсаторы элементов 12-15 (разряжается конденсатор элемента 12 и заряжается конденсатор элемента 13). После окончания процессов разряда и заряда конденсаторов 12 и 13 элементов соответственно код нового состояния устройства (двоичный код числа 2 0010) хранится на конденсаторах всех элементов 8-11 и 12-15,

устройство сохраняет свое состояние до поступления следующего (третьего) счетного импульса.

При поступлении третьего и последующих счетных импульсов устройство работает аналогично и последовательно принимает свои состояния до кода числа 15 (1111). При поступлении шестнадцатого счетного импульса на выходе переноса комбинационного сумматора 5 появляется сигнал с уровнем логической "1" с длительностью, равной длительности счетного импульса, который выдается на выходную шину 21 как импульс переполнения устройства. После окончания шестнадцатого счетного импульса конденсаторы всех элементов 8-11 и 12-15 оказываются разряженными, т. е. устройство возвращается в исходное нулевое состояние.

При поступлении счетных импульсов после предварительной установки устройства оно работает аналогично, но принимает последовательно состояния от предварительно установленного до состояния, соответствующего числу 15 (1111), а затем выдает импульс переполнения и возвращается в исходное нулевое состояние.

Таким образом, устройство изменяет свое состояние по срезу импульса на любом из управляющих входов (входной шине 16, шине 17 сброса, шине 18 команды записи) и только в том случае, если длительность импульса окажется больше некоторого заданного разработчиком значения и будет достаточной для записи кода нового состояния на конденсаторы элементов 8-11, т.е. для их перезаряда от уровня логического "0" до уровня логической "1" или наоборот. В противном случае по срезу импульса устройство не изменяет свое текущее состояние. Поскольку промежуточные состояния устройства хранятся на конденсаторах элементов задержки, т.е. пассивных и инерционных элементах памяти, а устройство содержит только элементы комбинационной логики, т.е. не имеет в своем составе активных бистабильных функциональных элементов, оно устойчиво и к внутренним помехам, в том числе к помехам в шине питания.

При наличии импульса на шине 17 сброса устройство не реагирует на импульсы по шинам 18 и 16, т.е. шина 17 обладает приоритетом перед шинами 18 и 16.

При наличии импульса на шине 18 устройство не реагирует на импульсы по входной шине 16, т.е. шина 18 обладает приоритетом перед входной шиной 16.

Предлагаемое устройство может работать и в составе многоразрядных счетных устройств с предварительной установкой, для чего достаточно выходную шину 21 первого устройства соединить с входной шиной 16 второго устройства и т.д. а шины 17 и 18 всех устройств объединить.

Повышение помехоустойчивости по шине сброса достигается тем, что обеспечивается переключение устройства по срезу (а не по фронту, как в известном устройстве) импульса на шине сброса и только в том случае, если длительность импульса превышает некоторое пороговое значение, заданное разработчиком, т. е. если импульс не является помехой.

Расширение функциональных возможностей достигается тем, что обеспечивается возможность предварительной параллельной записи информации в устройство, что позволяет расширить области его применения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 1991 |

|

SU1817645A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1574146A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1987 |

|

SU1464893A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1989 |

|

SU1785407A2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1991 |

|

SU1826835A1 |

Изобретение относится к импульсной технике и может быть использовано в составе различных цифровых устройств, работающих в условиях воздействия электромагнитных помех и разрядов статического электричества. Цель изобретения повышение помехоустойчивости по шине сброса и расширение функциональных возможностей достигается путем обеспечения предварительной параллельной записи информации в устройство. Устройство содержит элементы ИЛИ-НЕ 1 3, инвертор 4, комбинационный сумматор 5, двухканальные цифровые мультиплексоры 6,7, элементы 8 15 задержки, выполненные в виде RC-цепей, входную шину 16, шину 17 сброса, шину 18 команды записи, кодовые шины 19, выходные шины 20, 21. Введение второго двухканального цифрового мультиплексора, третьего элемента ИЛИ-НЕ, инвертора и образование новых связей между элементами устройства позволяют производить сброс в исходное нулевое состояние по срезу импульса сброса только после анализа его длительности и осуществить параллельную запись произвольной информации. 1 ил.

УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ, содержащее входную и выходную шины, шину сброса, h разрядный комбинационный сумматор, первые и вторые РС-элементы задержки, первый и второй элементы ИЛИ НЕ и первый двухканальный h - разрядный мультиплексор, первый вход первого элемента ИЛИ НЕ соединен с шиной сброса, выход с первым входом второго элемента ИЛИ НЕ, второй вход которого соединен с шиной сброса, входы разрядов, кроме младшего, первого слагаемого h разрядного комбинационного сумматора соединены с общей шиной, входы разрядов второго слагаемого с выходами соответствующих разрядов первого двухканального h разрядного мультиплексора, входы первого канала которого подключены к выходам первых RC элементов задержки, а разрядные выходы через вторые RC элементы задержки соединены с соответствующими входами его второго канала, выход переноса h разрядного комбинационного сумматора соединен с выходной шиной, отличающееся тем, что, с целью повышения помехоустойчивости по шине сброса и расширения функциональных возможностей путем обеспечения возможности предварительной параллельной записи информации в устройство, в него введены шина команды записи, кодовые шины, третий элемент ИЛИ НЕ, инвертор и второй двухканальный n разрядный мультиплексор, первый вход третьего элемента ИЛИ НЕ соединен с входной шиной и входом младшего разряда первого слагаемого n разрядного комбинационного сумматора, второй вход с шиной сброса, третий вход с входом второго элемента ИЛИ НЕ, выход с входом инвертора и с первым управляющим входом первого двухканального n - разрядного мультиплексора, второй управляющий вход которого подключен к выходу инвертора, выходы разрядов второго двухканального n разрядного мультиплексора соединены с входами первых RC элементов задержки, входы первого канала с соответствующими выходами разрядов n разрядного комбинационного сумматора, входы, второго канала с соответствующими кодовыми шинами, второй управляющий вход с выходом второго элемента ИЛИ НЕ, первый управляющий вход с выходом первого элемента ИЛИ НЕ, второй вход которого соединен с шиной команды записи.

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1987 |

|

SU1464893A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-09-10—Публикация

1988-10-04—Подача