Изобретение относится к импульсной технике и может быть использовано в составе различных цифровых устройств, работающих в условиях воздействия помех.

Целью изобретения является повышение надежности устройства путем его упрощения.

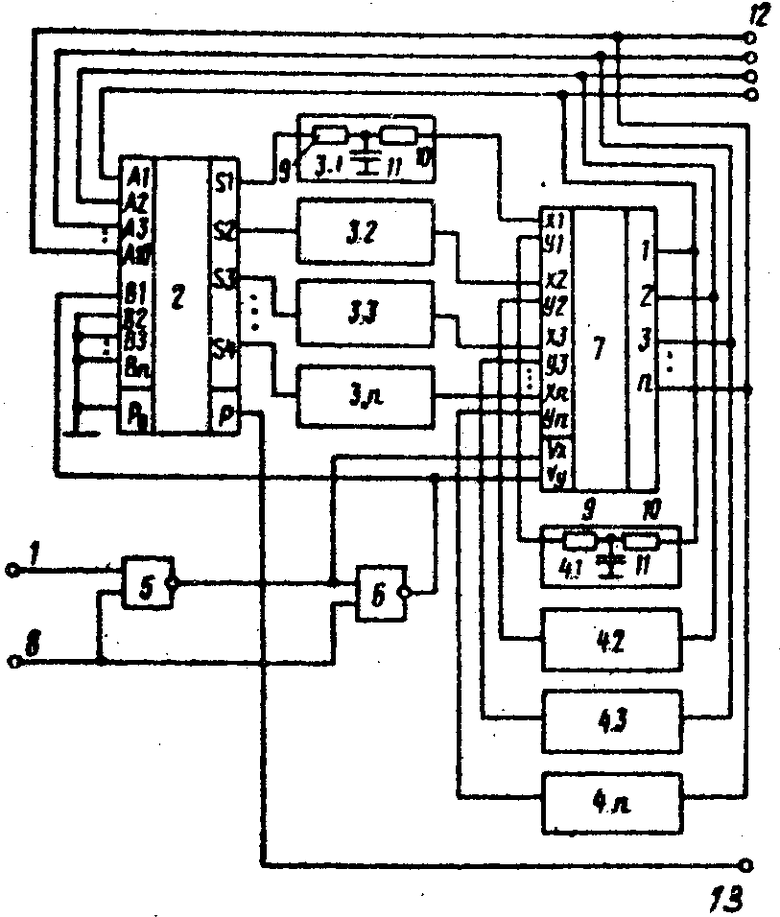

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство для счета импульсов содержит входную шину 1, n-разрядный комбинационный сумматор 2, m первых 3 и n вторых 4 RC-элементов задержки, первый 5 и второй 6 элементы ИЛИ-НЕ и двухканальный n-разрядный мультиплексор 7. Первый вход первого элемента ИЛИ-НЕ соединен с входной шиной 1, второй вход - с шиной сброса 8 и с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и с первым управляющим входом двухканального n-разрядного мультиплексора 7, второй управляющий вход которого соединен с выходом второго элемента ИЛИ-НЕ и с входом младшего разряда первого слагаемого n-разрядного комбинационного сумматора 2, входы остальных разрядов первого слагаемого n-разрядного комбинационного сумматора соединены с общей шиной, входы разрядов второго слагаемого - с выходами соответствующих разрядов двухканального n-разрядного мультиплексора, выходы разрядов n-разрядного комбинационного сумматора через соответствующие первые RC-элементы 3 задержки подключены к соответствующим входам первого канала двухканального n-разрядного мультиплексора 7, выходы разрядов которого через соответствующие вторые RC-элементы 4 задержки соединены с соответствующими входами второго канала двухканального n-разрядного мультиплексора 7. Каждый элемент задержки имеет в своем составе первый 9 и второй 10 резисторы и конденсатор 11, первый вывод которого подключен к общей шине, а второй соединен с первыми выводами первого и второго резисторов, вторые выводы которых соединены соответственно с входом и выходом RC-элемента задержки. Устройство также имеет выходы 12 разрядов и выход 13 переноса.

Постоянная времени всех RC-элементов задержки устройства одинаковая и выбирается исходя из требуемого уровня помехозащиты устройства. Резисторы 10 на выходах RC-цепей элементов задержки не являются обязательными элементами схемы: они нужны лишь в частных случаях, например для защиты отдельных серий микросхем с комплементарной МДП-структурой от так называемого "тиристорного эффекта" при больших значениях емкостей на входах этих микросхем.

Устройство работает следующим образом. Перед работой устройство устанавливается в исходное нулевое состояние подачей импульсного сигнала с уровнем логической единицы по шине 8 сброса. В течение длительности импульса сброса на выходах элементов ИЛИ-НЕ 5 и 6 и, следовательно, на первом и втором управляющих входах мультиплексора 7 будет поддерживаться уровень логического нуля. При наличии уровня логического нуля на обоих управляющих входах мультиплексора 7 на его выходах (независимо от уровней сигналов на его разрядных входах) будет присутствовать уровень логического нуля. Поэтому конденсаторы RC-цепей вторых RC-элементов 4 задержки начинают разряжаться (если до этого были заряжены) через малые выходные сопротивления выходов разрядного мультиплексора 7. Одновременно уровни логического нуля с выходов мультиплексора 7 поступают на разрядные входы второго слагаемого комбинационного сумматора 2. Поскольку при этом на всех разрядных входах первого слагаемого комбинационного сумматора 1 присутствует уровень логического нуля, то на его выходах в течение импульса сброса также будет поддерживаться уровень логического нуля, следовательно, конденсаторы первых RC-элементов 3 задержки также начинают разряжаться (если до этого были заряжены) через малые выходные сопротивления выходов комбинационного сумматора 2. Длительность импульса сброса выбирается такой, что в течение длительности этого импульса конденсаторы 11 вторых элементов 3 задержки полностью разряжаются (до уровня остаточного напряжения логического нуля на выходах комбинационного сумматора 2).

По окончании импульса сброса на выходе первого элемента ИЛИ-НЕ 5 восстанавливается уровень логической единицы. Следовательно, на первом управляющем входе мультиплексора 7 будет уровень логической единицы, на втором - логического нуля. При такой комбинации сигналов на управляющих входах мультиплексора 7 на его разрядные входы передаются сигналы, имеющиеся на входах первого канала его разрядов, т.е. уровни сигналов с конденсаторов 11 RC-цепей первых RC-элементов 3 задержки. А поскольку в течение импульса сброса эти конденсаторы разрядились, то на выходах мультиплексора 7 уровни логического нуля сохранятся. Следовательно, на разрядных выходах комбинационного сумматора 2 также сохранятся уровни логического нуля, поскольку на всех входах первого и второго слагаемых комбинационного сумматора 2 в это время - уровень логического нуля, конденсаторы 11 RC-цепей первых RC-элементов задержки остаются разряженными. Таким образом, после импульса сброса конденсаторы 11 RC-цепей всех элементов задержки разряжены, а на всех выходах комбинационного сумматора 2 и мультиплексора 7 присутствует уровень логического нуля. Такое состояние устройства сохраняется до подачи счетного импульса по входной шине 1.

Необходимо отметить, что устройство при включении питания само устанавливается в описанное выше исходное нулевое состояние благодаря разряженным конденсаторам 11 RC-цепей элементов задержки и не нуждается в начальном сбросе.

Далее работа устройства рассматривается для случая n=4. При поступлении первого счетного импульса на выходе элемента ИЛИ-НЕ 5 появляется уровень логического нуля, на выходе элемента ИЛИ-НЕ 6 - уровень логической единицы, так как на шине 8 сброса уже поддерживается уровень логического нуля. Поэтому на первом и втором управляющих входах мультиплексора 7 в течение первого счетного импульса будет поддерживаться соответственно уровень логического нуля и уровень логической единицы. При такой комбинации сигналов на управляющих входах мультиплексора 2 на его разрядные выходы передаются сигналы, поступающие на входы второго канала его разрядов, т.е. с выходов вторых RC-элементов задержки. Поскольку конденсаторы 11 RC-цепей этих элементов задержки после импульса сброса поддерживаются разряженными, в течение первого счетного импульса на всех выходах мультиплексора 7 будет поддерживаться уровень логического нуля, т.е. двоичный код (00000) хранящегося во вторых RC-элементах 4 задержки числа "0" (младший разряд кода здесь и далее в тексте - справа). Этот код нулевого состояния устройства одновременно поддерживает разряженное состояние конденсатора 11 RC-цепей вторых RC-элементов 4 задержки и подается на разрядные входы второго слагаемого комбинационного сумматора 2 для обеспечения операции суммирования с кодом первого счетного импульса, подаваемого на разрядные входы первого слагаемого комбинационного сумматора 2 (код счетного импульса, поступающего через элементы ИЛИ-НЕ 5 и 6 на вход младшего разряда первого слагаемого комбинационного сумматора 2 равен "0001", поскольку входы всех разрядов, кроме младшего первого слагаемого, соединены с общей шиной, имеющей уровень логического нуля). Таким образом, в течение длительности поступившего счетного импульса код этого импульса и код предыдущего, в данном случае нулевого состояния устройства, на входах слагаемых комбинационного сумматора 2 поддерживается неизменным, на выходах комбинационного сумматора 2 присутствует код суммы "0001", следовательно, заряжается конденсатор 11 RC-цепи первого RC-элемента 3.1 задержки, подключенного к выходу младшего разряда комбинационного сумматора 2. Постоянная времени RC-цепей выбирается такой, чтобы конденсатор 11 до среза счетного (информационного) импульса успел зарядиться до уровня логической единицы (или разрядиться до уровня логического нуля, если был заряжен). Таким образом, к концу первого счетного импульса код нового состояния устройства (0001) запоминается на конденсаторах 11 RC-цепей первых RC-элементов 3 задержки, а конденсаторы 11 RC-цепей вторых RC-элементов задержки в это время еще "хранят" код предыдущего состояния устройства (0000).

По окончании первого счетного импульса на выходе элемента ИЛИ-НЕ 5 восстанавливается уровень логической единицы, на выходе элемента ИЛИ-НЕ 6 - уровень логического нуля, следовательно, на входах первого слагаемого комбинационного сумматора 2 также восстанавливается исходный уровень логического нуля. На первом и втором управляющих входах мультиплексора 7 восстанавливаются исходные уровни соответственно логической единицы и логического нуля. А при такой комбинации сигналов на управляющих входах мультиплексора 7, как было указано выше, на его выходы передается код числа, запомненный на конденсаторах RC-цепей первых RC-элементов 3 задержки, в нашем случае - это код числа "1" (0001). Этот код поступает на входы второго слагаемого комбинационного сумматора 2, а так как на всех входах первого слагаемого последнего в это время - уровень логического нуля, то на его разрядных выходах будет тот же код "0001". Он будет поддерживать запомненный после первого счетного импульса на конденсаторах 11 RC-цепей первых RC-элементов 3 задержки код числа "1" (0001). Одновременно (при появлении кода "0001+ на разрядных выходах мультиплексора 7 после первого счетного импульса) начинается заряд конденсатора 11 RC-цепи второго RC-элемента задержки 4, подключенного к выходу младшего разряда мультиплексора 7. Постоянная времени RC-цепей элементов 4 задержки выбирается такой, чтобы до поступления счетного импульса конденсатор успел зарядиться до уровня логической единицы (или разрядиться до уровня логического нуля, если был заряжен). Таким образом, в интервале между счетными импульсами код нового состояния устройства (в нашем случае это код числа "1") запоминается на конденсаторах 11 RC-цепей вторых RC-элементов 4 задержки. Следовательно, между первым и вторым счетными импульсами устройство находится в своем первом устойчивом состоянии: на конденсаторах RC-цепей элементов 3 и 4 задержки хранится код (0001) состояния устройства, которое оно приняло после первого импульса.

При поступлении очередного счетного импульса (в нашем случае второго) устройство работает аналогично: в течение длительности счетного импульса код 0001 числа "1", хранящийся в элементах 4 задержки, через мультиплексор 7 подается на входы второго слагаемого комбинационного сумматора 2 для обеспечения суммирования кода состояния (0001) устройства, соответствующего числу "1", с кодом второго счетного импульса (0001), подаваемого на входы первого слагаемого этого комбинационного сумматора. В результате на разрядных выходах комбинационного сумматора 2 в течение второго счетного импульса будет присутствовать код числа "2" - "0010", при этом разряжается конденсатор RC-цепи элемента 3.1 задержки, подключенного к выходу первого разряда комбинационного сумматора 2, и заряжается конденсатор RC-цепи элемента 3.2 задержки, подключенного к выходу второго разряда комбинационного сумматора 2. По окончании второго счетного импульса код "0010", запомненный на конденсаторах первых RC-элементов 3 задержки, через мультиплексор 7 и комбинационный сумматор 2 поддерживает сам себя, и одновременно разряжается конденсатор RC-цепи элемента 4.1 задержки, подключенного к выходу первого разряда мультиплексора 7, и заряжается конденсатор RC-цепи элемента 4.2 задержки, подключенного к выходу второго разряда мультиплексора 7. Следовательно, после второго счетного импульса на конденсаторах RC-цепей элементов 3, 4 задержки хранится код "0010", соответствующий числу "2", устройство находится в своем устойчивом состоянии и сохраняет его до поступления следующего счетного импульса.

При поступлении третьего и последующих счетных импульсов устройство работает аналогично и последовательно принимает свои состояния до кода "1111" числа "15". При поступлении шестнадцатого счетного импульса на выходе переноса комбинационного сумматора 2 появляется сигнал с уровнем логической единицы с длительностью, равной длительности счетного импульса, который поступает на выходную шину 13, как импульс переполнения устройства. А по окончании шестнадцатого счетного импульса конденсаторы RC-цепей всех RC-элементов задержки оказываются разряженными, т.е. устройство возвращается в исходное нулевое состояние.

Таким образом, устройство изменяет свое состояние по срезу каждого счетного импульса и только в том случае, если длительность импульса, поступающего по входной шине 1, окажется больше некоторого заданного разработчиком значения и будет достаточной для перезаряда конденсатора RC-цепей элементов 3 задержки (от уровня логического нуля до уровня логической единицы или наоборот), в противном случае по окончании счетного импульса устройство сохраняет свое текущее состояние. Поскольку промежуточные состояния устройства "хранятся" на емкостях элементов задержки, т.е. пассивных инерционных элементах памяти - конденсаторах, а устройство содержит только элементы комбинационной логики, т. е. не имеет в своем составе активных бистабильных функциональных элементов, оно устойчиво и к внутренним помехам, в том числе к помехам в шинах питания. Шина 8 сброса устройства обладает приоритетом перед счетным входом 1, при этом при подаче импульса сброса по шине 8 сброса на разрядных выходах мультиплексора 7 код "0000" устанавливается сразу по фронту импульса сброса и сохраняется в течение этого импульса, однако нулевое состояние устройство принимает только в том случае, если длительность этого импульса будет достаточной для перезарядки емкостей RC-цепей первых RC-элементов задержки. В противном случае по окончании импульса "сброса" (помехи) устройство сохраняет свое состояние, которое оно имело до поступления указанного импульса по шине 8 сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1574146A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1572383A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1991 |

|

SU1817645A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1989 |

|

SU1785407A2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1992 |

|

RU2022463C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1990 |

|

SU1814487A1 |

| МНОГОКАНАЛЬНЫЙ ДАТЧИК ОДИНОЧНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2118042C1 |

Изобретение относится к импульсной технике и может использоваться в помехоустойчивых счетных устройствах. Цель изобретения - повышение надежности. Устройство содержит входную шину 1, многоразрядный комбинационный сумматор 2. Цель достигается введением по числу разрядов сумматора первых 3 и вторых 4 элементов задержки, элементов ИЛИ - НЕ 5 и 6, мультиплексора 7. Резистивно-емкостные элементы задержки помимо защиты от помех запоминают промежуточные состояния выходов многоразрядного комбинационного сумматора 2, что позволяет уменьшить количество элементов по сравнению с прототипом. 1 ил.

УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ, содержащее входную шину, n-разрядный комбинационный сумматор, два RC-элемента задержки и первый элемент ИЛИ-НЕ, отличающееся тем, что, с целью повышения надежности путем упрощения, в него введены 2n-2 RC-элементов задержки, второй элемент ИЛИ-НЕ и двухканальный n-разрядный мультиплексор, первый вход первого элемента ИЛИ-НЕ соединен с входной шиной, второй вход - с шиной сброса и с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и с первым управляющим входом двухканального n-разрядного мультиплексора, второй управляющий вход которого соединен с выходами второго элемента ИЛИ-НЕ и с входом младшего разряда первого слагаемого n-разрядного комбинационного сумматора, входы остальных разрядов первого слагаемого n-разрядного комбинационного сумматора соединены с общей шиной, входы разрядов второго слагаемого - с выходами соответствующих разрядов двухканального n-разрядного мультиплексора, выходы разрядов n-разрядного комбинационного сумматора через соответствующие первые RC-элементы задержки подключены к соответствующим входам первого канала двухканального n-разрядного мультиплексора, выходы разрядов которого через соответствующие вторые RC-элементы задержки соединены с соответствующими входами второго канала двухканального n-разрядного мультиплексора.

| Устройство для счета импульсов | 1979 |

|

SU797078A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-01-09—Публикация

1987-04-06—Подача