Изобретение относится к импульсной технике, может быть использовано отдельно или в составе различных цифровых устройств в условиях воздействия помех и является усовершенствованием основного изобретения по авт.св. N 1464893.

В основном изобретении описано устройство для счета импульсов, содержащее входную шину, n-разрядный комбинационный сумматор, 2n RC-элементов задержки, первый и второй элементы ИЛИ-НЕ и двухканальный n-разрядный мультиплексор, первый вход первого элемента ИЛИ-НЕ соединен со входной шиной, второй вход с шиной сброса и с первым входом второго элемента ИЛИ-НЕ второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и с первым управляющим входом двухканального n-разрядного мультиплексора, второй управляющий вход которого соединен с выходом второго элемента ИЛИ-НЕ и со входом младшего разряда первого слагаемого n-разрядного комбинационного сумматора, входы остальных разрядов первого слагаемого n-разрядного комбинационного сумматора соединены с общей шиной, входы разрядов второго слагаемого с выходами соответствующих разрядов двухканального n-разрядного мультиплексора, выходы разрядов n-разрядного комбинационного сумматора через соответствующие первые RC-элементы задержки подключены к соответствующим входам первого канала двухканального n-разрядного мультиплексора, выходы разрядов которого через соответствующие вторые RC-элементы задержки соединены с соответствующими входами второго канала двухканального n-разрядного мультиплексора.

Недостатком известного устройства является относительно низкая достоверность результатов счета импульсов, обусловленная возможностью отказов элементов из-за сложности схемы и возможностью сбоев в работе при воздействии "пачек" помех по входной шине. Отказы элементов устройства и указанного типа сбои в его работе, искажающие результаты счета импульсов, остаются необнаруженными, поскольку устройство не обладает способностью их обнаружения.

Целью изобретения являются повышение достоверности результатов счета импульсов за счет обеспечения постоянного самоконтроля функционирования.

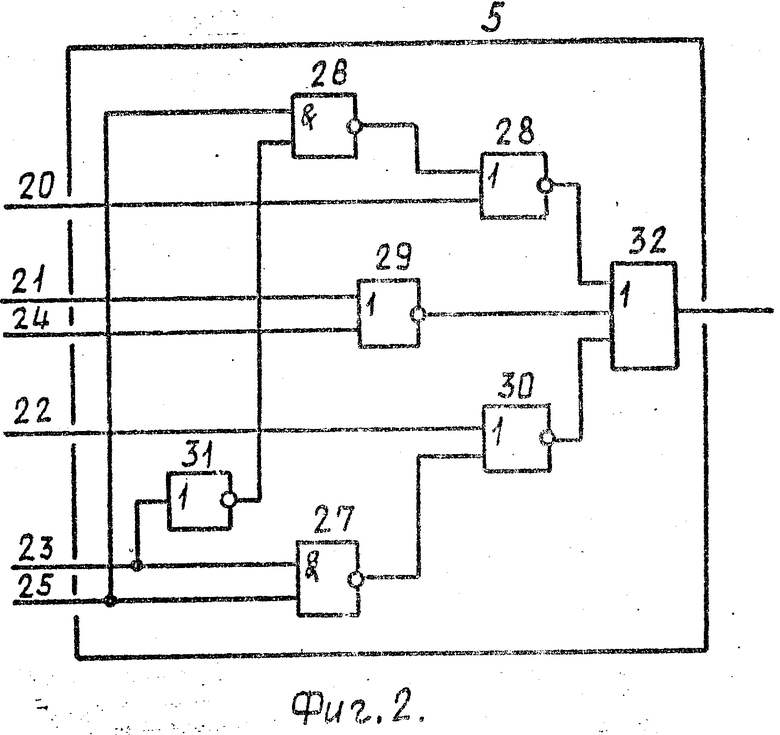

Поставленная цель достигается тем, что в устройство для счета импульсов по авт. св. N 1464893, содержащее входную шину, n-разрядный комбинационный сумматор, 2n RC-элементов задержки, первый и второй элементы ИЛИ-НЕ и двухканальный n-разрядный мультиплексор, первый вход первого элемента ИЛИ-НЕ соединен с входной шиной, второй вход с шиной сброса и с первым входом второго элемента ИЛИ-НЕ, второй вход которого соединен с выходом первого элемента ИЛИ-НЕ и с первым управляющим входом двухканального n-разрядного мультиплексора, второй управляющий вход которого соединен с выходом второго элемента ИЛИ-НЕ и с входом младшего разряда первого слагаемого n-разрядного комбинационного сумматора, входы остальных разрядов первого слагаемого n-разрядного комбинационного сумматора соединены с общей шиной, входы разрядов второго слагаемого с выходами соответствующих разрядов двухканального n-разрядного мультиплексора, выходы разрядов n-разрядного комбинационного сумматора через соответствующие первые RC-элементы задержки подключены к соответствующим входам первого канала двухканального n-разрядного мультиплексора, выходы разрядов которого через соответствующие вторые RC-элементы задержки соединены с соответствующими входами второго канала двухканального n-разрядного мультиплексора, введены блок сравнения двух чисел А и В, формирователь сигнала ошибки, формирователь опросного импульса и шина сигнала ошибки, причем входы разрядов числа А блока сравнения кодов соединены с выходами соответствующих разрядов n-разрядного комбинационного сумматора, входы разрядов числа В со входами соответствующих разрядов первого канала двухканального n-разрядного мультиплексора, выходы "A>B", "A=B" и "A<B" соединены соответственно с первым, вторым и третьим входами формирователя сигнала ошибки, четвертый вход которого соединен с выходом переноса n-разрядного комбинационного сумматора, пятый вход с выходом второго элемента ИЛИ-НЕ и с входом формирователя опросного импульса, выход которого соединен с шестым входом формирователя сигнала ошибки, выход которого соединен с шиной сигнала ошибки. При этом формирователь сигнала ошибки содержит два элемента И-НЕ, три элемента ИЛИ-НЕ, элемент НЕ и элемент ИЛИ, причем первые входы первого и второго элементов И-НЕ объединены и соединены с шестым входом формирователя сигнала ошибки, второй вход первого элемента И-НЕ соединен с выходом элемента НЕ, вход которого соединен с вторым входом второго элемента И-НЕ и с четвертым входом формирователя сигнала ошибки, выход первого элемента И-НЕ соединен с первым входом первого элемента ИЛИ-НЕ, второй вход которого соединен с первым входом формирователя сигнала ошибки, первый и второй входы второго элемента ИЛИ-НЕ соединены соответственно с вторым и пятым входами формирователя сигнала ошибки, первый вход третьего элемента ИЛИ-НЕ соединен с выходом второго элемента И-НЕ, второй вход с третьим входом формирователя сигнала ошибки, входы элемента ИЛИ соединены с выходами первого, второго и третьего элементов ИЛИ-НЕ, а вход соединен с выходом формирователя сигнала ошибки.

Указанная совокупность признаков обеспечивает положительный эффект повышение достоверности результатов счета импульсов. Это достигнуто обеспечением постоянного самоконтроля за правильностью функционирования устройства, как перед началом работы, так и в процессе счета импульсов, и формированием сигнала ошибки (отказа, сбоя), если состояния счетного устройства отличаются от допустимых ("штатных").

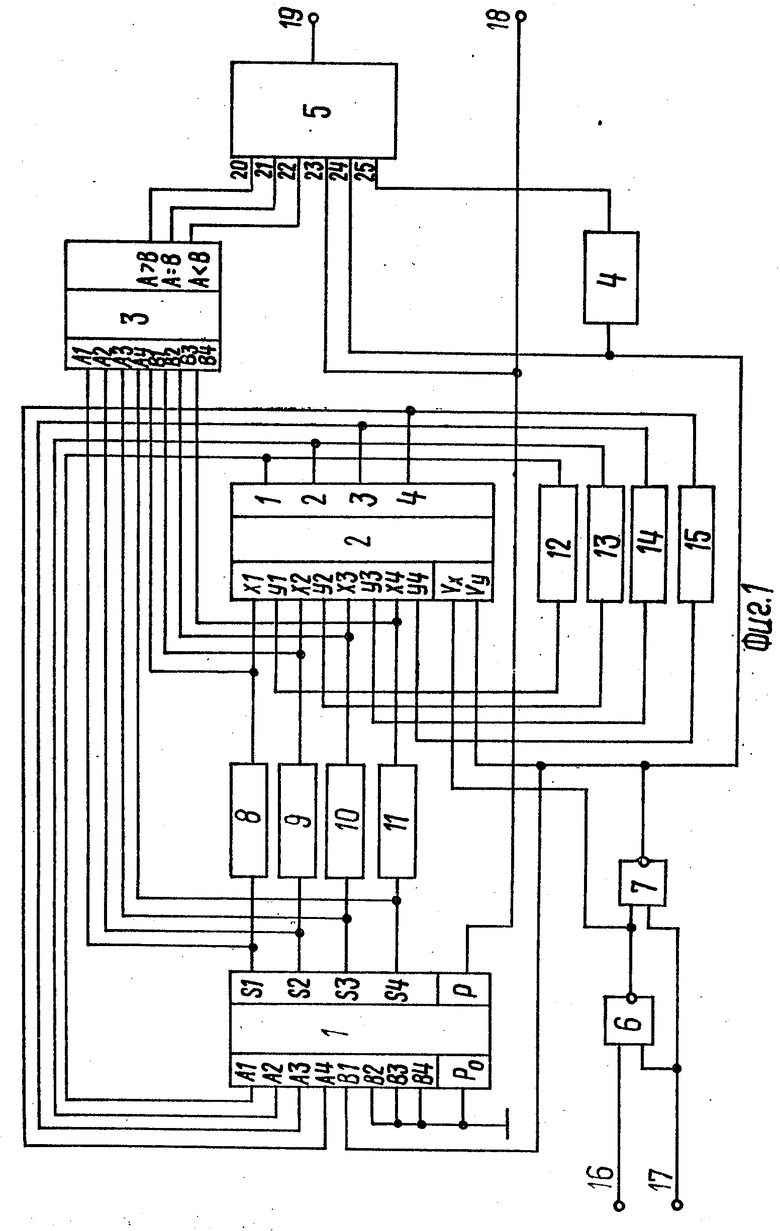

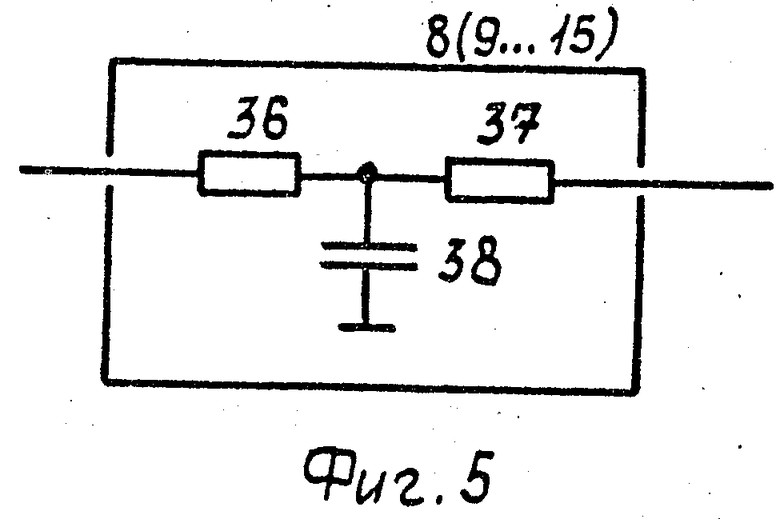

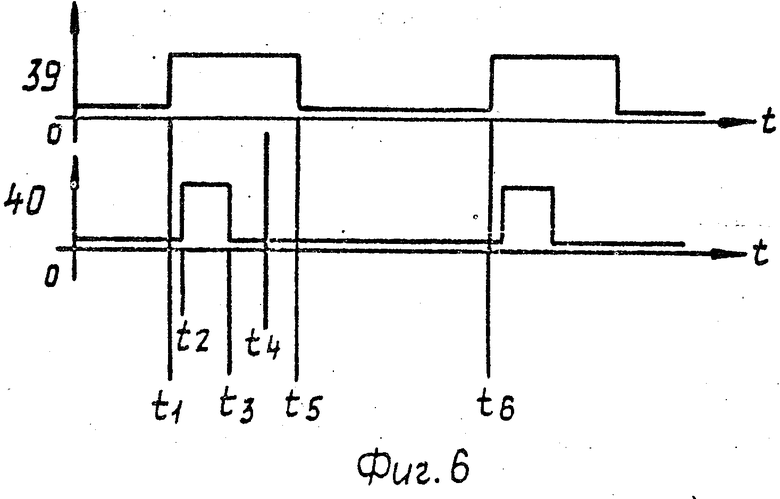

На фиг.1 приведена функциональная схема заявляемого устройства для счета импульсов; на фиг.2-5 электрические принципиальные схемы возможных вариантов реализации отдельных функциональных блоков устройства; на фиг.6 временная диаграмма выходного сигнала формирователя опросных импульсов.

Устройство для счета импульсов содержит комбинационный сумматор 1, мультиплексор 2, блок 3 сравнения двух чисел А и В, формирователь 4 опросного импульса, формирователь 5 сигнала ошибки, элементы 6, 7 ИЛИ-НЕ, RC-элементы 8. 15, входную шину 16, шину 17 сброса, выходную шину 18 и шину 19 сигнала ошибки. Первый вход элемента 6 ИЛИ-НЕ соединен с входной шиной 16, второй вход с шиной 17 сброса и с первым входом элемента 7 ИЛИ-НЕ, второй вход которого соединен с выходом элемента 6 ИЛИ-НЕ и с первым управляющим входом мультиплексора 2, второй управляющий вход которого соединен с выходом элемента 7 ИЛИ-НЕ и с входом младшего разряда первого слагаемого сумматора 1. Входы остальных разрядов первого слагаемого сумматора 1 соединены с общей шиной, входы разрядов второго слагаемого с выходами соответствующих разрядов мультиплексора 2. Разрядные выходы сумматора 1 через соответствующие RC-элементы 8.11 подключены к соответствующим разрядным входам первого канала мультиплексора 2, выходы разрядов которого через соответствующие RC-элементы 12. 15 соединены с соответствующими разрядными входами его второго канала. Входы разрядов числа А блока 3 сравнения двух чисел соединены с выходами соответствующих разрядов сумматора 1, входы разрядов числа В с входами соответствующих разрядов первого канала мультиплексора 2, а выходы "A>B", "A=B" и "A<B" соответственно с первым 21, вторым 22 и третьим 23 входами формирователя 5 сигнала ошибки, четвертый 24 вход которого соединен с выходом переноса сумматора 1 и с выходной шиной 18, пятый 25 вход с выходом элемента ИЛИ-НЕ 7 и с входом формирователя 4 опросного импульса, выход которого соединен с шестым 26 входом формирователя: 5 сигнала ошибки, выход которого подключен к шине 19 сигнала ошибки.

Формирователь 5 сигнала ошибки содержит (см. фиг.2) элементы 26, 27 И-НЕ, элементы 28, 29, 30 И-НЕ, элемент НЕ 31 и элемент 32 ИЛИ. При этом первые входы элементов 26, 27 И-НЕ объединены и подключены к входу 25 формирователя 5, второй вход элемента 26 И-НЕ соединен с выходом элемента 31 НЕ, вход которого подключен ко второму входу элемента 27 И-НЕ и ко входу 23 формирователя 5. Выход элемента 26 И-НЕ соединен с первым входом элемента 28 ИЛИ-НЕ, второй вход которого соединен с входом 20 формирователя 5. Первый и второй входы элемента 29 ИЛИ-НЕ соединены соответственно с входами 21 и 24 формирователя 5. Первый вход элемента 30 ИЛИ-НЕ соединен с выходом 27 И-НЕ, второй вход с входом 22 формирователя 5. Входы элемента 32 ИЛИ соединены с выходами элементов 28, 29, 30 ИЛИ-НЕ, а выход соединен с выходом формирователя 5.

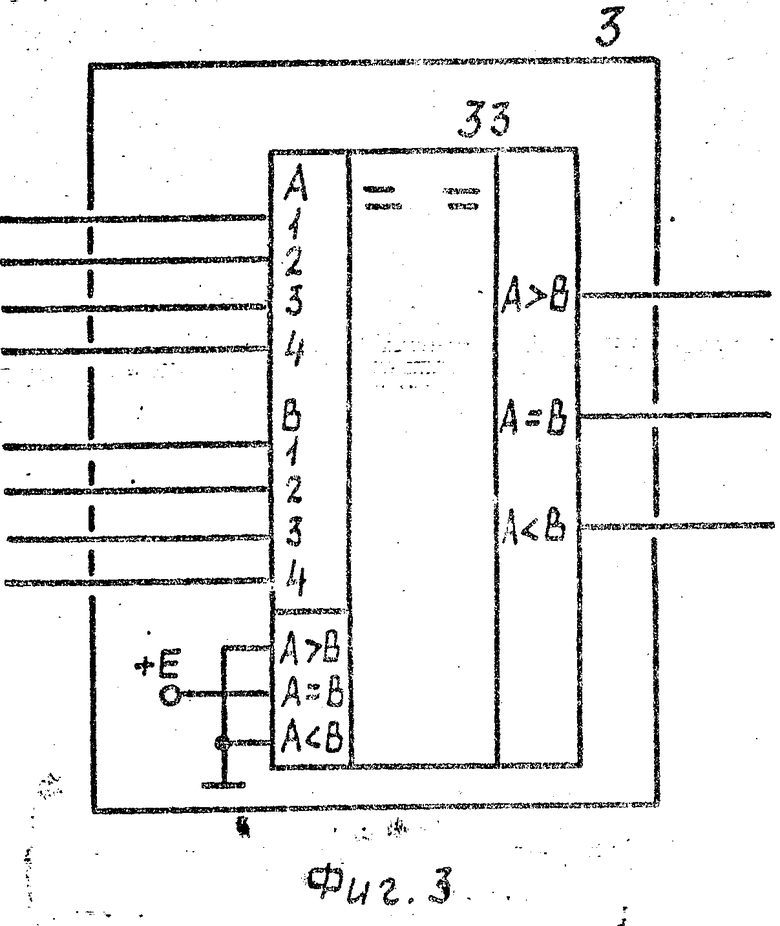

Блок 3 сравнения двух чисел выполняется на типовых схемах сравнения двух двоичных чисел, в том числе на схемах в интегральном исполнении, например, на микросхемах 564 ИП2 (см. фиг.3, поз.33), К561ИП2 и им подобных.

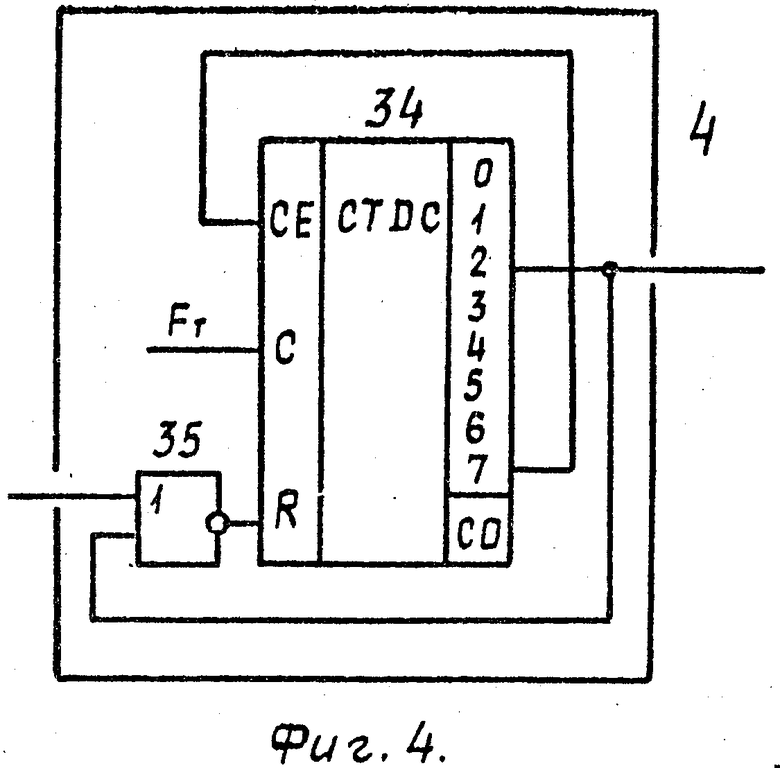

Формирователь 4 опросного импульса формирует по фронту каждого счетного импульса короткий одиночный импульс. Этот импульс задержан относительно фронта счетного импульса (для исключения ложного сигнала на входе 19) на время большее, чем длительность переходных процессов в сумматоре 1 и блоке 3 сравнения чисел после поступления счетного импульса, а срез его формируется раньше, чем конденсаторы RC-элементов 8.11 после поступления счетного импульса зарядятся до уровня логической "1" или разрядятся до уровня логического "0" (в зависимости от кода на разрядных выходах сумматора 1). Формирователь 4 выполняется по известным схемам, например, по схеме фиг.4, где он выполнен на счетчике 34 типа 564 ИЕ9 с встроенными дешифраторами состояния и на элементе 35 ИЛИ-НЕ микросхемы 564 ЛЕ5.

Постоянная времени всех RC-элементов 8.15 (см. фиг.5) устройства одинаковая и выбирается исходя из требуемого уровня помехоустойчивости устройства. Резисторы на выходе RC-элементов 8.15 (см. фиг.5 поз.37) не являются обязательными элементами схемы: они нужны лишь в частных случаях, например, для защиты отдельных серий микросхем (например, серии 164, 564) от так называемого "тиристорного эффекта" при относительно длительных фронтах и срезах сигналов на входах этих микросхем.

Построение заявляемого устройства с количеством разрядов более четырех, то есть больше, чем показано на фиг.1, осуществляется путем простого увеличения разрядов сумматора 1, мультиплексора 2, блока 3 сравнения чисел и количества RC-элементов 8.15. Можно также построить многоразрядное счетное устройство путем последовательного включения нескольких заявляемых устройств, при этом вход переноса сумматора второго устройства соединяется с выходной шиной 18 первого устройства, вход переноса сумматора третьего устройства с входной шиной 18 второго и т.д. Количество остальных элементов заявляемого устройства при увеличении его разрядности не увеличивается.

Работает устройство для счета импульсов (фиг.1) следующим образом.

После включения питания при отсутствии управляющих сигналов, то есть когда на входной шине 16 и шине 17 сброса присутствуют уровни логического "0", конденсаторы RC-элементов 8.15 разряжены, на входе элемента 6 ИЛИ-НЕ поддерживается уровень логической "1", на выходе элемента 7 ИЛИ-НЕ уровень логического "0" (здесь и далее в тексте уровни сигналов соответствуют устройству, реализованному на базе микросхем с положительной логикой). Следовательно, на всех разрядных входах первого слагаемого сумматора 1 будут присутствовать уровни логического "0", на первом управляющем входе мультиплексора 2 уровень логической "1", на втором управляющем входе уровень логического "0". При указанной комбинации сигналов на управляющих входах на выходы мультиплексора 2 "поступает" информация с соответствующих разрядных входов его первого канала (точнее на его выходах активно формируются уровни сигналов, повторяющие уровни сигналов на входах, в данном случае на входах первого канала). Следовательно, на выходах мультиплексора 2 присутствуют уровни логического "0" (поскольку конденсаторы RC-элементов 8.11 разряжены). На разрядных выходах сумматора 1 также присутствуют уровни логического "0", которые поддерживают в разряженном состоянии конденсаторы RC-элементов 8.11, а также конденсаторы RC-элементов 12.15. Поскольку на всех входах чисел A и В блока 3 сравнения чисел присутствуют уровни логического "0", на его выходе "А= В" будет уровень логической "1", на остальных двух выходах уровни логического "0". Эти сигналы поступают на первые три входа формирователя 5 сигнала ошибки. На остальных входах этого формирователя присутствуют уровни логического "0", на его выходе уровень логического "0", что означает отсутствие сигнала ошибки. Такое состояние устройства, когда конденсаторы всех RC-элементов 8.15 разряжены, на всех выходах сумматора 1, мультиплексора 2, на выходной шине 18 и шине 19 сигнала ошибки присутствуют уровни логического "0", является исходным и сохраняется до появления счетных импульсов по входной шине 16 (появление импульса сброса по шине 17 сброса в исходном состоянии устройства приведет только к изменению уровня сигнала на выходе элемента 6 ИЛИ-НЕ, что не приведет к изменению исходных состояний остальных элементов устройства).

Необходимо отметить, что при включении питания благодаря разряженным конденсаторам RC-элементов 8.1, устройство само устанавливается в исходное состояние и не нуждается в начальном сбросе.

Сброс устройства в исходное состояние (при необходимости) в процессе работы осуществляется подачей по шине 17 сброса сигнала с уровнем логической "1". При этом в течение длительности импульса сброса на выходах элементов 6, 7 ИЛИ-НЕ и, следовательно, на обоих управляющих входах мультиплексора 2 будут поддерживаться уровни логического "0". При наличии уровней логического "0" на обоих управляющих входах мультиплексора 2 на всех его выходах активно формируются уровни логического "0", поэтому конденсаторы RC-элементов 12.15 начинают разряжаться (которые до этого были заряжены) через малые выходные сопротивления выходов мультиплексора 2. Одновременно уровни логического "0" с выходов мультиплексора 2 поступают на разрядные входы второго слагаемого сумматора 1, и (поскольку при этом на всех разрядных входах первого слагаемого сумматора 1 присутствуют уровни логического "0") на его разрядных выходах в течение длительности импульса сброса присутствуют уровни логического "0". Следовательно, конденсаторы RC-элементов 8.11 также начинают разряжаться (которые до этого были разряжены) через малые выходные сопротивления разрядных выходов сумматора 1. Длительность импульса сброса выбирается такой, что в течение его длительности конденсаторы RC-элементов 8.15 полностью разряжаются (точнее разряжаются до уровня остаточного напряжения логического "0" на выходах сумматора 1 и мультиплексора 2).

После окончания импульса сброса на выходе элемента 6 ИЛИ-НЕ восстанавливается уровень логической "1", а на выходе элемента 7 ИЛИ-НЕ сохраняется уровень логического "0". Следовательно, на первом управляющем входе мультиплексора 2 будет уровень логической "1", на втором уровень логического "0". При такой комбинации сигналов на управляющих входах мультиплексора на его выходы выдаются логические уровни сигналов, имеющиеся на разрядных входах первого канала, то есть уровни логического "0" с разряженных в течение длительности импульса сброса конденсаторов RC-элементов 8.11. Следовательно, на выходах мультиплексора 2 после окончания импульса сброса сохраняются уровни логического "0", на разрядных выходах сумматора 1 также сохраняются уровни логического "0" (поскольку на всех разрядных входах первого и второго слагаемых сумматора 1 сохраняются уровни логического "0"), конденсаторы RC-элементов 8.11, а также RC-элементов 12.15, остаются разряженными. Таким образом, после окончания импульса сброса устройство оказывается в описанном выше исходном состоянии.

Рассмотрим теперь работу устройства в режиме счета импульсов с постоянным самоконтролем правильности функционирования. При этом, для удобства изложения, рассмотрим сначала совместную работу функциональных элементов устройства, осуществляющих счет импульсов, а затем принцип самоконтроля и работу функциональных элементов (блока 3 сравнения чисел, формирователя 4 опросного импульса и формирователя 5 сигнала ошибки), осуществляющих самоконтроль функционирования. Такое раздельное рассмотрение работы указанных функциональных частей устройства целесообразно и потому, что элементы устройства, осуществляющие самоконтроль, не влияют на работу элементов, осуществляющих счет импульсов.

При поступлении первого счетного импульса на выходе элемента 6 ИЛИ-НЕ появляется уровень логического "0", на выходе элемента 7 ИЛИ-НЕ уровень логической "1", так как на шине 17 сброса при работе поддерживается уровень логического "0". Поэтому на первом и втором управляющих входах мультиплексора 2 в течение длительности первого счетчика импульса будут присутствовать уровни логического "0" и логической "1" соответственно. При такой комбинации сигналов на управляющих входах мультиплексора 2 на его выходы "выдаются" сигналы, имеющиеся на входах второго канала, то есть на конденсаторах RC-элементов 12. 15. Поскольку конденсаторы RC-элементов 12.15 в исходном (нулевом) состоянии поддерживаются разряженными, в течение первого счетного импульса на всех выходах мультиплексора 2 будет поддерживаться уровень логического "0", то есть двоичный код 0000 хранящегося на конденсаторах RC-элементов 12. 15 числа 0 (младший разряд кода здесь и далее в тексте справа). Этот код нулевого состояния устройства одновременно поддерживает разряженное состояние конденсаторов RC-элементов 12.15 и подается на разрядные входы первого слагаемого сумматора 1 для обеспечения операции сложения с кодом первого счетного импульса 0001, подаваемого на разрядные входы его первого слагаемого. Таким образом, в течение длительности первого счетного импульса код счетного импульса (0001) и код предыдущего нулевого состояния устройства (0000) на входах слагаемых сумматора 1 поддерживаются неизменными, на разрядных выходах сумматора 1 присутствует код их суммы 0001, и, следовательно, заряжается конденсатор RC-элемента 8, подключенного к выходу младшего разряда сумматора 1. Постоянная времени RC-элементов 8.11 выбирается таким образом, чтобы конденсатор до среза счетного импульса успел зарядиться до уровня логической "1" (или разрядиться до уровня логического "0", если был до этого заряжен). Таким образом, до момента поступления среза первого счетного импульса код нового состояния (0001) устройства запоминается на конденсаторах RC-элементов 8. 11, а конденсаторы RC-элементов 12.15 в это время еще "хранят" код предыдущего состояния (0000) устройства.

После окончания первого счетного импульса на выходе элемента 6 ИЛИ-НЕ восстанавливается уровень логической "1", на выходе элемента 7 ИЛИ-НЕ уровень логического "0", следовательно, на входе младшего разряда первого слагаемого сумматора 1 также восстанавливается исходный уровень логического "0". На первом и втором управляющих входах мультиплексора 2 также восстанавливаются исходные уровни соответственно логической "1" и логического "0". А при такой комбинации сигналов на управляющих входах мультиплексора 2 на его выходы выдается, как было указано выше, код числа, запомненный на конденсаторах RC-элементов 8.11, в нашем случае это код числа 1 (0001). Этот код поступает на входы второго слагаемого сумматора 1, на входах первого слагаемого которого в это время уже восстановился код исходного уровня сигналов (0000). Поэтому на разрядных выходах сумматора 1 будет присутствовать тот же код 0001, который будет поддерживать запомненный в течение первого счетного импульса на конденсаторах RC-элементов 8.11 код числа 1 (0001).

Одновременно, то есть после снятия первого счетного импульса, начинается заряд конденсатора RC-элемента 12, подключенного к выходу младшего разряда мультиплексора 2. Постоянная времени RC-элементов 12.15 выбирается таким образом, чтобы до поступления очередного счетного импульса конденсатор успел зарядиться до уровня логической "1" (или разрядиться до уровня логического "0", если был до этого заряжен). Таким образом, в интервале между первым и вторым счетными импульсами код нового состояния (0001) "запоминается" на конденсаторах RC-элементов 12.15, и после завершения процесса заряда конденсатора RC-элемента 12 устройство находится в первом своем устойчивом состоянии: на конденсаторах как RC-элементов 8.11, так и RC-элементов 12.15 "хранится" код нового состояния 0001, соответствующего числу 1, которое приняло устройство после первого счетного импульса.

При поступлении очередного счетного импульса (в нашем случае вторичного) устройство работает аналогично: в течение длительности счетного импульса код числа 1 (0001), хранящийся на конденсаторах RC-элементов 12.15, через мультиплексор 2 подается на входы разрядов второго слагаемого сумматора 1 для обеспечения операции сложения кода состояния устройства, соответствующего числу 1 (0001), с кодом второго счетного импульса (0001), подаваемого на входы первого слагаемого сумматора 1. В результате на разрядных выходах сумматора 1 в течение длительности второго счетного импульса будет присутствовать код числа 2 (0010), при этом начинает разряжаться конденсатор RC-элемента 8, подключенный к выходу младшего разряда сумматора 1, и начинает заряжаться конденсатор RC-элемента 9, подключенного к выходу второго разряда сумматора 1.

После окончания второго счетного импульса код числа 2 (0010), запомненный в течение длительности этого импульса на конденсаторах RC-элементов 8.11, через мультиплексор 2 и сумматор 1 поддерживает сам себя. При этом разряжается конденсатор RC-элемента 12, подключенного к выходу младшего разряда мультиплексора 2, и заряжается конденсатор RC-элемента 13, подключенного к выходу второго разряда мультиплексора 2. Таким образом, после второго счетного импульса по окончании процессов перезаряда конденсаторов RC-элементов 12, 13 на конденсаторах RC-элементов 8.11 и на конденсаторах RC-элементов 12.15 хранится код (0010), соответствующий числу 2, и устройство сохраняет это новое свое состояние до поступления третьего счетного импульса.

При поступлении третьего и последующих счетных импульсов устройство работает аналогично и последовательно принимает состояния до состояния, соответствующего числу 15. При поступлении шестнадцатого счетного импульса на выходе переноса сумматора 1 появляется сигнал переноса с уровнем логической "1" и длительностью, равной длительности счетного импульса, который поступает на выходную шину 18 в качестве импульса переполнения устройства. А после окончания шестнадцатого счетного импульса конденсаторы всех RC-элементов 8. 15 оказываются разряженными, то есть устройство возвращается в исходное нулевое состояние.

Таким образом, устройство изменяет свое состояние по срезу каждого счетного импульса и только в том случае, если длительность счетного импульса окажется достаточной для перезаряда конденсаторов RC-элементов 8.11, в противном случае после окончания счетного импульса (импульса сброса) устройство сохраняет свое текущее состояние.

Рассмотрим теперь принцип самоконтроля функционирования, принятый в устройстве, и работу его функциональных элементов, осуществляющих самоконтроль.

Самоконтроль устройства осуществляется после включения питания постоянно как в исходном состоянии, так и в процессе счета импульсов, при этом функциональные элементы устройства, осуществляющие этот контроль (блок 3 сравнения двух чисел, формирователь 4 опросного импульса и формирователь 5 сигнала ошибки) на работу остальных функциональных элементов устройства влияния, как указывалось выше, не оказывают.

Основан самоконтроль на проверке состояний устройства в определенные моменты времени, которые дают необходимую информацию, позволяющую сделать вывод о работоспособности устройства. Как следует из описания работы устройства, в исходном состоянии на конденсаторах как RC-элементов 8.11, так и RC-элементов 12.15 хранится одинаковый код нулевого состояния устройства, а при подаче первых пятнадцати счетных импульсов (для четырехразрядного устройства) с разрядных выходов сумматора 1 подается код нового (будущего) состояния устройства, который на единицу больше кода текущего состояния устройства, хранящего на конденсаторах RC-элементов 8.11. И эта разность кодов на выходах сумматора 1 и выходах RC-элементов 8.11 сохраняется до окончания процесса перезаряда конденсаторов RC-элементов 8.11. После окончания указанных (с 1 по 15) счетных импульсов коды на выходах сумматора 1 и RC-элементов 8.11 снова становятся одинаковыми (код нового состояния), и этот новый код сам себя поддерживает по замкнутой цепи: RC-элементы 8.11 мультиплексор 2 сумматор 1 RC-элементы 8.11. При этом RC-элементы 12.15 служат для поддержания на входах второго слагаемого сумматора 1 кода текущего состояния устройства в течение длительности счетных импульсов (для обеспечения операции сложения).

При поступлении шестнадцатого счетного импульса картина иная: сразу по фронту счетного импульса с выходов сумматора 1 на входы RC-элементов 8.11 подается код нулевого состояния (0000) устройства, а на конденсаторах RC-элементов 8.11 в это время еще имеется код (1111), текущего состояния устройства, соответствующего числу 15, то есть в данном случае код на выходах сумматора 1 будет меньше кода, хранящегося на конденсаторах RC-элементов 8. 11. При этом на выходе переноса сумматора 1 должен формироваться сигнал переноса.

Из изложенного следует, что сравнивая коды на выходах сумматора 1 и RC-элементов 8.11 в начале счетных импульсов (при подаче первых 15 счетных импульсов код на выходах сумматора 1 должен быть больше кода на конденсаторах RC-элементов 8.11, при подаче шестнадцатого счетного импульса код на выходах сумматора 1 меньше кода на конденсаторах RC-элементов 8.11 при условии наличия сигнала переноса у сумматора 1), а также между счетными импульсами и в исходном состоянии (коды на выходах сумматора 1 и на конденсаторах RC-элементов 8. 11 должны совпадать) можно с достаточно высокой достоверностью сделать вывод о работоспособности устройства. Это и используется для самоконтроля функционирования заявляемого устройства. При этом сравнение указанных кодов осуществляет блок 3 сравнения чисел (см. фиг.1, фиг.3), который непрерывно анализиpует коды в указанных точках устройства. Однако, результаты сравнения кодов при поступлении первых 15 счетных импульсов "отбираются" устройством для формирования результата самоконтроля только в течение длительности импульсов (см. фиг.6, поз.40) формирователя 4 опросных импульсов, формируемых последним, как было указано выше, с некоторой задержкой относительно фронта счетных импульсов (см. фиг.6, поз.39). При несоответствии состояний устройства в опрашиваемые моменты указанным выше требованиям формирователь 5 сигнала ошибки формирует соответствующий сигнал на своем выходе.

Рассмотрим теперь более подробно работу функциональных элементов устройства, осуществляющих самоконтроль.

В исходном состоянии, как было указано выше, на выходах сумматора 1 и на конденсаторах RC-элементов 8.11 имеется одинаковый код (0000) нулевого состояния устройства. Поэтому на выходе "А=В" блока 3 сравнения чисел присутствует уровень логической "1" (на других выходах уровень логического "0"), который поступает на вход 21 формирователя 5 сигнала ошибки. В последнем этот сигнал поступает (см. фиг.2) на один из входов элемента 29 ИЛИ-НЕ и поддерживает на его выходе уровень логического "0", независимо от уровня сигналов на другом входе. Если бы из-за какого-либо отказа (сбоя) устройства коды на выходах сумматора 1 и конденсаторах RC-элементов 8.11 отличались, то на выходе "А=В" блока 3 сравнения чисел присутствовал бы уровень логического "0", на выходе элемента 29 ИЛИ-НЕ (см. фиг.2) уровень логической "1" (поскольку на его другом входе при отсутствии счетного импульса имеется уровень логического "0"), что привело бы к появлению на выходе элемента 32 ИЛИ уровня логической "1" сигнала ошибки.

При подаче на устройство с первого по пятнадцатый счетных импульсов по фронту каждого импульса (фиг. 6, моменты t1, t6,) на выходах сумматора 1 устанавливается код нового (будущего) состояния устройства, который на единицу больше кода текущего состояния устройства, имеющегося в это время на конденсаторах RC-элементов 8.11, и эта разность сохраняется до окончания процесса перезаряда конденсаторов RC-элементов 8.11 (см. фиг.6, до момента t4). При этом уровень логической "1" присутствует на выходе "А>В" блока 3 сравнения чисел, который поступает на вход 20 формирователя 5 сигнала ошибки. Одновременно по фронту каждого из указанных счетных импульсов запускается формирователь 4 опросного импульса и с небольшой задержкой, превышающей задержку сигналов на выходах блока 3 сравнения чисел, формирует короткий импульс (см. фиг. 6, поз.40, интервал t3-t2), который поступает на вход 25 формирователя 5 сигнала ошибки, на входах 21 и 22 которого в это время имеются уровни логического "0", на входе 23 также уровень логического "0" (поскольку нет сигнала переноса на выходе сумматора 1), на входе 24 уровень логической "1" (поскольку есть счетный импульс). В результате на выходе элемента 26 И-НЕ формирователя 5 сигнала ошибки (см. фиг.2) на время длительности опросного импульса появляется уровень логического "0", который поступает на вход элемента 28 ИЛИ-НЕ. Но так как на другом входе элемента 28 ИЛИ-НЕ в это время присутствует уровень логической "1", на его выходе будет поддерживаться уровень логического "0", следовательно, на выходе элемента 32 ИЛИ сохранится уровень логического "0", то есть сигнала ошибки не будет. Если бы из-за какого-либо отказа в рассматриваемом интервале на выходах сумматора 1 код не был больше кода на конденсаторах RC=элементов 8.11, то на выходе "А>В" блока 3 сравнения чисел и, следовательно, на втором входе указанного элемента 28 ИЛИ-НЕ присутствовал бы уровень логического "0", что привело бы к появлению уровня логической "1" на выходе элемента 28 ИЛИ-НЕ и уровня логической "1" на выходе элемента 32 ИЛИ (поскольку на остальных входах последнего в это время присутствуют уровни логического "0"), то есть привело бы к формированию сигнала ошибки. После окончания каждого из указанных счетных импульсов коды на выходах сумматора 1 и на конденсаторах RC-элементов 8.11 совпадают, что приводит к восстановлению уровня логической "1" на выходе "А=В" блока 3 сравнения чисел, который поступает на вход 21 формирователя 5 сигнала ошибки и далее на вход элемента 29 ИЛИ-НЕ (см. фиг. 2) последнего. Это приводит, независимо от уровня сигнала на другом входе элемента 29 ИЛИ-НЕ, к появлению уровня логического "0" на его выходе, который не приводит к изменению уровня логического "0" на выходе элемента 32 ИЛИ, то есть не приводит к формированию сигнала ошибки. Если же после каждого из указанных счетных импульсов устройство из-за отказов (сбоев) не устанавливается в новое состояние, и коды на выходах сумматора 1 и на конденсаторах RC-элементов 8.11 не будут совпадать, то в интервале между счетными импульсами на выходе "А=В" блока 3 сравнения чисел уровень логической "1" не восстановится. Это приведет к появлению уровня логической "1" на выходе элемента 29 ИЛИ-НЕ (так как на другом его входе между счетными импульсами присутствует уровень логического "0") и появлению уровня логической "1" на выходе элемента 32 ИЛИ, то есть приведет к формированию сигнала ошибки.

При подаче шестнадцатого счетного импульса на выходах сумматора 1 устанавливается код (0000) нулевого состояния устройства, который меньше кода текущего состояния устройства (1111), имеющего на конденсаторах RC-элементов 8.11, а на выходе переноса на время длительности счетного импульса устанавливается уровень логической "1" сигнал переноса, который поступает на вход 23 формирователя 5 сигнала ошибки. При этом уровень логической "1" устанавливается на выходе "А<В" блока 3 сравнения чисел, который поступает на вход 22 формирователя 5 сигнала ошибки, на входах 20 и 21 которого в это время присутствуют уровни логического "0", на входе 24 уровень логической "1" (так как есть счетный импульс), на вход 25 также поступает (с небольшой задержкой относительно фронта счетного импульса) уровень логической "1" импульс опроса. В результате на выходе элемента 27 И-НЕ формирователя 5 сигнала ошибки (см. фиг. 2) появляется (на время длительности опросного импульса) уровень логического "0", который поступает на вход элемента 30 ИЛИ-НЕ. На другой вход элемента 30 ИЛИ-НЕ в это время присутствует уровень логической "1" (поступающий с выхода "А<В" блока 3 сравнения чисел), поэтому на его выходе будет поддерживаться уровень логического "0", который поступает на вход элемента 32 ИЛИ, но не приводит к смене уровня логического "0" на выходе последнего, то есть не приводит к формированию сигнала ошибки. Если бы при подаче шестнадцатого счетного импульса на выходах сумматора 1 из-за отказа (сбоя) устройства установился бы код равный или больше кода на конденсаторах RC-элементов 8.11, на выходе "А<В" блока 3 сравнения чисел установился бы уровень логического "0". Это в рассматриваемом интервале (см. фиг.6, интервал t4-t1) привело бы к появлению на выходе элемента 30 ИЛИ-НЕ формирователя 5 сигнала ошибки (см. фиг.2) уровня логической "1", который привел бы к появлению (на время длительности опросного импульса) на выходе элемента 32 ИЛИ уровня логической "1", то есть привело бы к формированию сигнала ошибки.

После окончания шестнадцатого счетного импульса, то есть в интервале между шестнадцатым и последующим счетным импульсами, элементы устройства, обеспечивающие его самоконтроль функционирования, работают так же, как и между первыми пятнадцатью счетными импульсами, о чем было изложено выше.

Контроль исправности шины 17 сброса и факта прохождения сигнала сброса в устройство и сброса последнего в исходное нулевое состояние осуществляется (при необходимости) путем подачи сигнала сброса, предварительно запустив устройство в режим счета. В этом случае на выходах мультиплексора 2 в течение сигнала сброса активно формируются, как было указано выше, уровни логического "0", на разрядных выходах сумматора 1 появляется код нулевого состояния устройства, который будет меньше кода, имеющегося в это время на конденсаторах RC-элементов 8.11 (при нахождении устройства в состояниях, соответствующих числам от 1 до 15). Очевидно, что в течение длительности сигнала сброса на выходе "А<В" блока 3 сравнения чисел будет уровень логической "1", на выходах "А=В" и "А>В" уровень логического "0", которые поступают на выходы 22, 21 и 20 соответственно формирователя 5 сигнала ошибки. На входах 24 и 25 данного формирователя в это время будет присутствовать уровень логического "0" (поскольку сигнал сброса поддерживает на выходе элемента 7 ИЛИ-НЕ уровень логического "0", независимо от того, есть счетной импульс или нет его), а на входе 23 уровень логического "0" (нет сигнала переноса на выходе переноса сумматора 1). В результате в течение сигнала сброса на обоих входах элемента 29 ИЛИ-НЕ формирователя 5 сигнала ошибки (см. фиг.2), будут присутствовать уровни логического "0", что приводит к появлению уровня логической "1" на выходах элементов 29 ИЛИ-НЕ и 32 ИЛИ, то есть формированию сигнала ошибки. После снятия сигнала сброса коды на разрядных выходах сумматора 1 и конденсаторах RC-элементов 8.11 совпадут, на выходе "А=В" блока 3 сравнения чисел восстановится уровень логической "1", что приведет к исчезновению сигнала ошибки на выходе формирователя 5 сигнала ошибки. Таким образом, факт появления сигнала ошибки на соответствующей выходной шине устройства при подаче сигнала сброса в процессе его работы и исчезновение этого сигнала ошибки после снятия сигнала сброса свидетельствует об исправности шины 17 сброса, поступлении сигнала сброса в устройство и сброса последнего в исходное состояние. В том, что устройство установилось в нулевое состояние и находится в нем, можно, при необходимости, убедиться повторно подав сигнал сброса. При этом сигнал ошибки не будет формироваться.

По сравнению с прототипом заявляемый объект обладает существенным положительным эффектом более высокой достоверностью результатов счета.

Повышение достоверности результатов счета импульсов заявляемым устройством достигнуто за счет обеспечения постоянного самоконтроля функционирования в процессе работы, начиная с момента включения питания, путем анализа состояний устройства в течение каждого счетного импульса, в интервале между счетными импульсами и при отсутствии последних.

На предприятии собран и испытан макет заявляемого устройства для счета импульсов в четырехразрядном варианте. Макет был реализован на базе микросхем серии 564. При этом сумматор 1 был выполнен на микросхеме 564 ИМ1, вход переноса которой был подключен к общей шине устройства. Мультиплексор 2 был выполнен на микросхеме 564 ЛС2, блок 3 сравнения чисел на микросхеме 564 ИП2, формирователь 4 опросного импульса на счетчике 564 ИЕ9 и элементе ИЛИ-НЕ микросхемы 564 ЛЕ5 по схеме фиг.4, формирователь 5 сигнала ошибки на элементах И-НЕ и ИЛИ-НЕ соответственно микросхем 564 ЛА7 и 564 ЛЕ5, элементы 6, 7 ИЛИ-НЕ на элементах ИЛИ-НЕ микросхемы 564 ЛЕ5. Формирователь 4 опросного импульса формировал одиночные импульсы с длительностью 5 мкс с задержкой 5.10 мкс относительно фронта счетного импульса, при этом период следования импульсов на тактовом входе его счетчика равнялся 5 мкс. RC-элементы 8.15 макета были выполнены на дискретных резисторах типа ОМЛТ и конденсаторах типа КМ-5а, при этом сопротивление резисторов было принято равным 100 кОм, емкость конденсаторов равной 360 пф, то есть постоянная времени RC-элементов 8.15 равнялась ≈75 мкс.

При испытаниях макета на его входную шину 16 сначала подавались импульсы с длительностью 50 мкс, затем с длительностью 100 мкс. В первом случае устройство сохраняло свое исходное нулевое состояние, а во втором случае четко запускалось и изменяло свои состояния по срезу счетных импульсов с формированием после подачи шестнадцати импульсов импульса переполнения. Способность устройства формировать сигнал ошибки при отказах элементов в процессе испытаний макета проверялась путем имитации различных отказов (обрыв, входа младшего разряда первого слагаемого сумматора 1, обрыв цепи питания мультиплексора 2 или сумматора 1, постоянный уровень логической "1" или логического "0" на выходах мультиплексора 2, отказы управляющих входов мультиплексора 2 и т.д.) при ручном и автоматическом режимах подачи счетных импульсов.

Испытания макета показали работоспособность заявляемого устройства для счета импульсов и его способность формировать сигнал ошибки при наличии отказов (сбоев), приводящих к изменению алгоритма его работы, и, таким образом, подтвердили достижение поставленной цепи.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТНОЕ УСТРОЙСТВО | 1991 |

|

SU1817645A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1574146A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1988 |

|

SU1572383A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1987 |

|

SU1464893A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| РЕКОНФИГУРИРУЕМЫЙ АСИНХРОННЫЙ СУММАТОР-УМНОЖИТЕЛЬ | 1999 |

|

RU2159464C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| Устройство для защиты электрооборудования от перегрева током | 1988 |

|

SU1541701A1 |

Изобретение относится к импульсной технике и может быть использовано отдельно или в составе различных цифровых устройств в условиях воздействия помех. Целью изобретения является повышение достоверности результатов отсчета, что достигается за счет обеспечения постоянного самоконтроля функционирования. Самоконтроль устройства осуществляется после включения питания постоянно как в исходном состоянии, так и в процессе счета импульсов. По сравнению с прототипом предложенное устройство для счета импульсов обладает существенным положительным эффектом - более высокой достоверностью результатов счета. 1 з.п. ф-лы, 6 ил.

НЕ соединен с выходом элемента НЕ, вход которого подключен к второму входу второго элемента И НЕ и к четвертому входу формирователя сигнала ошибки, выход первого элемента И НЕ соединен с первым входом первого элемента ИЛИ - НЕ, второй вход которого соединен с первым входом формирователя сигнала ошибки, первый и второй входы второго элемента ИЛИ НЕ соединены соответственно с вторым и пятым входами формирователя сигнала ошибки, первый вход третьего элемента ИЛИ НЕ соединен с выходом второго элемента И НЕ, второй вход с третьим входом формирователя сигнала ошибки, входы элемента ИЛИ соединены с выходами первого, второго и третьего элементов ИЛИ НЕ, а выход соединен с выходом формирователя сигнала ошибки.

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1987 |

|

SU1464893A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-04-30—Публикация

1989-12-29—Подача