Изобретение относится к вычислительной технике и может применяться в устройствах управления внешней памятью.

Целью изобретения является снижение аппаратурных затрат.

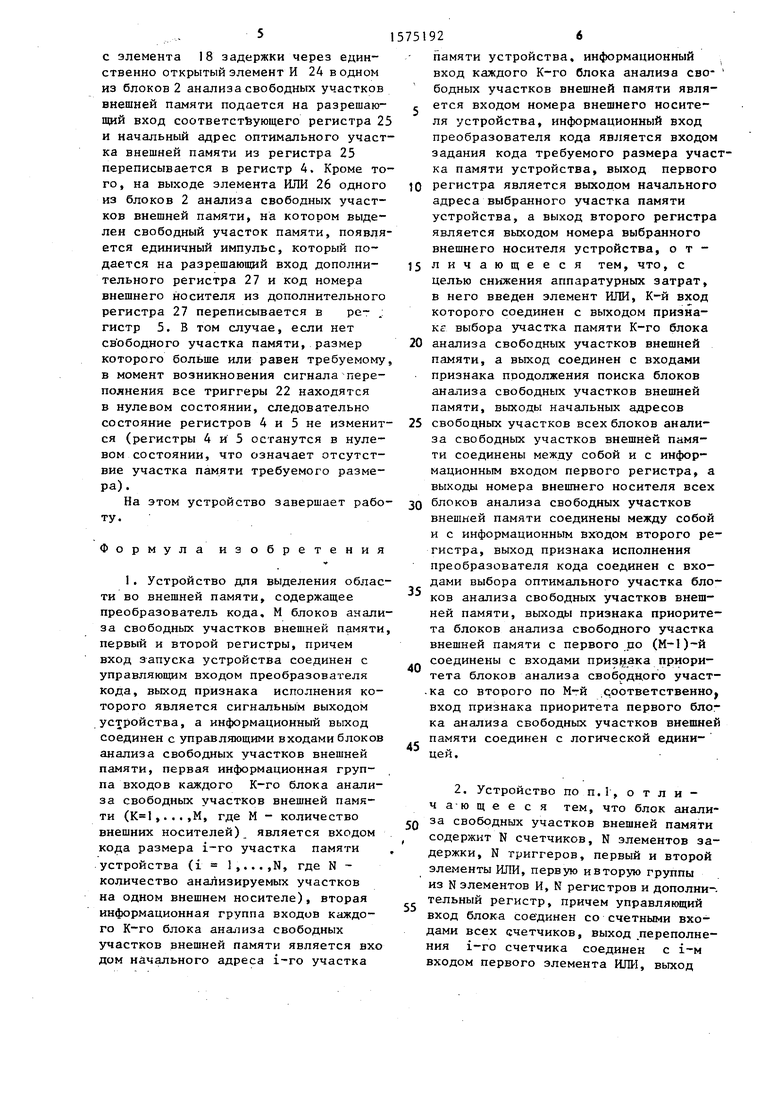

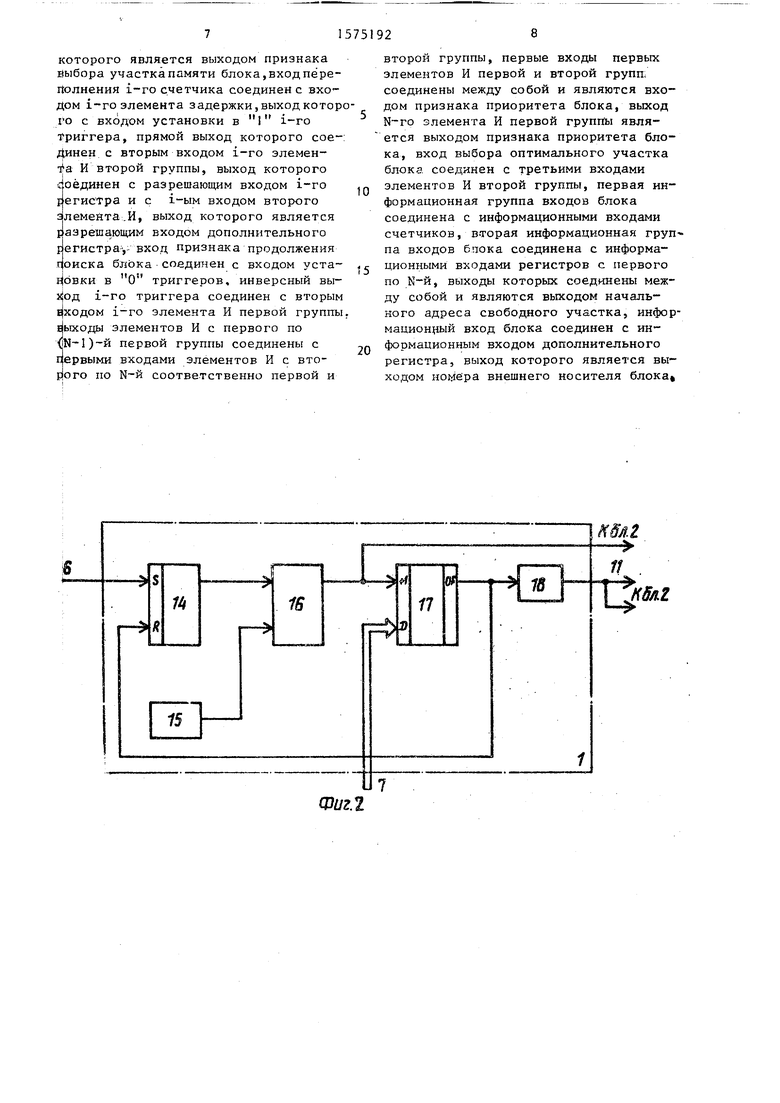

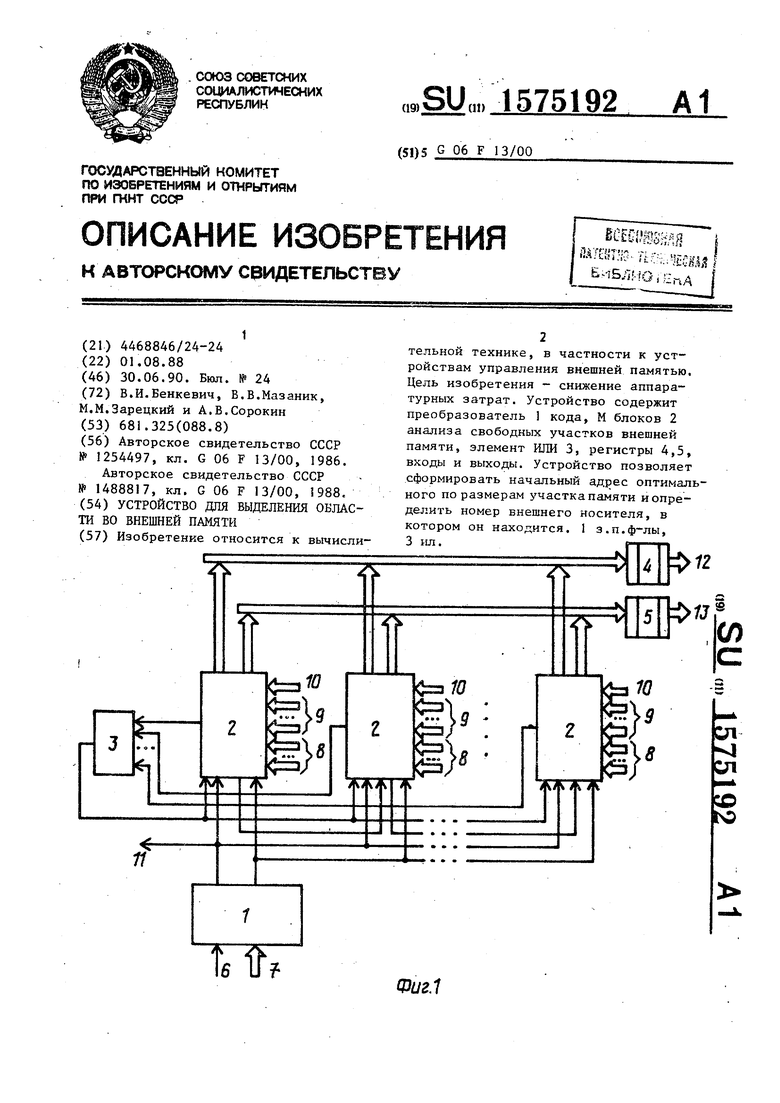

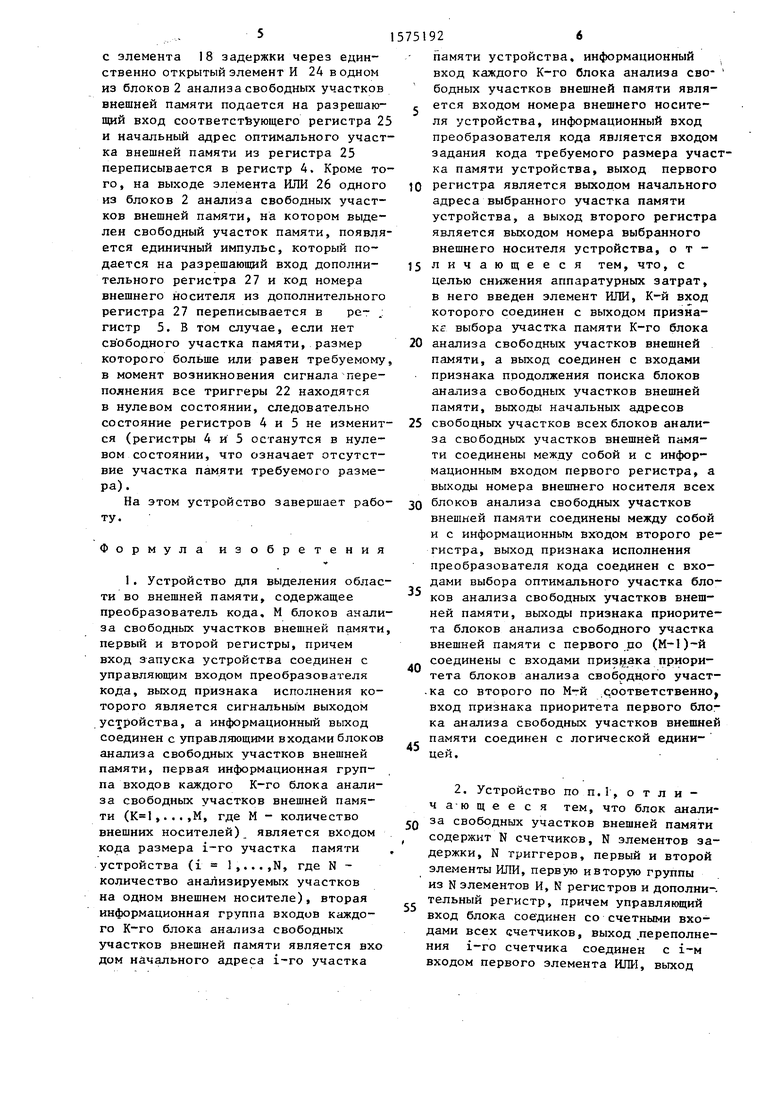

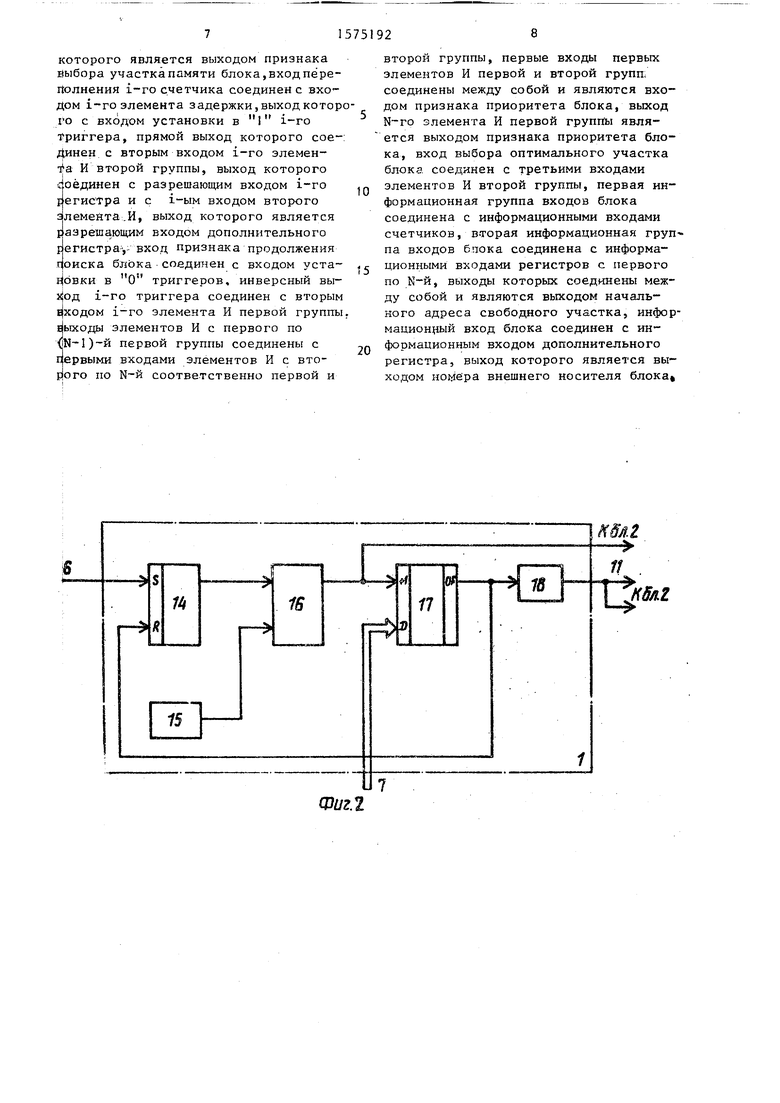

На фиг.1 изображена функциональная схема предлагаемого устройства; а фиг.2 - функциональная схема преобразователя кодов; на фиг.З - функциональная схема блока анализа свободных участков внешней памяти.

Устройство содержит преобразователь 1 кода, М блоков 2 анализа свободных участков внешней памяти, элемент ИЛИ 3, первый регистр 4, второй Регистр 5, вход 6 запуска, вход 7 задания кода требуемого размера участка памяти М групп входов 8 кода размера 1-го участка памяти, М групп входов 9 начального адреса 1-го учаска памяти, М входов 10 номера внешнего носителя, сигнальный выход 11, выход 12 начального адреса выбранного участка памяти, выход 13 номера выбранного внешнего носителя. Преобразователь 1 кода содержит триггер 14, генератор 15 импульсов, элемент И 16, счетчик 17 и элемент 18 задержки. Блок 2 анализа свободных участков внешней памяти содержит N счетчиков 19, N элементов 20 задержки, первый элемент ИЛИ 21, N триггеров 22t N элементов И 23 первой группы, N элементов И 24 второй группы, N регистров 25, второй элемент ИЛИ 26 и дополнительный регистр 27.

Устройство работает следующим образом.

В исходном состоянии все триггеры счетчики и регистры устройства обнулены (не показано). В счетчик 17 по входу 7 записывается код требуемого размера участка памяти на внешнем носителе. По входам 8 в счетчики 19 которого К-го блока 2 анализа свободных участков внешней памяти (К-1,... М,где М - число внешних носителей памяти) заносятся коды размеров свободных участков памяти, а в регистры 25 по входам 9 заносятся их начальные адреса, причем если i-й участок памяти занят (i t,2,...,N,rne N - число анализируемых участков на одном внешнем носителе), то в 1-й счетчик 19 и i-й регистр 25 заноси ся нулевой код (нули во все разряды) Код номера внешнего носителя заносится в дополнительный .регистр 27 по

т, т -.

10

f5

20

25

30

35

40

45

50

55

924

входу 10. Регистры 25 и дополнительный регистр 27 находятся в третьем состоянии (с большим входным сопротивлением) и не оказывают влияние на регистры 4 и 5. С приходом импульса запуска по входу 6 триггер 14 переходит в единичное состояние и импульсы с генератора импульсов через элемент И 16 поступают на счетные входы счетчика 17 и счетчиков 19 всех блоков 2 анализа свободных участков внешней памяти. Состояние всех счетчиков с каждым импульсом увеличивается на единицу.

Чем больше код размера свободного участка памяти в одном из счетчиков 19, тем раньше возникает сигнал переполнения на соответствующем счетчике, При возникновении сигнала переполнения на одном из счетчиков все триггеры 22 через элементы ИЛИ 21 и 3 обнуляются и через время t{ , определяемое элементом 20 задержки, соответствующий счетчику 19 триггер 22 переводится в единичное состояние. Если к этому моменту времени сигнал переполнения счетчика 17 не поступил, то перевод триггера 22 в единичное состояние означает, что обнаружен участок памяти, размер которого больше требуемого Если с приходом очередного импульса с генератора 15 импульсов ни на одном из счетчиков сигнал переполнения не возникает, то состояние триггером 22 не изменяется .

При появлении сигнала переполнения на счетчике 17 триггер 14 переводится в нулевое состояние и генератор 15 импульсов отключается. Через время 1, определяемое элементом 18 задержки, на сигнальном выходе 11 устройств появляется сигнал Готовность устройства. К этому моменту времени один или несколько триггеров 22 находятся в единичном состоянии (если имелся участок памяти размером больше, либо равный требуемому) . В общем случае может быть несколько участков памяти одинаковой длины, что обуславливает единичное состояние нескольких триггеров 22.

Группы элементов И 23 и 24 всех блоков 2 анализа свободных участков внешней памяти представляют собой схему приоритета. В том случае, если два и более триггеров 22 находятся в единичном состоянии, то лишь один элемент И 24 будет открыт. Импульс

с элемента 18 задержки через единственно открытый элемент И 24 в одном из блоков 2 анализа свободных участков внешней памяти подается на разрешающий вход соответствующего регистра 25 и начальный адрес оптимального участка внешней памяти из регистра 25 переписывается в регистр 4, Кроме того, на выходе элемента ИЛИ 26 одного из блоков 2 анализа свободных участков внешней памяти, на котором выделен свободный участок памяти, появляется единичный импульс, который подается на разрешающий вход дополнительного регистра 27 и код номера внешнего носителя из дополнительного регистра 27 переписывается в регистр 5. В том случае, если нет свободного участка памяти, размер которого больше или равен требуемому в момент возникновения сигнала переполнения все триггеры 22 находятся в нулевом состоянии, следовательно состояние регистров 4 и 5 не изменится (регистры 4 и 5 останутся в нулевом состоянии, что означает отсутствие участка памяти требуемого размера) .

На этом устройство завершает работу.

Формула изобретения

1. Устройство для выделения области во внешней памяти, содержащее преобразователь кода, М блоков анализа свободных участков внешней памяти первый и второй регистры, причем вход запуска устройства соединен с управляющим входом преобразователя кода, выход признака исполнения которого является сигнальным выходом устройства, а информационный выход соединен с управляющими входами блоков анализа свободных участков внешней памяти, первая информационная группа входов каждого К-го блока анализа свободных участков внешней памяти (,...,М, где М - количество внешних носителей) является входом кода размера 1-го участка памяти устройства (i 1,...,N, где N - количество анализируемых участков на одном внешнем носителе), вторая информационная группа входов каждого К-го блока анализа свободных участков внешней памяти является вхо дом начального адреса 1-го участка

.

10

15

20

25

30

35

40

45

50

55

926

памяти устройства, информационный вход каждого К-го блока анализа сво- бодных участков внешней памяти является входом номера внешнего носителя устройства, информационный вход преобразователя кода является входом задания кода требуемого размера участка памяти устройства, выход первого регистра является выходом начального адреса выбранного участка памяти устройства, а выход второго регистра является выходом номера выбранного внешнего носителя устройства, отличающееся тем, что, с целью снижения аппаратурных затрат, в него введен элемент ИЛИ, К-й вход которого соединен с выходом признаке выбора участка памяти К-го блока анализа свободных участков внешней памяти, а выход соединен с входами признака продолжения поиска блоков анализа свободных участков внешней памяти, выходы начальных адресов свободных участков всех блоков анализа свободных участков внешней памяти соединены между собой и с информационным входом первого регистра, а выходы номера внешнего носителя всех блоков анализа свободных участков внешней памяти соединены между собой и с информационным входом второго регистра, выход признака исполнения преобразователя кода соединен с входами выбора оптимального участка блоков анализа свободных участков внешней памяти, выходы признака приоритета блоков анализа свободного участка внешней памяти с первого по (М-1)-й соединены с входами признака приоритета блоков анализа свободного участ- .ка со второго по М-й соответственно, вход признака приоритета первого блока анализа свободных участков внешней памяти соединен с логической единицей.

2. Устройство по п.отличающееся тем, что блок анализа свободных участков внешней памяти содержит N счетчиков, N элементов задержки, N триггеров, первый и второй элементы ИЛИ, первую и вторую группы из N элементов И,N регистров и дополнительный регистр, причем управляющий вход блока соединен со счетными входами всех счетчиков, выход .переполнения i-ro счетчика соединен с i-м входом первого элемента ИЛИ, выход

которого является выходом признака выбора участкапамяти блока,входпёре- полнения 1-го счетчика соединено входом 1-го элемента задержки, выход которго с входом установки в 1 1-го Триггера, прямой выход которого соединен с вторым входом 1-го элемента И второй группы, выход которого соединен с разрешающим входом i-ro регистра и с i-ым входом второго элемента.И, выход которого является |аэ решающим входом дополнительного р егистра , вход признака продолжения цоиска блока соединен с входом установки в О триггеров, инверсный выход 1-го триггера соединен с вторым уходом 1-го элемента И первой группы выходы элементов И с первого по )-ft первой группы соединены с цервыми входами элементов И с второго по N-й соответственно первой и

3

0

второй группы, первые входы первых элементов И первой и второй групп, соединены между собой и являются входом признака приоритета блока, выход NTO элемента И первой rpynifti является выходом признака приоритета блока, вход выбора оптимального участка блока соединен с третьими входами элементов И второй группы, первая информационная группа входов блока соединена с информационными входами счетчиков, вторая информационная группа входов бпока соединена с информационными входами регистров с первого по N-й, выходы которых соединены между собой и являются выходом начального адреса свободного участка, информационный вход блока соединен с информационным входом дополнительного регистра, выход которого является выходом номера внешнего носителя блока

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распознавания объектов | 1986 |

|

SU1405080A1 |

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| УСТРОЙСТВО ВЫБОРА ОПТИМАЛЬНОГО МАРШРУТА МАНЕВРА | 1992 |

|

RU2045773C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления внешней памятью. Цель изобретения - снижение аппаратурных затрат. Устройство содержит преобразователь 1 кода, М блоков 2, анализа свободных участков внешней памяти, элемент ИЛИ 3, регистры 4, 5, входы и выходы. Устройство позволяет сформировать начальный адрес оптимального по размерам участка памяти и определить номер внешнего носителя, в котором он находится. 1 з.п. ф-лы, 3 ил.

/4

16

Фиг.2

П

№

18

11

Ј5лг

| Устройство для выделения области во внешней памяти | 1985 |

|

SU1254497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1488817, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-08-01—Подача