Изобретение относится к вычислительной технике и может быть использовано для построения мультипропессорных вычислительных систем.

Цель изобретения - повышение пропускной способности устройства.

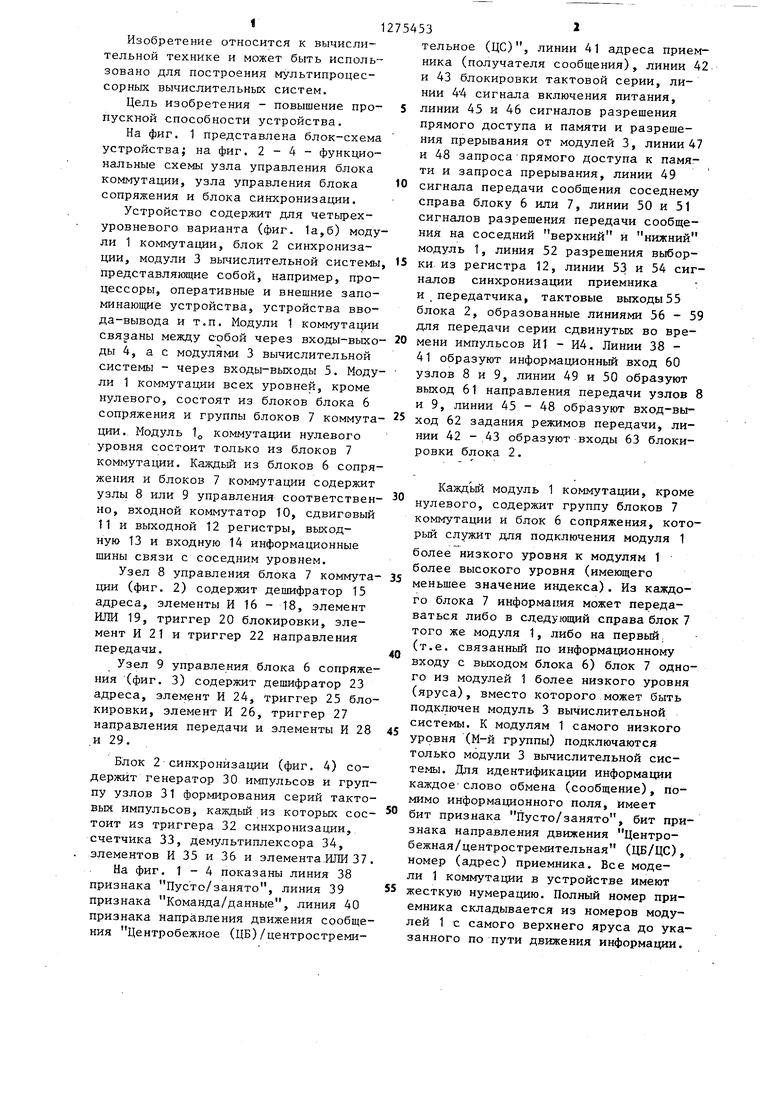

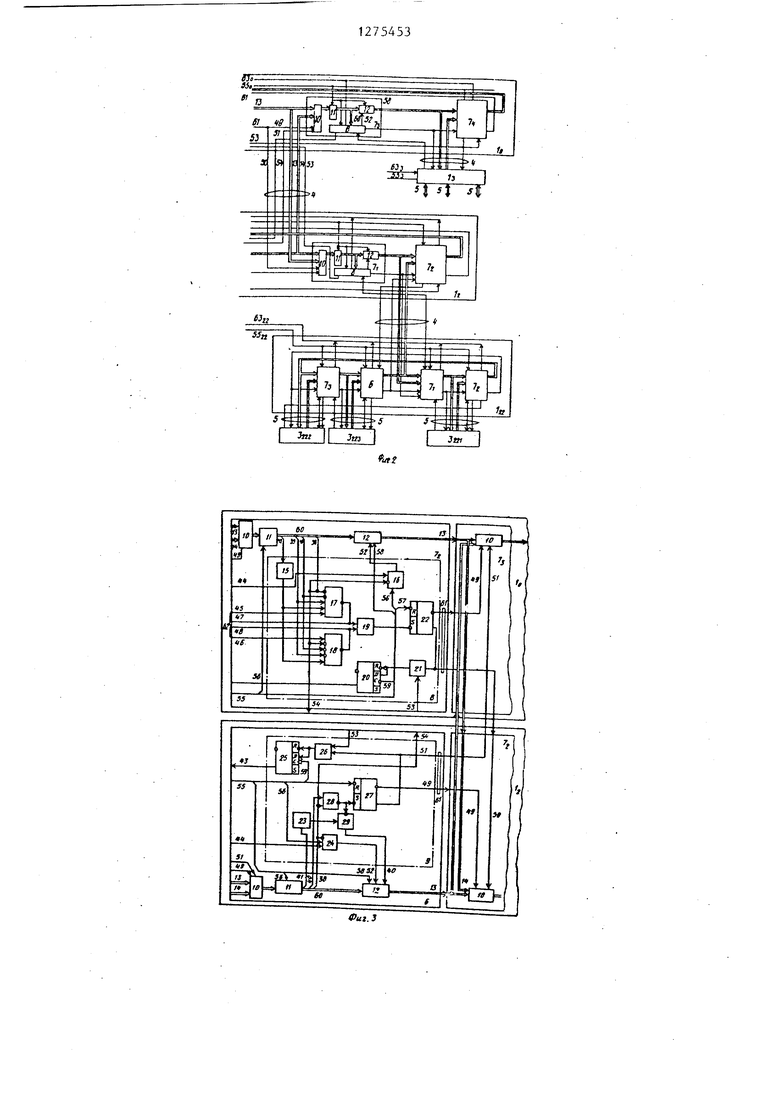

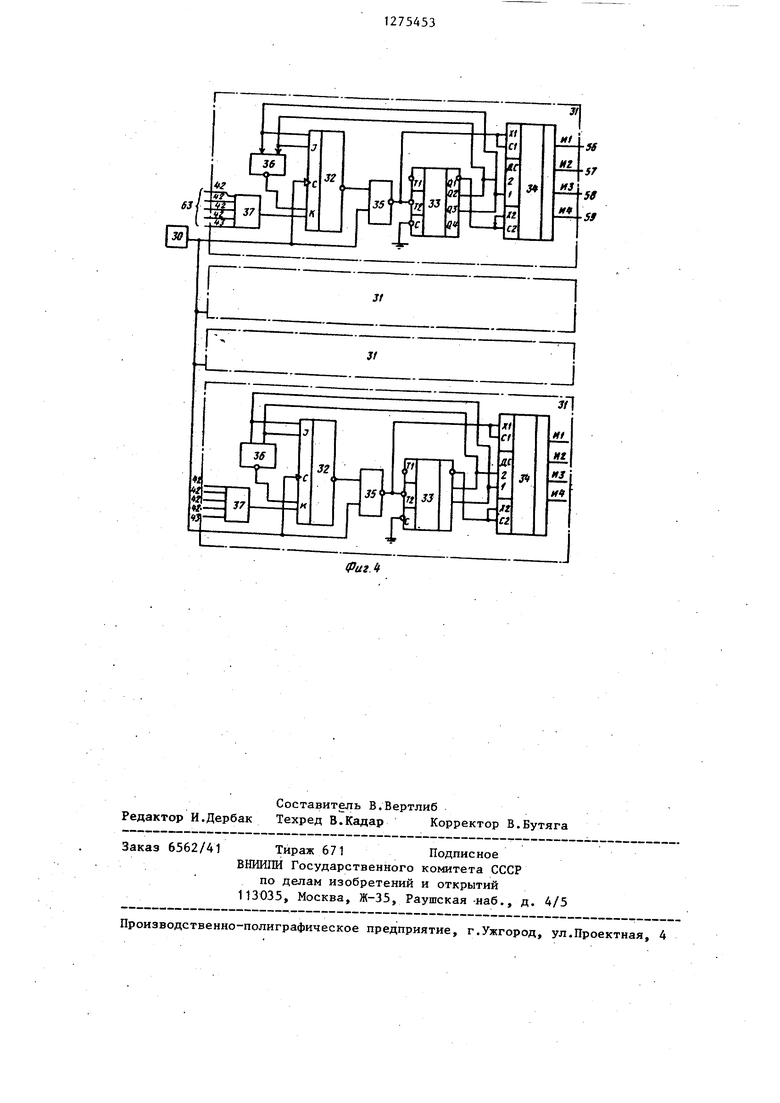

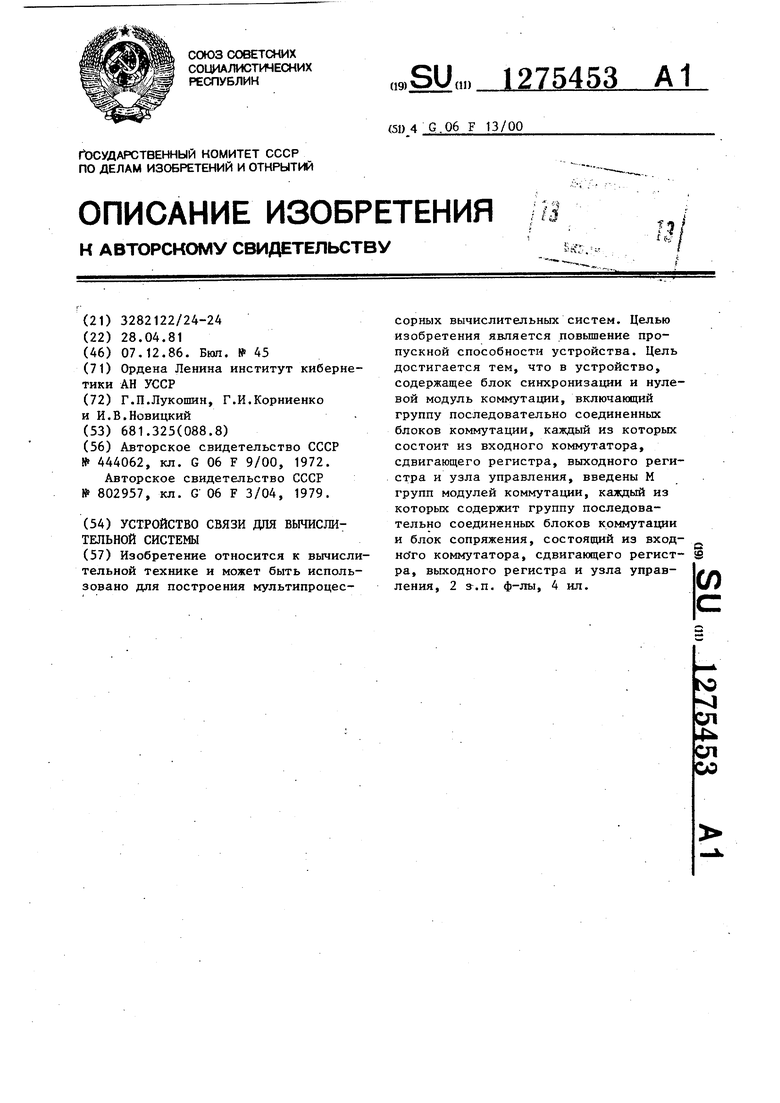

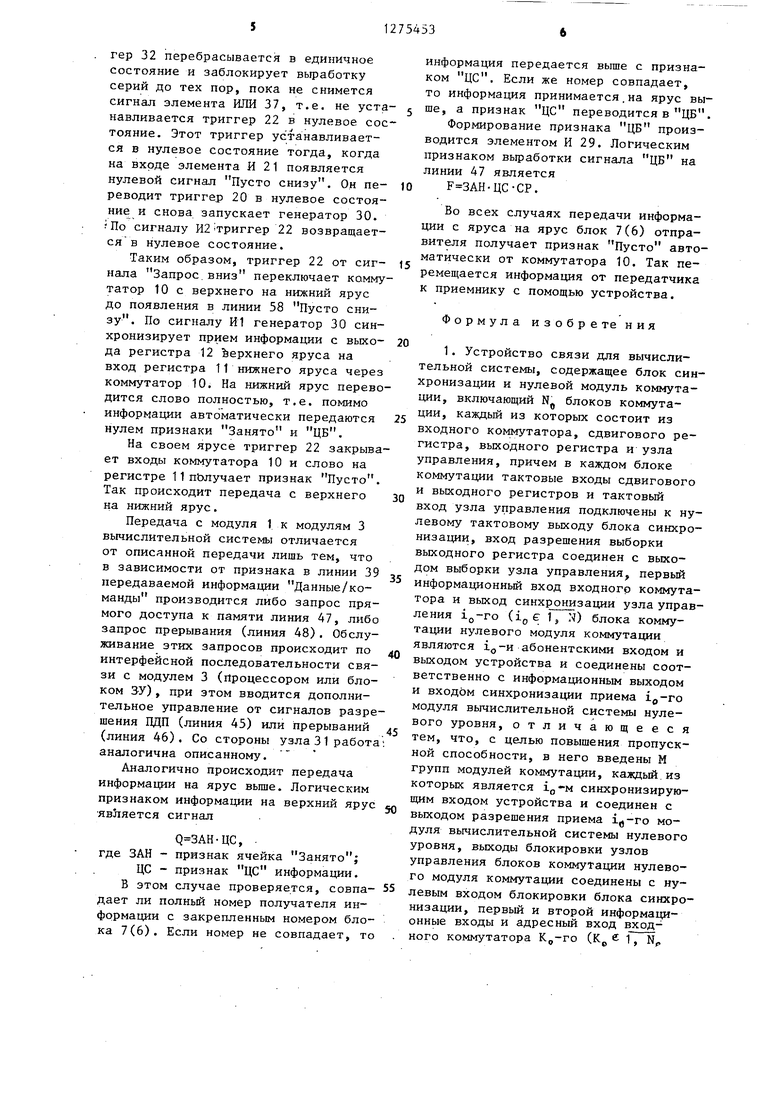

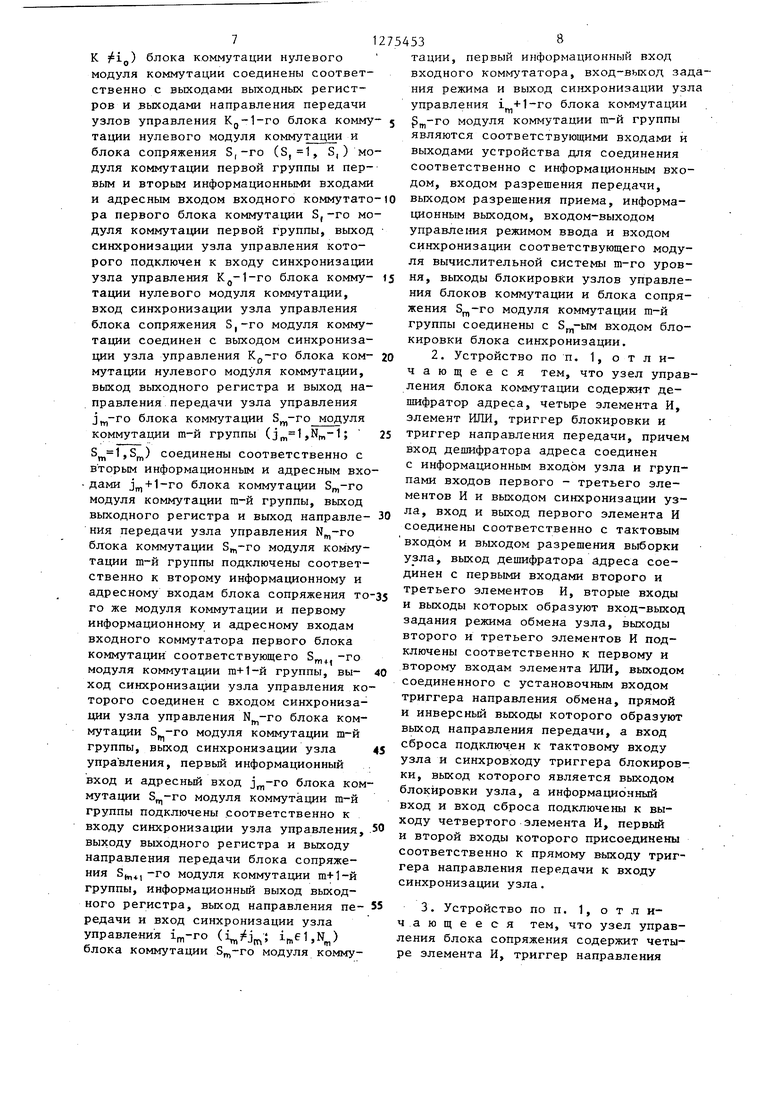

На фиг, 1 представлена блок-схема устройстваi на фиг. 2 - 4 - функциональные схемы узла управления блока коммутации, узла управления блока сопряжения и блока синхронизации.

Устройство содержит для четырехуровневого варианта (фиг. 1а,б) модули 1 коммутации, блок 2 синхронизации, модули 3 вычислительной системы, представляющие собой, например, процессоры, оперативные и внешние запоминающие устройства, устройства ввода-вывода и т.п. Модули 1 коммутации связаны между собой через входы-выходы 4, ас модулями 3 вычислительной системы - через входы-выходы 5. Модули 1 коммутации всех уровней, кроме нулевого, состоят из блоков блока 6 сопряжения и группы блоков 7 коммутации. Модуль 1о коммутации нул.евого уровня состоит только из блоков 7 коммутации. Каждьш из блоков 6 сопряжения и блоков 7 коммутации содержит узлы 8 или 9 управления соответственно, входной коммутатор 10, сдвиговый 11 и выходной 12 регистры, выходную 13 и входную 14 информационные шины связи с соседним уровнем.

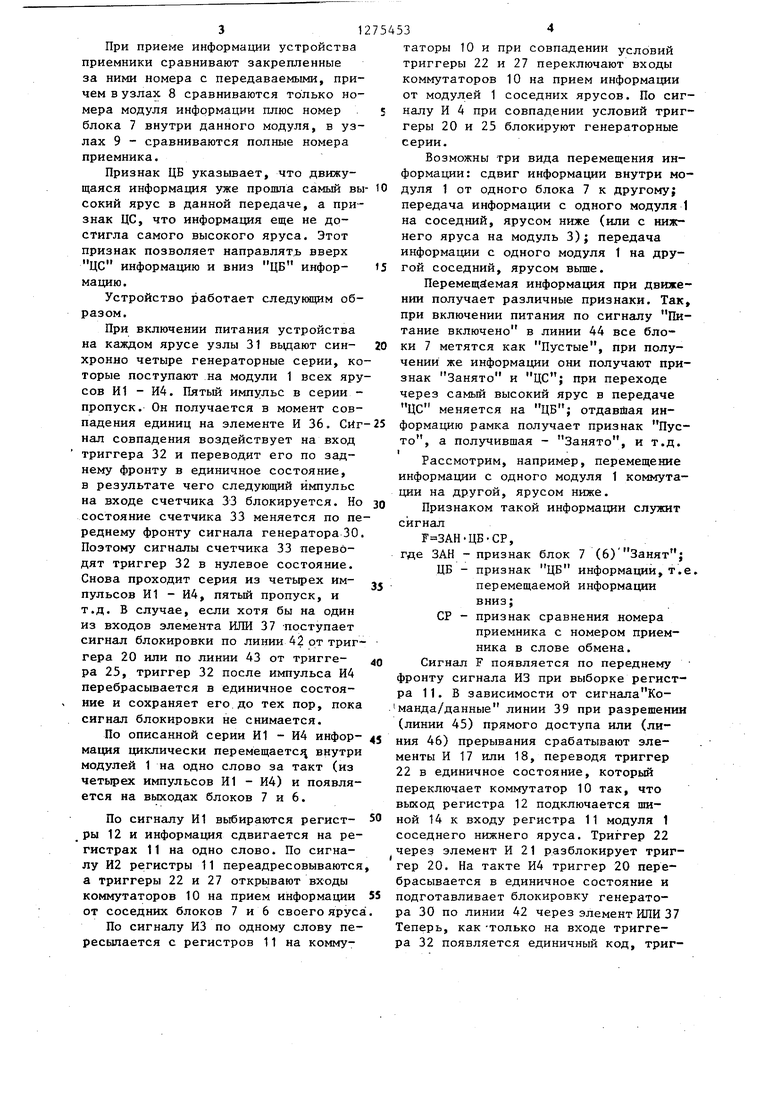

Узел 8 управления блока 7 коммутации (фиг, 2) содержит дешифратор 15 адреса, элементы И 16 - 18, элемент ИЛИ 19, триггер 20 блокировки, элемент И 21 и триггер 22 направления передачи.

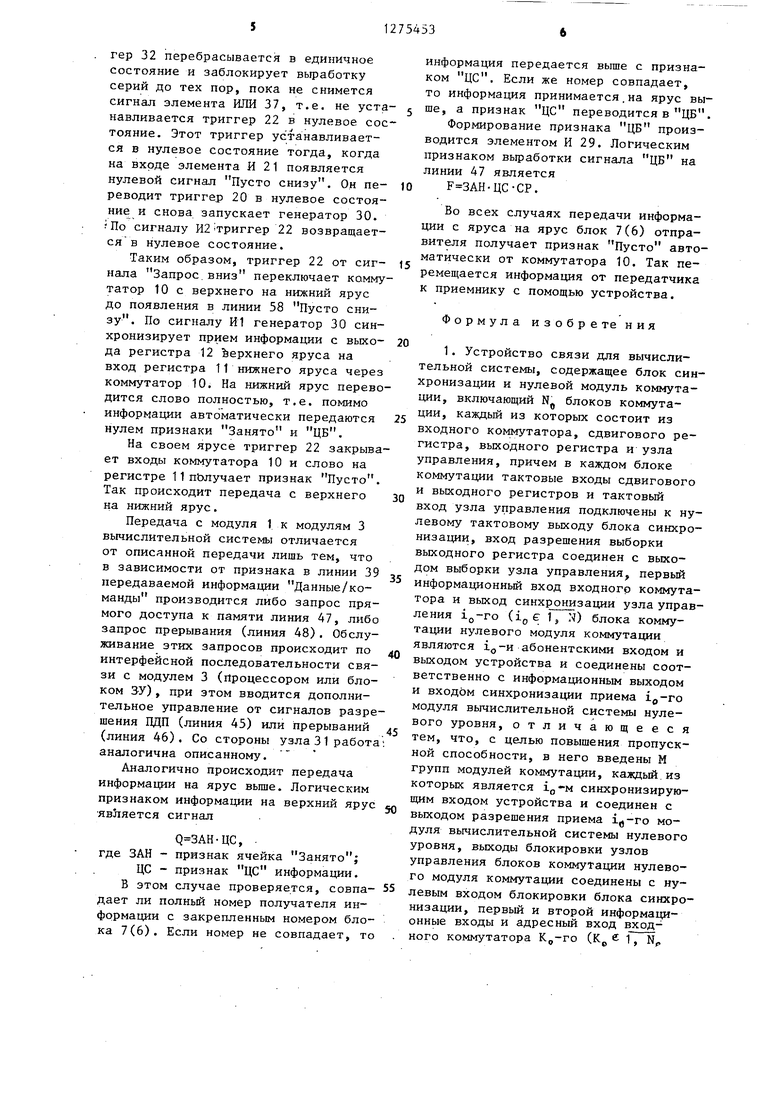

Узел 9 управления блока 6 сопряжения (фиг. 3) содержит дешифратор 23 адреса, элемент И 24, триггер 25 блокировки, элемент И 26, триггер 27 направления передачи и элементы И 28 .и 29.

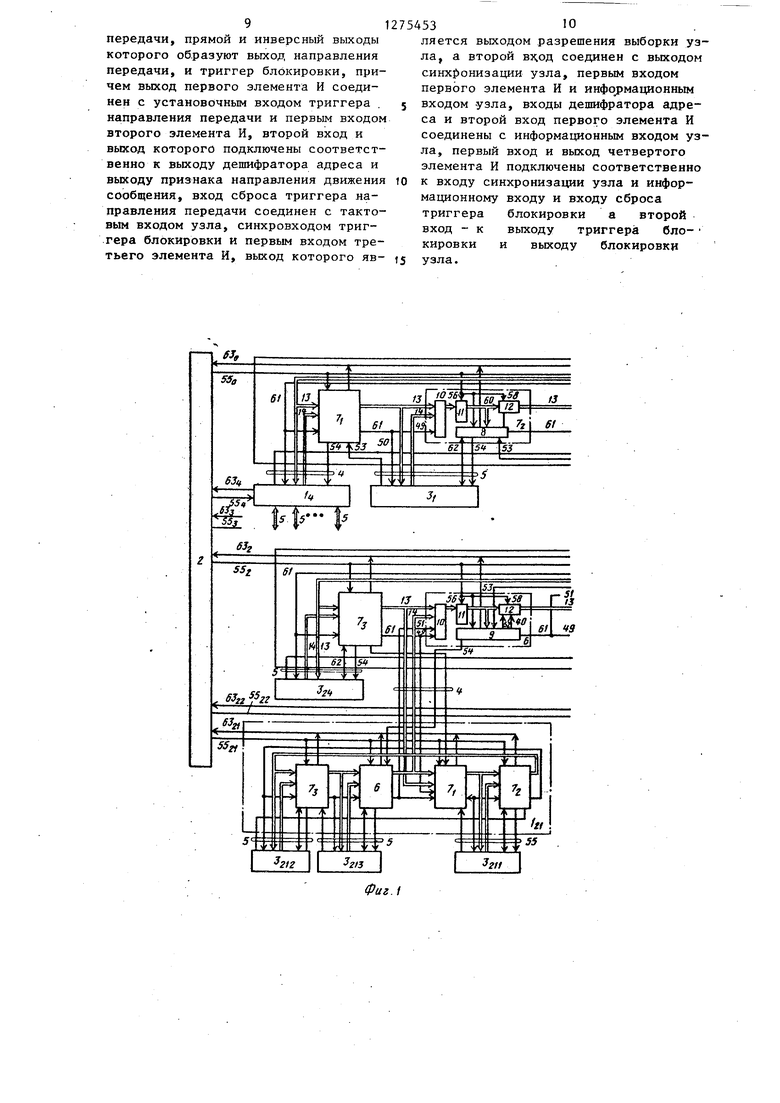

Блок 2 синхронизации (фиг. 4) содержит генератор 30 импульсов и группу узлов 31 формирования серий тактовьм импульсов, каждый из которых состоит из триггера 32 синхронизации, счетчика 33, демультиплексора 34, элементов И 35 и 36 и элемента.ИЛИ 37,

На фиг. 1 - 4 показаны линия 38 признака Пусто/занято, линия 39 признака Команда/данные, линия 40 признака направления движения сообщения Центробежное (ЦБ)/центростремительное (ЦС), линии 41 адреса приемника (получателя сообщения), линии 42 и 43 блокировки тактовой серии, линии 44 сигнала включения питания,

линии 45 и 46 сигналов разрешения прямого доступа и памяти и разрешения прерывания от модулей 3, линии 47 и 48 запроса прямого доступа к памяти и запроса прерывания, линии 49

сигнала передачи сообщения соседнему справа блоку 6 или 7, линии 50 и 51 сигналов разрешения передачи сообщения на соседний верхний и нижний модуль 1, линия 52 разрешения выбор5 ки из регистра 12, линии 53 и 54 сигналов синхронизации приемника и передатчика, тактовые выходы 55 блока 2, образованные линиями 56 - 59 для передачи серии сдвинутых во вре0 мени импульсов И1 - И4. Линии 38 41 образуют информационный вход 60 узлов 8 и 9, линии 49 и 50 образуют выход 61 направления передачи узлов 8 и 9, линии 45 - 48 образуют вход-вы5 ход 62 задания режимов передачи, линии 42 - 43 образуют входы 63 блокировки блока 2.

Каждьй модуль 1 коммутации, кроме

0 нулевого, содержит группу блоков 7 коммутации и блок 6 сопряжения, которьй служит для подключения модуля 1

более низкого уровня к модулям 1 более высокого уровня (имеющего

меньшее значение индекса). Из каждого блока 7 информация может передаваться либо в следующий справа блок 7 того же модуля 1, либо на первый, (т.е. связанньй по информационному

0 входу с выходом блока 6) блок 7 одного из модулей 1 более низкого уровня (яруса), вместо которого может быть подключен модуль 3 вычислительной системы. К модулям 1 самого низкого уровня (М-й группы) подключаются только модули 3 вычислительной системы. Для идентификации информации каждое-слово обмена (сообщение), помимо информационного поля, имеет

бит признака Пусто/занято, бит признака направления движения Центробежная/центростремительная (ЦБ/ЦС), Номер (адрес) приемника. Все модели 1 коммутации в устройстве имеют

5 жесткую нумерацию. Полный номер приемника складывается из номеров модулей 1 с самого верхнего яруса до указанного по пути движения информации. При приеме информации устройства приемники сравнивают закрепленные за ними номера с передаваемыми, причем в узлах 8 сравниваются только номера модуля информации плюс номер . блока 7 внутри данного модуля, в узлах 9 - сравниваются полные номера приемника. Признак ЦБ указьшает, что движущаяся информация уже прошла самый вы сокий ярус в данной передаче, а признак ЦС, что информация еще не достигла самого высокого яруса. Этот признак позволяет направлять вверх ЦС информацию и вниз ЦБ информацию. Устройство работает следукшщм образом. При включении питания устройства на каждом ярусе узлы 31 выдают синхронно четыре генераторные серии, ко торые поступают на модули 1 всех яру сов И1 - И4. Пятый импульс в серии пропуск. Он получается в момент совпадения единиц на элементе И 36, Сиг нал совпадения воздействует на вход триггера 32 и переводит его по заднему фронту в единичное состояние, в результате чего следующий импульс на входе счетчика 33 блокируется. Но состояние счетчика 33 меняется по пе реднему фронту сигнала генератора 30 Поэтому сигналы счетчика 33 переводят триггер 32 в нулевое состояние. Снова проходит серия из четьфех импульсов И1 - И4, пятый пропуск, и т.д. В случае, если хотя бы на один из входов элемента ИЛИ 37 -поступает сигнал блокировки по линии 42 от триг гера 20 или по линии 43 от триггера 25, триггер 32 после импульса И4 перебрасывается в единичное состояние и сохраняет его до тех пор, пока сигнал блокировки не снимается. По описанной серии И1 - И4 информация циклически перемещается внутри модулей 1 на одно слово за такт (из четырех импульсов И1 - И4) и появляется на выходах блоков 7 и 6. По сигналу И1 выбираются регистры 12 и информация сдвигается на регистрах 11 на одно слово. По сигналу И2 регистры 11 переадресовываются а триггеры 22 и 27 открывают входы коммутаторов 10 на прием информации от соседних блоков 7 и 6 своего ярус По сигналу ИЗ по одному слову пересыпается с регистров 11 на коммутаторы 10 и при совпадении условий триггеры 22 и 27 переключают входы коммутаторов 10 на прием информации от модулей 1 соседних ярусов. По сигналу И 4 при совпадении условий триггеры 20 и 25 блокируют генераторные серии. Возможны три вида перемещения информации: сдвиг информации внутри модуля 1 от одного блока 7 к другому; передача информации с одного модуля 1 на соседний, ярусом ниже (или с нижнего яруса на модуль 3); передача информации с одного модуля 1 на другой соседний, ярусом вьше. Перемещаемая информация при движении получает различные признаки. Так, при включении питания по сигналу Питание включено в линии 44 все блоки 7 метятся как Пустые, при получении же информации они получают признак Занято и при переходе через самый высокий ярус в передаче ЦС меняется на отдавйая информацию рамка получает признак Пусто, а получившая - Занято, и т.д. I Рассмотрим, например, перемещение информации с одного модуля 1 коммутации на другой, ярусом ниже. Признаком такой информации служит сигнал Г ЗАНЦБСР, где ЗАН - признак блок 7 (6) Занят ; ЦБ - признак ЦБ информации, т.е. перемещаемой информации вниз; СР - признак сравнения номера приемника с номером приемника в слове обмена. Сигнал F появляется по переднему фронту сигнала ИЗ при выборке регистра 11. В зависимости от сигнала Команда/данные линии 39 при разрешении (линии 45) прямого доступа или (линия 46) прерывания срабатывают элементы И 17 или 18, переводя триггер 22 в единичное состояние, который переключает коммутатор 10 так, что выход регистра 12 подключается шиной 14 к входу регистра 11 модуля 1 соседнего нижнего яруса. Триггер 22 через элемент И 21 разблокирует триггер 20. На такте И4 триггер 20 перебрасывается в единичное состояние и подготавливает блокировку генератора 30 по линии 42 через элемент ИЛИ 37 Теперь, как -только на входе триггера 32 появляется единичный код, тригrep 32 перебрасывается в единичное состояние и заблокирует вьфаботку серий до тех пор, пока не снимется сигнал элемента ИЛИ 37, т.е. не устанавливается триггер 22 в нулевое состояние. Этот триггер устанавливается в нулевое состояние тогда, когда на входе элемента И 21 появляется нулевой сигнал Пусто снизу. Он переводит триггер 20 в нулевое состояние и снова запускает генератор 30. JПо сигналу И2триггер 22 возвращаетсяв нулевое состояние.

Таким образом, триггер 22 от сигнала Запрос.вниз переключает коммутатор 10 с верхнего на нижний ярус до появления в линии 58 Пусто снизу. По сигналу И1 генератор 30 синхронизирует прием информации с выхода регистра 12 верхнего яруса на вход регистра 11 нижнего яруса через коммутатор 10. На нижний ярус переводится слово полностью, т.е. помимо информации автоматически передаются нулем признаки Занято и ЦБ.

На своем ярусе триггер 22 закрывает входы коммутатора 10 и слово на регистре 11 пьлучает признак Пусто. Так происходит передача с верхнего на нижний ярус.

Передача с модуля 1 к модулям 3 вычислительной системы отличается от описанной передачи лишь тем, что в зависимости от признака в линии 39 передаваемой информации Данные/команды производится либо запрос прямого доступа к памяти линия 47, либо запрос прерывания (линия 48). Обслуживание этих запросов происходит по интерфейсной последовательности связи с модулем 3 (процессором или блоком ЗУ), при этом вводится дополнительное управление от сигналов разрешения ПДП (линия 45) или прерываний (линия 46). Со стороны узла 31 работа аналогична описанному.

Аналогично происходит передача информации на ярус выше. Логическим признаком информации на верхний ярус является сигнал

Q 3AH-4C,

где ЗАН - признак ячейка Занято ; ЦС - признак ЦС информации. В этом случае проверяется, совпадает ли полньй номер получателя информации с закрепленным номером блока 7(6). Если номер не совпадает, то

информация передается выше с признаком ЦС. Если же номер совпадает, то информация принимается.на ярус выше, а признак ЦС переводится

Формирование признака ЦБ производится элементом И 29. Логическим признаком вьфаботки сигнала ЦБ на линии 47 является

Р ЗАН-ЦС-СР.

Во всех случаях передачи информации с яруса на ярус блок 7(6) отправителя получает признак Пусто автоматически от коммутатора 10. Так перемещается информация от передатчика к приемнику с помощью устройства.

Формула изобрете ния

1. Устройство связи для вычислительной системы, содержащее блок синхронизации и нулевой модуль коммутации, включающий блоков коммутации, каждьш из которых состоит из входного коммутатора, сдвигового регистра, выходного регистра и узла управления, причем в каждом блоке коммутации тактовые входы сдвигового и выходного регистров и тактовый вход узла управления подключены к нулевому тактовому выходу блока синхронизации:, вход разрешения выборки выходного регистра соединен с выходом выборки узла управления, первьй информационньй вход входного коммутатора и выход синхрюнизации узла управления 1ц-го (if, 1} N) блока коммутации нулевого модуля коммутации являются 1д-и абонентскими входом и выходом устройства и соединены соответственно с информационным выходом и входом синхронизации приема модуля вычислительной системы нулевого уровня, отличающееся тем, что, с целью повышения пропускной способности, в него введены М групп модулей коммутации, каждый.из которых является IQ-M синхронизирующим входом устройства и соединен с выходом разрешения приема модуля вычислительной системы нулевого уровня, выходы блокировки узлов управления блоков коммутации нулевого модуля коммутации соединены с нулевым входом блокировки блока синхронизации, первый и второй информационные входы и адресный вход входного коммутатора (К и: i N к ig} блока коммутации нулевого модуля коммутации соединены соответственно с выходами выходных регистров и выходами направления передачи узлов управления Кд-1-го блока комму тации нулевого модуля коммутации и блока сопряжения S|-ro (S,1, S,) мо дуля коммутации первой группы и первым и вторым информационными входами и адресным входом входного коммутато ра первого блока коммутации S,-го мо дуля коммутации первой группы, выход синхронизации узла управления которого подключен к входу синхронизации узла управления К j-1-го блока коммутации нулевого модуля коммутации, вход синхронизации узла управления блока сопряжения S,-ro модуля коммутации соединен с выходом синхронизации узла управления блока коммутации нулевого модуля коммутации, выход выходного регистра и выход направления передачи узла управления блока коммутации модуля коммутации т-й группы (Jm-1, ,Sj) соединены соответственно с вторым информационным и адресным вхо дами j +1-го блока коммутации модуля коммутации га-й группы, выход выходного регистра и выход направления передачи узла управления блока коммутации 5„-го модуля коммутации т-й группы подключены соответственно к второму информационному и адресному входам блока сопряжения то го же модуля коммутации и первому информационному и адресному входам входного коммутатора первого блока коммутации соответствующего S -го модуля коммутации m+1-й группы, выход синхронизации узла управления ко торого соединен с входом синхронизации узла управления блока коммутации S -го модуля коммутации т-й группы, выход синхронизации узла управления, первый информационный вход и адресный вход блока ком мутации модуля коммутации т-й группы подключены соответственно к входу синхронизации узла управления, выходу выходного регистра и выходу направления передачи блока сопряжения S, -го модуля коммутации m+1-й группы, информационный выход выходного регистра, выход направления передачи и вход синхронизации узла управления ( in,e1,N) блока коммутации модуля комму53тации, первый информационный вход входного коммутатора, вход-выход задания режима и выход синхронизации узла управления in +1-го блока коммутации . „-го модуля коммутации т-й группы являются соответствующими входами и выходами устройства для соединения соответственно с информационным входом, входом разрешения передачи, выходом разрешения приема, информационным выходом, входом-выходом управле1й1Я режимом ввода и входом синхронизации соответствующего модуля вычислительной системы т-го уровня, выходы блокировки узлов управления блоков коммутации и блока сопряжения модуля коммутации т-й группы соединены с входом блокировки блока синхронизации. 2. Устройство по п, 1, о т л ичающееся тем, что узел управления блока коммутации содержит дешифратор адреса, четыре элемента И, элемент ИЛИ, триггер блокировки и триггер направления передачи, причем вход дешифратора адреса соединен с информационным входом узла и группами входов первого - третьего элементов И и выходом синхронизации узсоединены соответственно с тактовым входом и выходом разрешения выборки узла, выход дешифратора адреса соединен с первыми входами второго и третьего элементов И, вторые входы и выходы которых образуют вход-выход задания режима обмена узла, выходы второго и третьего элементов И подключены соответственно к первому и второму входам элемента ИЛИ, выходом соединенного с установочным входом триггера направления обмена, прямой и инверсный выходы которого образуют выход направления передачи, а вход сброса подключен к тактовому входу узла и синхровходу триггера блокировки, выход которого является выходом блокировки узла, а информационный вход и вход сброса подключены к выходу четвертого элемента И, первый и второй входы которого присоединены соответственно к прямому выходу триггера направления передачи к входу синхронизации узла. 3. Устройство по п. 1, отличающееся тем, что узел управления блока сопряжения содержит четыре элемента И, триггер направления

передачи, прямой и инверсный выходы которого образуют выход, направления передачи, и триггер блокировки, причем выход первого элемента И соединен с установочным входом триггера . направления передачи и первьм входом второго элемента И, второй вход и выход которого подключены соответственно к выходу дешифратора адреса и выходу признака направления движения сообщения, вход сброса триггера направления передачи соединен с тактовым входом узла, синхровходом триг.гера блокировки и первым входом третьего элемента И, выход которого является выходом разрешения выборки узла, а второй вкод соединен с выходом синхронизации узла, первым входом первого элемента И и информационным входом узла, входы дешифратора адреса и второй вход первого элемента И соединены с информационным входом узла, первый вход и выход четвертого элемента И подключены соответственно к входу синхронизации узла и информационному входу и входу сброса триггера блокировки а второй вход - к выходу триггера бло- кировки и выходу блокировки узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Система коммутации вычислительных устройств,устройство коммутации связи и устройство сопряжения | 1984 |

|

SU1180915A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для сопряжения вычислительного модуля с магистралью | 1985 |

|

SU1325495A1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2116664C1 |

| МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА | 1996 |

|

RU2110831C1 |

| Устройство для сопряжения абонентов с каналом передачи данных | 1986 |

|

SU1357969A2 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения мультипроцессорных вычислительных систем. Целью изобретения является повьппение пропускной способности устройства. Цель достигается тем, что в устройство, содержащее блок синхронизации и нулевой модуль коммутации, включающий группу последовательно соединенных блоков коммутации, каждый из которых состоит из входного коммутатора, сдвигающего регистра, выходного регистра и узла управления, введены М групп модулей коммутации, каждый из которых содержит группу последовательно соединенных блоков коммутации и блок сопряжения, состоящий из входс S Hcfro коммутатора, сдвигающего регистра, выходного регистра и узла управ(Л ления, 2 З.П. ф-лы, 4 ил.

ztz

гп

ss

57

58 Si

| Устройство управления передачей информации | 1972 |

|

SU444062A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-07—Публикация

1981-04-28—Подача