Изобретение относится к вычислительной технике и может быть использовано, например, для функциональнотехнологического контроля при производстве полупроводниковых микросхем . памяти, а также для их входного конт роля.

Известно устройство для контроля оперативной памяти, содержащее схему пуска, регистр числа, счетчик адресов/ счетчик циклов, дешифратор циклов, дополнительные счетчики, схему сравнения, схему регистрации, схему останова и коммутатор разрядов 1.

Недостатками этого устройства является низкая производительность и ог-15 раниченная область применения.

Наиболее близким техническим решением к изобретению является устройство для контроля оперативной памяти, содержащее блок управления, 20 первый счетчик, регистр числа, подключенные к выходным шинам устройства, счетный триггер, формирователь импульсов, элемент И, второй счетчик, предназначенный, для подсчета 25 подциклов, третий счетчик-, группу элементов.И, сумматор по модулю два, основнйе и дополнительные коммутаторыС2.

Недостатком данного устройства ,является низкое быстродействие, так как время проверки оперативной памяти для этого устройства находится в квадратичной зависимости от количества адресов.

Целью изобретения явяляется повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для контроля оперативной памяти/ содержащее блок Q управления, регистр числа, счетный триггер, формирователь импульсов, счетчики, элемент И, основные и дополнительные коммутаторы, cyNOv aTOp по модулю два и группу элементов И, причем выходы первого счетчика и . регистра числа, выход элемента И и первый выход блока управления являются выходами устройства, второй выход блока управления соединен с прямым входом элемента И, первыми входами 50 счетного триггера и формирователя импульсов, выход которого подключен к инверсному входу элемента И, выход которого соединен с входом первого счётчика, выход последнего разряда 55 которого подключен к второму и третьему входу счетного триггера, выход которого соединен с вторым входом фор1 1ррвате ля импульсов, входом второгосчетчика и первым входом сум- ; (J матора помодулю два, второй вход которого подключен к выходу последнего разряда третьего счетчика, вход ; которого соединен со вторым выходом i блока управления/ третий выход котр- ЛЗ

рого подключен к входу синхронизации регистра числа, информационные входы которых соединены с выходами основных коммутаторов, первые и вторые.информационные входы которых подключены соответственно к выходу сумматора по модулю два и к выходши дополнительных коммутаторов, управлякядие входы которых соединены с выходами второго счетчика, а информационные входы - с выходами третьего счетчика, первые и вторые управляющие входы основных коммутаторов подключены соответственно к четвертому и пятому выходам блока управления, введены дешифратор строк дешифратор столбцов, элемент ИЛИ и элемент НЕ, выход и вход которого подключены соответственно к третьим и к четвертым информационным входам основных коммутаторов, выход элемента ИЛИ соединен с входом элемента НЕ, а, входы подключены к выходам элементов И группы, первые входы которых соединены с выходами дешифраторастрок, а вторые входы - с выходами дешифратора столбцов, входы которого подключены к одним из выходов трет, тьего счетчика, входы дешифратора строк соединены с одними из выходов первого счетчика, инверсный вход одного из элементов И группы подключен к выходу формирователя импульсов.

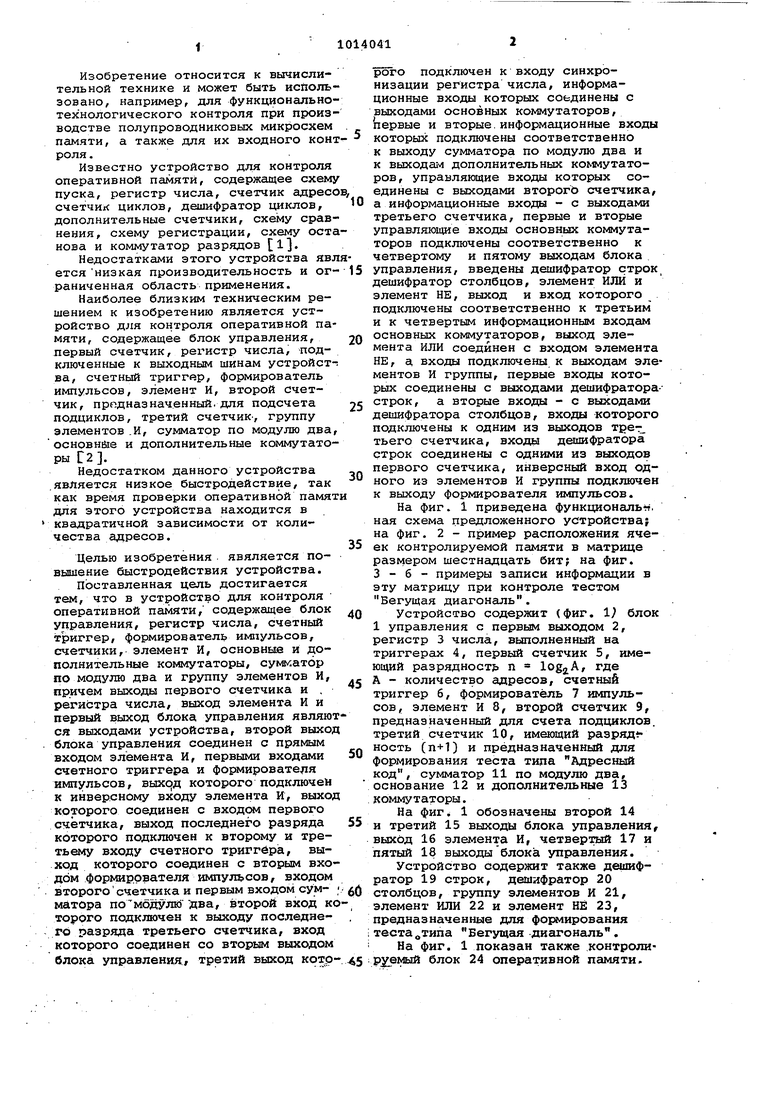

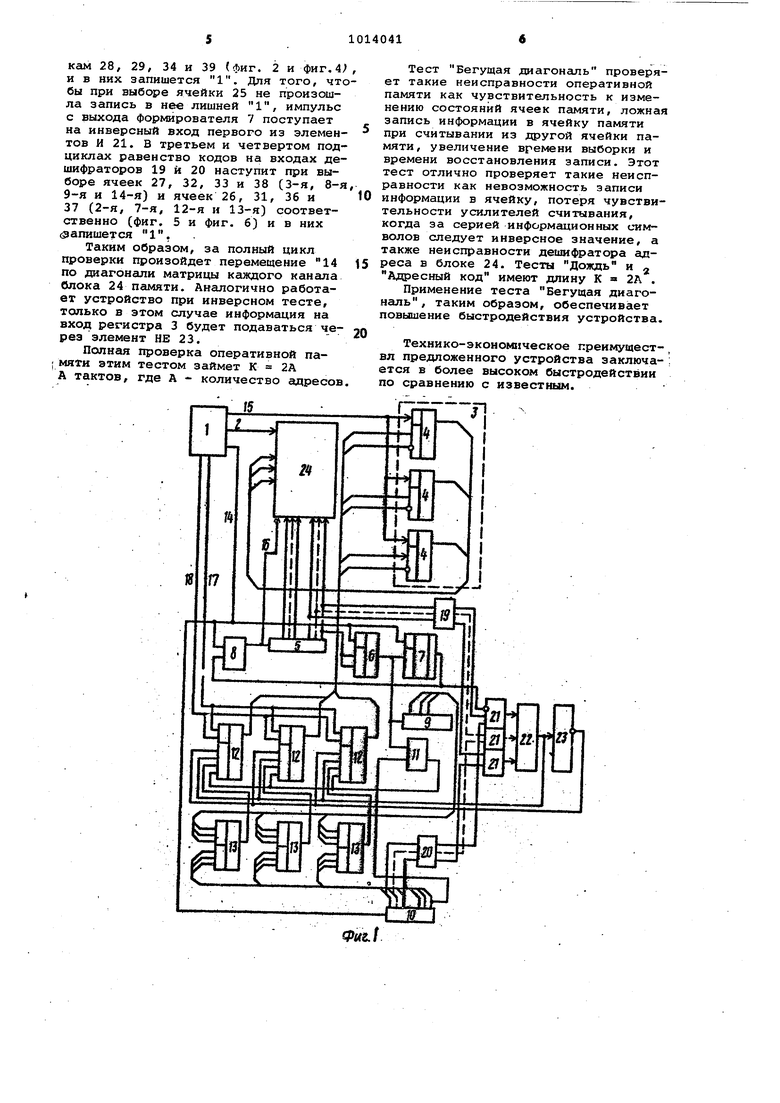

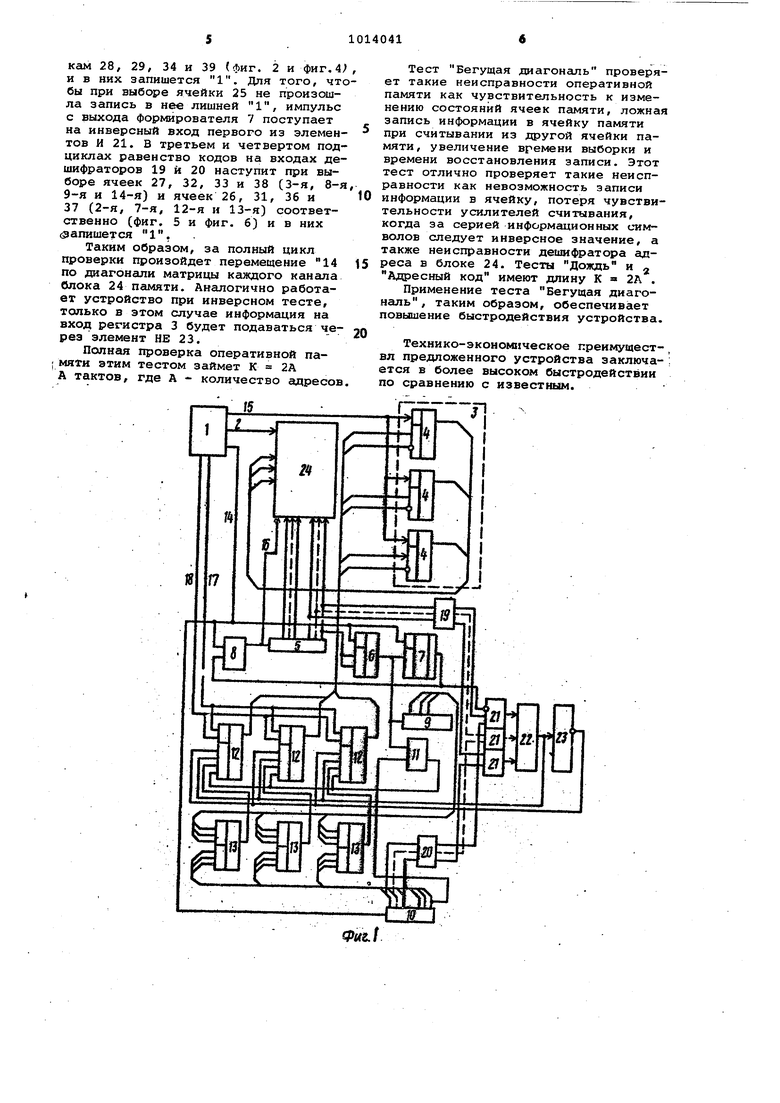

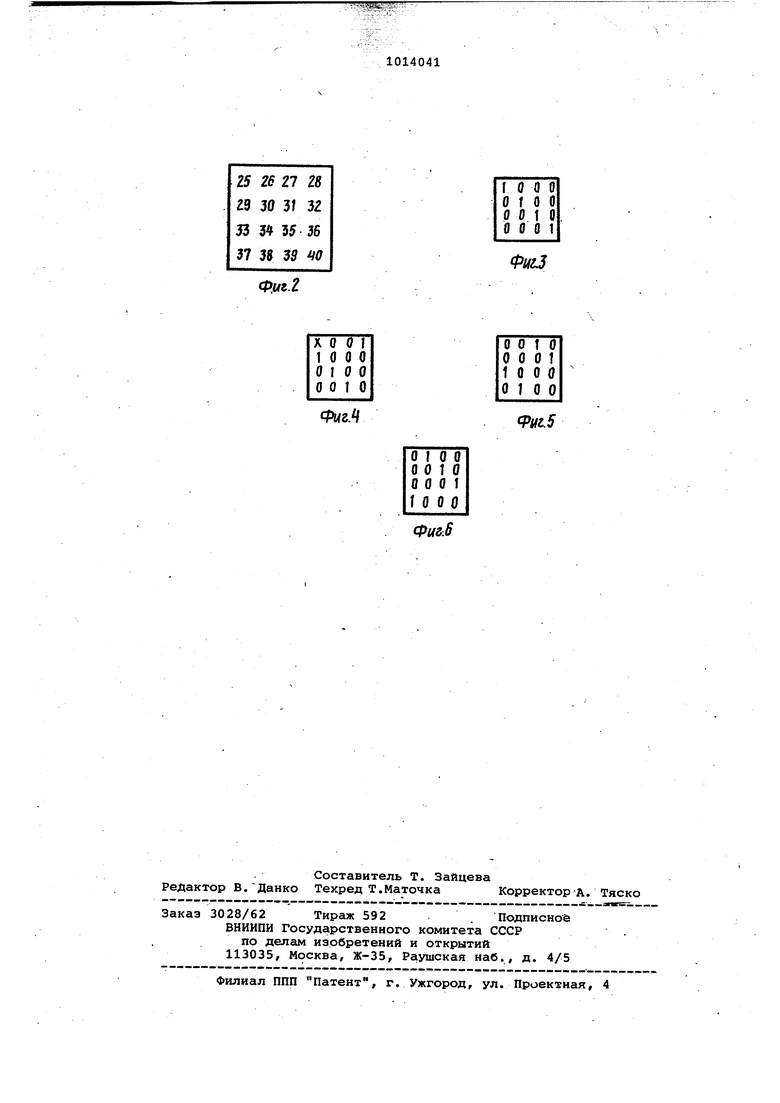

На фиг. 1 приведена функциональ т, ная схема предложенного устройства; на фиг. 2 - пример расположения ячеек контролируемой памяти в матрице размером шестнадцать бит; на фиг. 3 - б - примеры записи информации в эту матрицу при контроле тестом Бегущая диагональ.

Устройство содержит (фиг. 1 блок 1 управления с первым выходом 2, регистр 3 числа, выполненный на триггерах 4, первый счетчик 5, имеЮ1ЦИЙ разрядность п logj,A, где А - количество адресов, счетный триггер б, формирователь 7 импульсов, элемент И 8, второй счетчик 9, предназначенный для счета подциклов. третий счетчик 10, имеющий разряд ность (п+1) и предназначенный для формирования теста типа Адресный код, сумматор 11 по модулю два, основание 12 и дополнительные 13 коммутаторы.

На фиг. 1 обозначены второй 14 и третий 15 выходы блока управления, выход 16 элемента И, четвертый 17 и пятый 18 выходы блока управления.

Устройство содержит также дешифратор 19 строк, дешифратор 20 столбцов, группу элементов И 21, элемент ИЛИ 22 и элемент НЕ 23, предназначенные для формирования теста типа Бегущая диагональ.

На фиг. 1 показан также контролируемый блок 24 оперативной памяти. На фиг. 2 обозначены запоминающие ячейки 25-40 с первой по шестнадцатую в матрице .размером шестнещцать бит одного из каналов контролируемого блока оперативной памяти. Предложенное устройство работает следующим образом. , В режиме Дождь источником информации, запиоаваемой в регистр 3 (фиг. 1, является сумматор 11. При нажатии кнопки Пуск С на фиг. 1 условно не показана) в блоке 1 начинает вырабатываться тактовая последовательность импульсов. В первом подцикле счетчики 5 и 10 работают синхронно от одних и тех же тактов блока 1. При этом на входах сумматора 11 код одинаковый, а на его выходе низкий уровень напря жения, соответствующий записи кода О по всем адресам блока 24. : По окончании первого подцикла формирователем 7 вьщеляется задний фронт импульса с вь1хода триггера 6, и производится запрет (в элементе И 9) одного импульса продвижения в счетчик 5. в результате второй подцикл в счетчике 5 закончится на один так позже, чем в счетчике 10, и суммато1 11 зафиксирует неравнозначность в конце второго подцикла..Поэтому во втором подцикле во всех адресах памя ти блока 24, кроме последнего, будут ёгшисаны коды О, а в последнем - код 1. По окончании второго подцикла точно также произойдет запрет продвижения еще одного импульс в счетчик 5. Соответственно неравнозначность 3 афи1 сируется в двух последних адресах третьего подцикла, куда и будет записан код 1. Таким , блок 24, заполненный в пер вом подцикле еми нулями, заполняется в следующих псмцщклс1Х единицам т.е. происходит процесс набегания единиц характерный для теста Дождь Когда пройдут А поддиклов, коды на вка де сумматора 11 будут инверсными, и весь блок 24 будет заполнен единигцамя. В следующие А прдциклов точно также/ начиная с адреса, код единиц сменится кодсш нулей. Через 2А подциклов. закончится полный период теста. Рассмотрим ргаботу устройства при формировании теста типа Адресный код. В ЭТОМ случае управляющие импуль сы с выходов 17 и 18 блока 1 подклю чают к входам регистра 3 выходщ сче чика 10 через коммутаторы 13 и 12. Работа коммутаторов 12 аналогична их работе в режиме Дояадь эа исклю чением того, что источником информгщии является не сумматор 11, а (датчик 10, причем счетчики 10 и 9 ,1меют расхождение по частоте, равиое я-. А при этом код числа, записываемый в блок 24, будет меняться с каждым адресом, и каждый следующий подцикл в адресном коде будет начинаться с разных кодовых комбинаций, чем обеспечивается динамическое смещение информации по подциклам. Благодаря наличию коммутаторов 13, управляемых счетчиком 9, обеспечивается подключение к соответствующим разряг дам регистра числа 3 различных, разрядов счетчика 10 в различных подциклах. Этим достигается выравниванйе динами.ки работы разных разрядов.Рассмотрим работу устройства при формировании теста Бегущая диагональ , В этом случае управляющие импульсы с выходов 17 и 18 блока 1 подключают к входам регистра 3 .выходы элемента ИЛИ 22.для прямого теста Бегущая диагональ или выход эяемен- та НЕ 23 для инверсного теста. На выходе элемента ИЛИ 22 будет импульс 1 только в случае равенства кодов на входах дешифратора 19 и дешифратора 20. При всех остальных комбинациях на выходе элемента ИЛИ 22 будет импульс О. В исходном состоянии счетчики 5 и 10 обнулены. На первомвыходе дешифратора 19 устанавливается импульс 1, соответствующий первой выбранной строке. На первом выходе . дешифратора 20 тоже будет импульс 1, соответствующий первому выбранному столбцу. На первом из элементов И 21 произойдет логическое умножение, и через элемент ИЛИ 22, коммутаторы 12 и регистр 3 импульс 1 запишется в блок 24 и ячейку, расположенную на пересечении первой строки и первого столбца (фиг. 3 . При поступлении на вход счетчика 10 (фиг. 1J первого трактового импульса на первом выходе дешифратора 20 будет импульс О, и в последующие ячейки первой строки бУДУТ записаны О После прохождения всех ячеек первой строки сменится код на входе дешифратора 19, и импульс 1 появится на его втором выходе. Равенство кодов на входах обоих дешифраторов 19 и 20 наступит теперь при поступлении пятого счетного импульса (фиг. 6), и 1 запишется в шестую ячейку, находящуюся на пересечении второй строки и второго столбца (фиг. 3.). Так будет продолжаться до тех пор, пока 1 не запишется во все ячейки 25, 30, 35 и 40 (фиг. 2 Л После прохождения первого подцикла, как ив случае теста Дождь, произойдет запрет прохождения импульса в счетчик 5. При этом равенство кодов на входахдешифраторов, 19 и 20 будет выполняться при обращении к 28, 29, 34 и 39 (фиг. 2 и фиг,4, и в них запишется 1. Для того, чтобы при выборе ячейки 25 не произошла запись в не« лишней 1, импульс с выхода формирователя 7 поступает на инверсный вход первого из элементов И 21. В третьем и четвертом подциклах равенство кодов на входах дешифраторов 19 и 20 наступит при выборе ячеек 27, 32, 33 и 38 (З-я, 8-я, 9-я и 14-я) и ячеек 26, 31, 36 и 37 (2-я, 7-я, 12-я и 13-я) соответственно (фиг, 5 и фиг. б) и в них Запишется 1.

Таким образом, за полный цикл проверки произойдет перемещение 14 по диагонали матрицы каждого канала блока 24 памяти. Аналогично работает устройство при инверсном тесте, только в этом случае информация на вход регистра 3 будет подаваться через элемент НЕ 23.

Полная проверка оперативной паяти этим тестом займет К 2А А тактов, где А - количество адресов.

Тест Бегущая диагональ проверяет такие неисправности оперативной памяти как чувствительность к изменению состояний ячеек памяти, ложная запись информации в ячейку памяти при считывании из другой ячейки памяти, увеличение времени выборки и времени восстановления записи. Этот тест отлично проверяет такие неисправности как невозможность записи информации в ячейку, потеря чувствительности усилителей считывания, когда за серией информационных символов следует инверсное значение, а также неисправности дешифратора адреса в блоке 24. Тесты Дождь и 5, Адресный код имеют длину К 2А .

Применение теста Бегущая диагональ, таким образом, обеспечивает повышение быстродействия устройства.

Технико-экономическое преимущестал предложенного устройства заключается в более высоком быстродействии по сравнению с известным.

2526 27 ZB

2930 31 32

333 35 36

3738 35 0

Ф.иг.2

I О О О 0100 001 о 0001

ФигЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля оперативной памяти | 1980 |

|

SU955208A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU924758A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Устройство для отображения информации | 1987 |

|

SU1437909A1 |

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

УСТРОЙСТВО ДЗШ КОНТРОЛЯ ОПЕРАТИВНОЙ ПАМЯТИ, содержащее блок управления, регистр числа, счетный -триггер, Формирователь импульсов, счетчики, элемент И, основные и до полнительные коммутато Я 1, сумматор по модулю два и группу элементов И, причем вькоды первого счетчика и регистра числа, выход элемента И и выход блока управления являются выходами устройства, второй выход блока управления соединен с прямым входсхм элемента И, первыми, .входами счетного триггера и формирователя импульсов, выход которого .подключен к инверсному входу элемента И, выход которого соединен с входом первого счетчика, выход последнего разряда которого подключен к второму и третьему входам счетного триггера, выход которого соединен с втоЕ«1м .входом формирователя юшульсов, входом второго счетчика и первым входом сумматора по модулю два, второй вход которого подключен к выходу последнего разряда третьего счетчика, вход которого соединен с вторым выходом блока управления, третий выход которого подключен к входу синхронизации регистра числа, информационные входы которых соединены с выходами основных коммутаторов, первые и вторые информационные входы которых подключены соответственно к выходу сумматора по модулю два и к выходам дополнительных коммутаторов, управляющие входы которых соединены с выходами второго счетчика, информационные входы - с. выходами третьего счетчика, первые и вторые управляющие входы основi ных коммутйторов подключены соответственно к четвертому и пятому вы(Л ходам блока управления, отличающееся тем, что, с целью повышения быстродействия-устройства, в него введены дешифратор строк, дешифратор столбцов, элемент ИЛИ и элемент НЕ, выход и вход которого подключены соответственно к третьим и к четвертым информационным входам основных коммутаторов, выход элемента ИЛИ-соединен с входом элемента 4 О НЕ, а входы подключены к выводам элементов И группы, первые входы которых соединены с выходами деошфратора строк, а вторые входы - с вы, ходами дешифратора столбцов, входы которого подволочены к одним из выходов третьего счетчика, входы даиифратора строк соединены с одними из выходов первого счетчика, инверсный вход одного из элементов И группы подключен к выходу фо1%шроватепя им- пульсов.

X о о I

1000 0100 0010

Фи&М

0010 0001 1000 0100

Раг.$

0100 0010 0001

1000

Фиг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля оперативного накопителя информации | 1972 |

|

SU443414A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3337384/18-24, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-29—Подача