влод

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического измерения глубины амплитудной модуляции | 1979 |

|

SU781714A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| Система экстремального регулирования | 1985 |

|

SU1352452A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| РАДИОЛУЧЕВОЙ ДАТЧИК ОХРАНЫ | 1992 |

|

RU2079889C1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| УЛЬТРАЗВУКОВОЙ РАСХОДОМЕР | 2002 |

|

RU2210062C1 |

| Адаптивный коммутатор | 1982 |

|

SU1061170A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ R-ЗУБЦА ЭЛЕКТРОКАРДИОСИГНАЛА | 1989 |

|

RU2012226C1 |

Изобретение позволяет расширить частотный диапазон устройство для измерения периода сигнала сложной формы. Устройство содержит компаратор 4 с нулевым порогом срабатывания и преобразователь 5 временного интервала в код. Введение (N-1) фильтров 1 нижних частот, коммутаторов 2 и 3, двухполупериодного выпрямителя 6, пиковых детекторов 7 и 8, регулируемого аттенюатора 9, компаратора 10 и блока 11 управления позволяет однозначно определять фильтры, в рабочий диапазон которых попадает основная гармоника измеряемого сигнала. Кроме того, обеспечивается возможность путем коммутации выбрать фильтр с максимальным уровнем сигнала для последующего измерения периода. В описании приведен пример реализации блока 11 управления. 1 з.п.ф-лы, 1 табл., 7 ил.

сд 1

оэ оо оо

Фиг.1

Изобретение относится к импульсной технике и может быть использовано для измерения периода.

Цель изобретения - расширение час- тотного диапазона устройства для измерения периода сигнала сложной формы

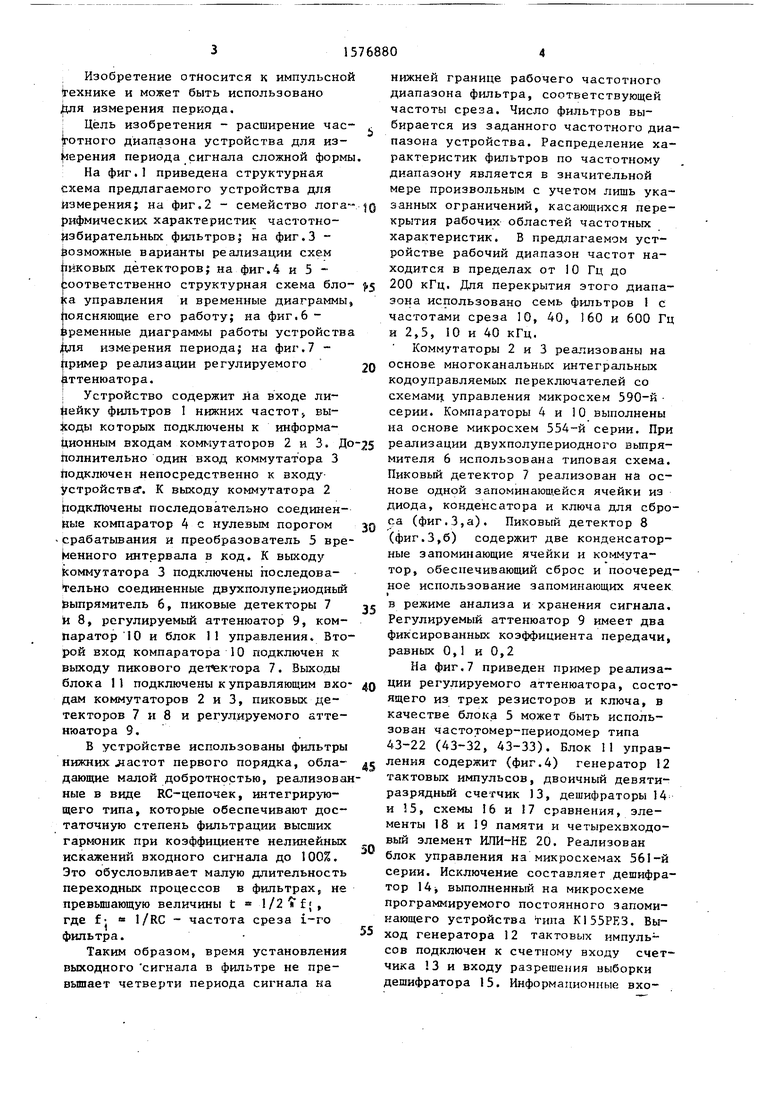

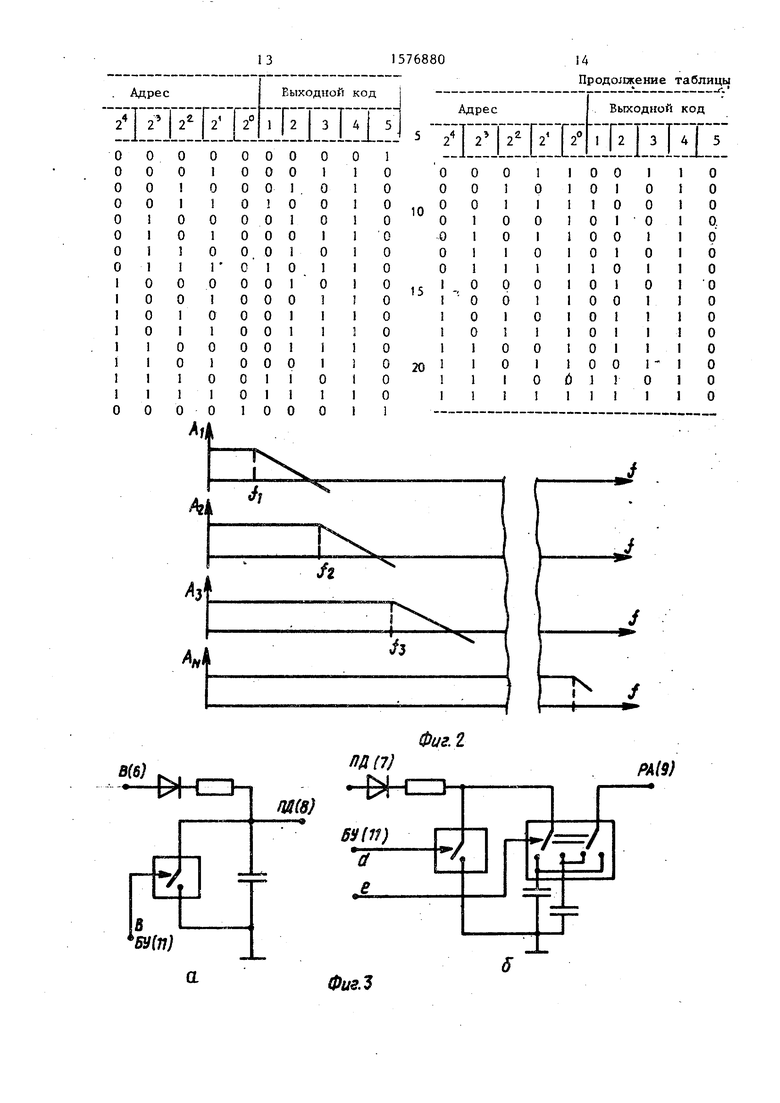

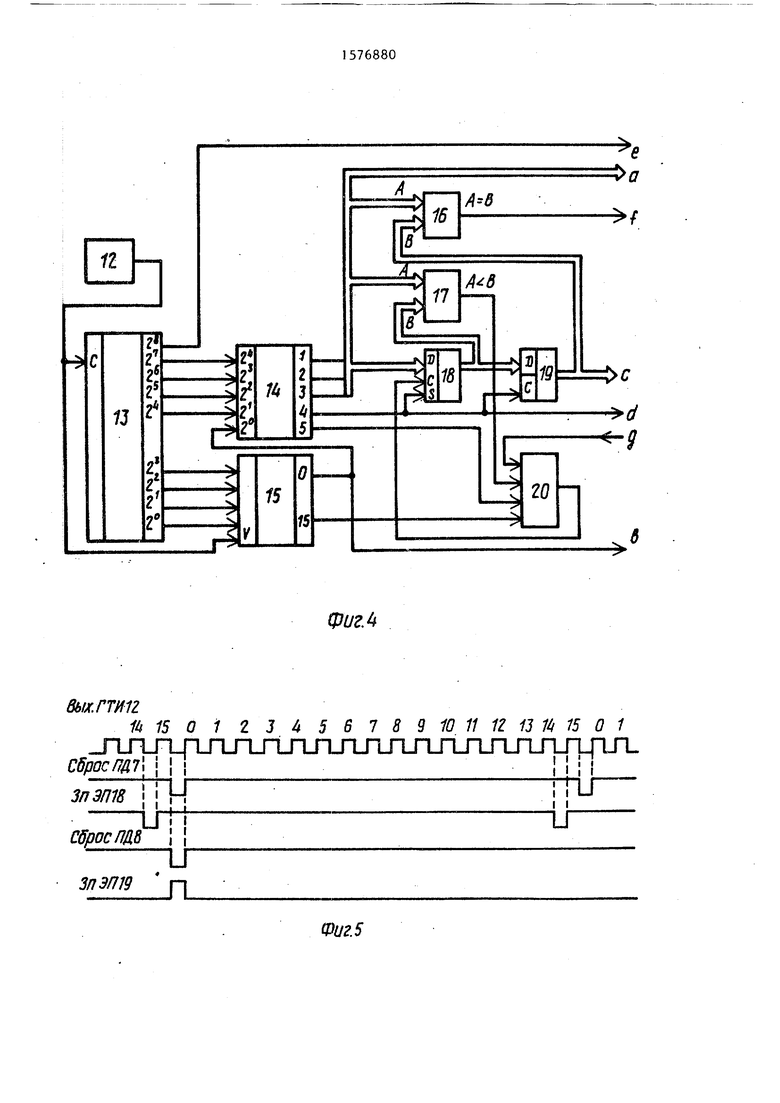

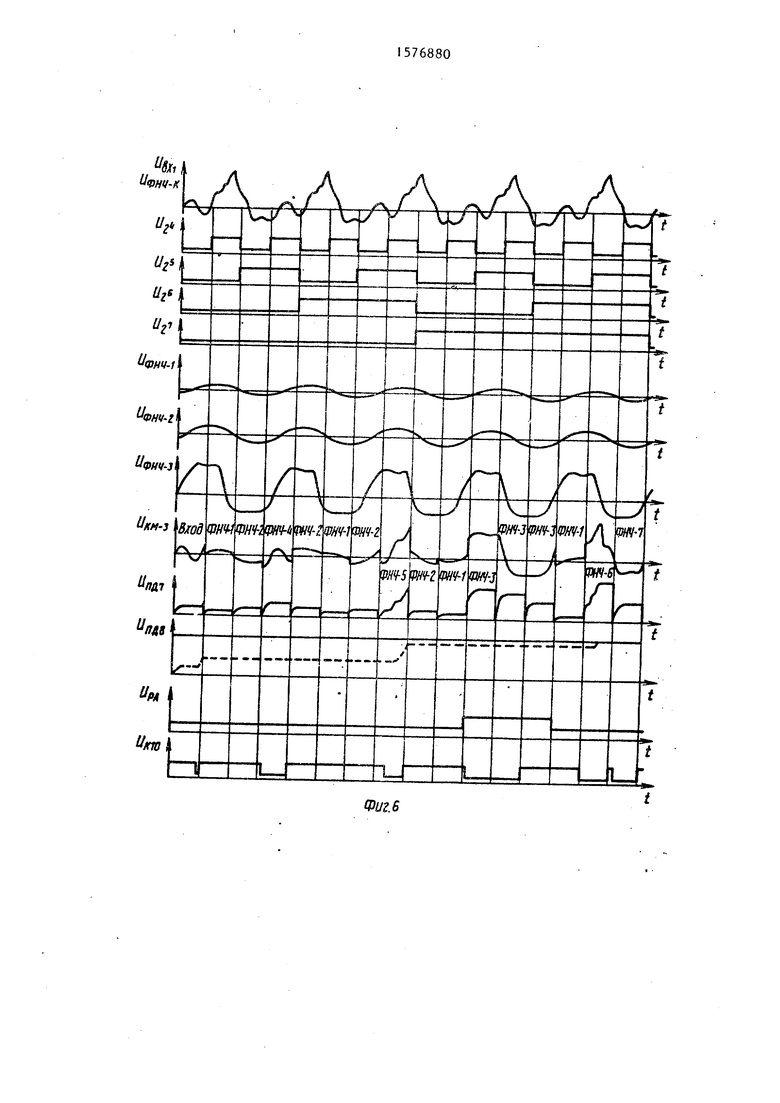

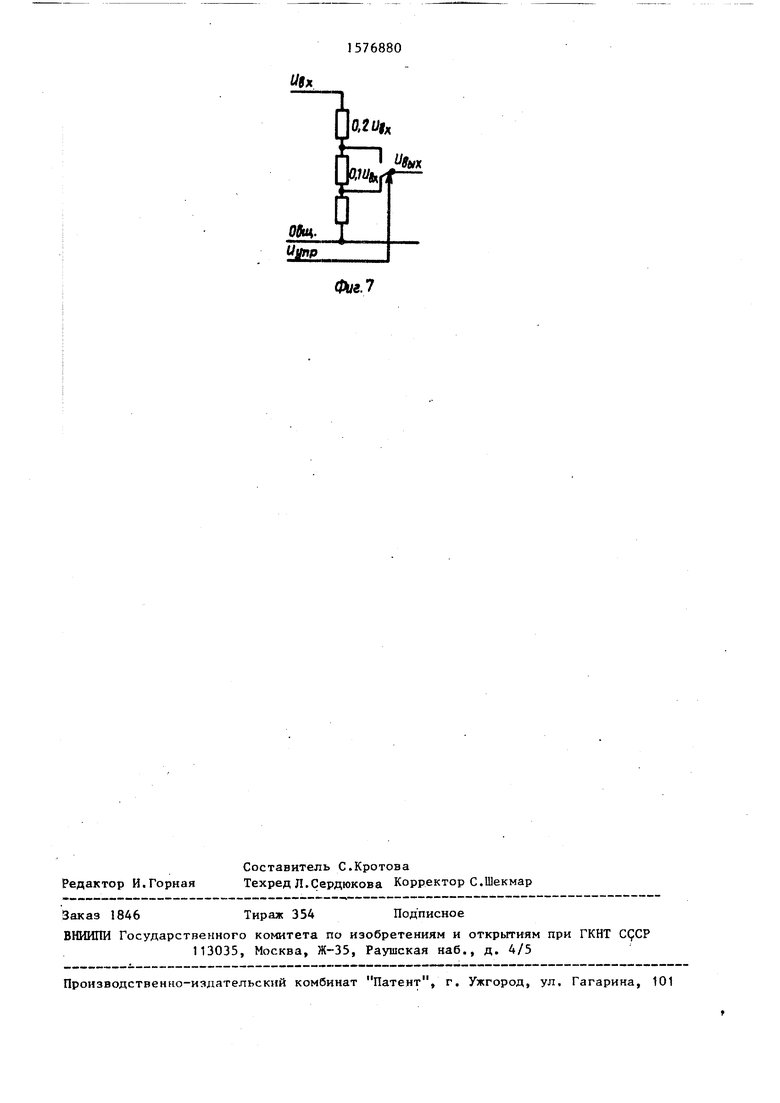

На фиг.1 приведена структурная схема предлагаемого устройства для измерения; на фиг.2 - семейство лога- рифмических характеристик частотно- избирательных фильтров на фиг.З - возможные варианты реализации схем пиковых детекторов; на фиг.4 и 5 - соответственно структурная схема бло- ка управления и временные диаграммы, поясняющие его работу; на фиг.6- временные диаграммы работы устройства для измерения периода; на фиг.7 - пример реализации регулируемого аттенюатора.

Устройство содержит на входе линейку фильтров 1 нижних частот, выходы которых подключены к информационным входам коммутаторов 2 и 3. До полнительно один вход коммутатора 3 подключен непосредственно к входу устройства. К выходу коммутатора 2 подключены последовательно соединенные компаратор 4 с нулевым порогом срабатывания и преобразователь 5 временного интервала в код. К выходу коммутатора 3 подключены последовательно соединенные двухполупериодный выпрямитель 6, пиковые детекторы 7 и 8, регулируемый аттенюатор 9, компаратор 10 и блок 11 управления. Второй вход компаратора 10 подключен к выходу пикового детектора 7. Выходы блока 11 подключены к управляющим вхо- дам коммутаторов 2 и 3, пиковых детекторов 7 и 8 и регулируемого аттенюатора 9.

В устройстве использованы фильтры нижних .настот первого порядка, обла- дающие малой добротностью, реализованные в виде RC-цепочек, интегрирующего типа, которые обеспечивают достаточную степень фильтрации высших гармоник при коэффициенте нелинейных искажений входного сигнала до 100%. Это обусловливает малую длительность переходных процессов в фильтрах, не превышающую величины t ж l/2li f«, где f- e 1/RC - частота среза 1-го фильтра.

Таким образом, время установления выходного сигнала в фильтре не превышает четверти периода сигнала на

-

Q 5 0

§

0

нижней границе рабочего частотного диапазона фильтра, соответствующей частоты среза. Число фильтров выбирается из заданного частотного диапазона устройства. Распределение характеристик фильтров по частотному диапазону является в значительной мере произвольным с учетом лишь указанных ограничений, касающихся перекрытия рабочих областей частотных характеристик. В предлагаемом устройстве рабочий диапазон частот находится в пределах от 10 Гц до 200 кГц. Для перекрытия этого диапазона использовано семь фильтров 1 с частотами среза 10, 40, 160 и 600 Гц и 2,5, 10 и 40 кГц.

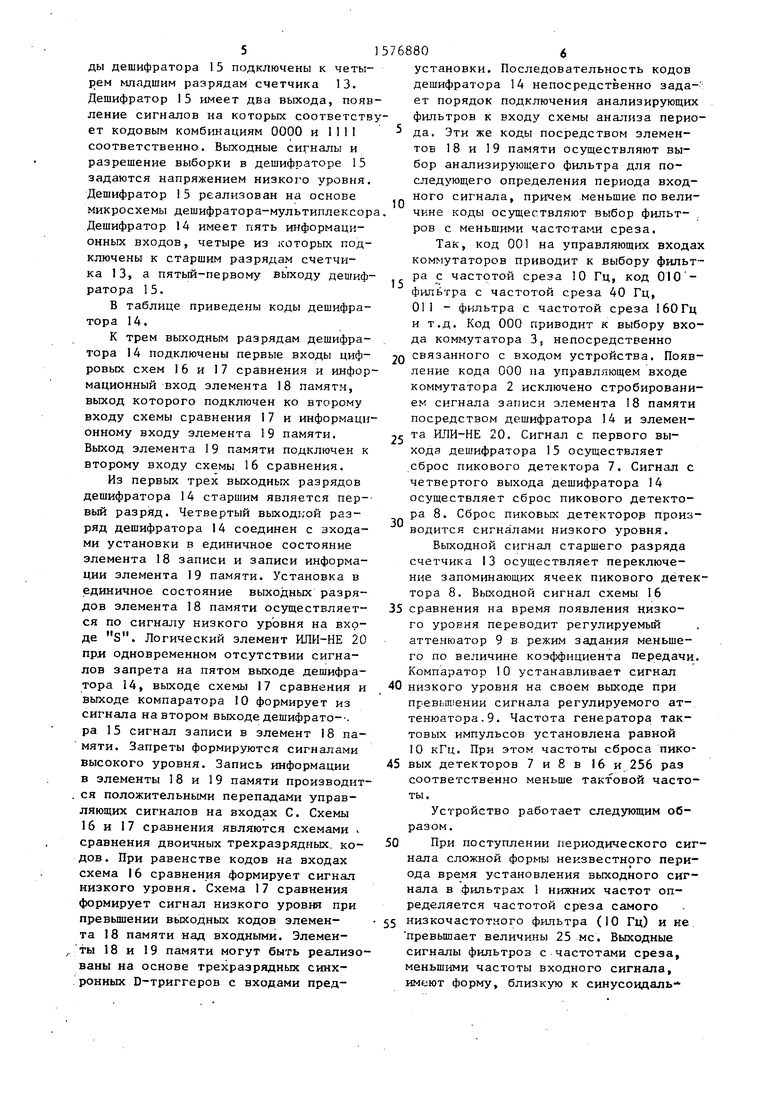

Коммутаторы 2 и 3 реализованы на основе многоканальных интегральных кодоуправляемых переключателей со схемами; управления микросхем 590-й серии. Компараторы 4 и 10 выполнены на основе микросхем 554-й серии. При реализации двухполупериодного выпрямителя 6 использована типовая схема. Пиковый детектор 7 реализован на основе одной запоминающейся ячейки из диода, конденсатора и ключа для сброса (фиг.З,а). Пиковый детектор 8 (фиг.3,6) содержит две конденсаторные запоминающие ячейки и коммутатор, обеспечивающий сброс и поочередное использование запоминающих ячеек i

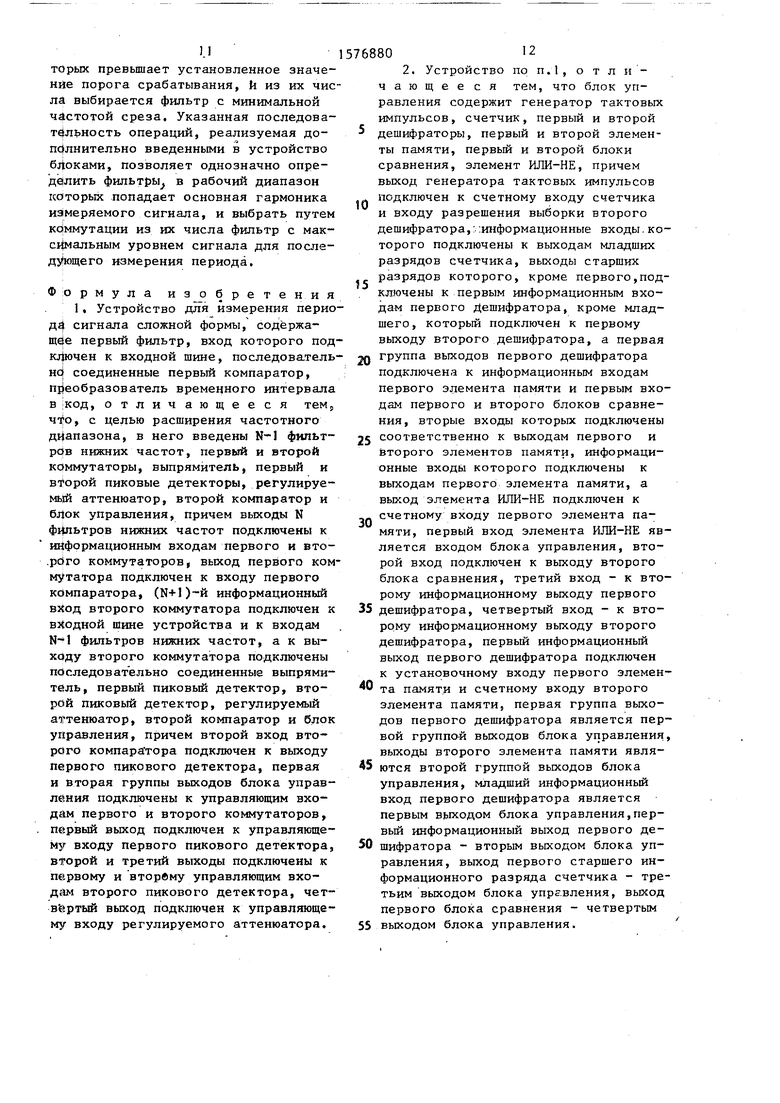

в режиме анализа и хранения сигнала. Регулируемый аттенюатор 9 имеет два фиксированных коэффициента передачи, равных 0,1 и 0,2

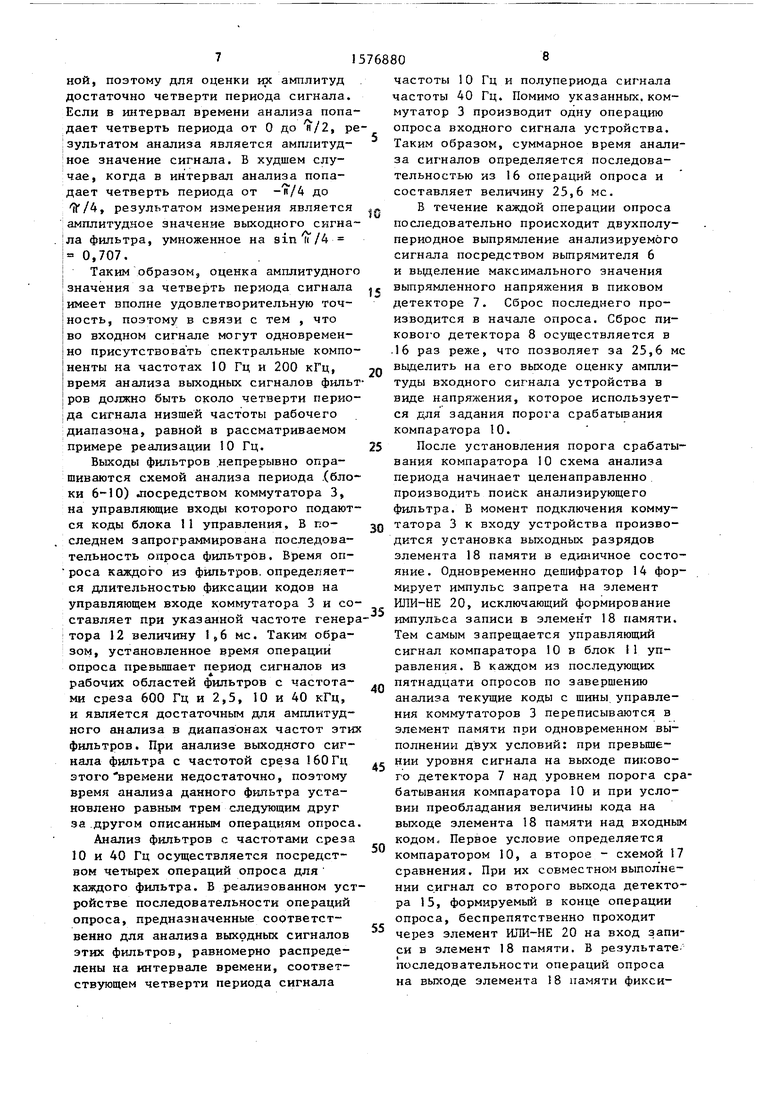

На фиг.7 приведен пример реализации регулируемого аттенюатора, состоящего из трех резисторов и ключа, в качестве блока 5 может быть использован частотомер-периодомер типа 43-22 (43-32, 43-33). Блок 11 управления содержит (фиг.4) генератор 12 тактовых импульсов, двоичный девятиразрядный счегчик 13, дешифраторы 14 и 15, схемы 16 и 17 сравнения, элементы 18 и 19 памяти и четырехвходо- вый элемент ИЛИ-НЕ 20. Реализован блок управления на микросхемах 561-й серии. Исключение составляет дешифратор 14, выполненный на микросхеме программируемого постоянного запоминающего устройства типа KI55PE3. Выход генератора 12 тактовых импульсов подключен к счетному входу счетчика 13 и входу разрешения выборки дешифратора 15. Информационные входы дешифратора I5 подключены к четырем младшим разрядам счетчика 13. Дешифратор 15 имеет два выхода, появление сигналов на которых соответствет кодовым комбинациям 0000 и 1111 соответственно. Выходные сигналы и разрешение выборки в дешифраторе 15 задаются напряжением низкого уровня. Дешифратор 15 реализован на основе микросхемы дешифратора-мультиплексор Дешифратор 14 имеет пять информационных входов, четыре из которых подключены к старшим разрядам счетчика 13, а пятый-первому выходу дешифратора 15.

В таблице приведены коды дешифратора 14.

К трем выходным разрядам дешифратора 14 подключены первые входы цифровых схем 16 и 17 сравнения и информационный вход элемента 18 памяти, выход которого подключен ко второму входу схемы сравнения 17 и информационному входу элемента 19 памяти. Выход элемента 19 памяти подключен к второму входу схемы 16 сравнения.

Из первых трех выходных разрядов дешифратора 14 старшим является первый разряд. Четвертый выходкой разряд дешифратора 14 соединен с входами установки в единичное состояние элемента 18 записи и записи информации элемента 19 памяти. Установка в единичное состояние выходных разрядов элемента 18 памяти осуществляется по сигналу низкого уровня на вхр- де S. Логический элемент ИЛИ-НЕ 20 при одновременном отсутствии сигналов запрета на пятом выходе дешифратора 14, выходе схемы 17 сравнения и выходе компаратора 10 формирует из сигнала на втором выходе дешифрато- . ра 15 сигнал записи в элемент 18 памяти. Запреты формируются сигналами высокого уровня. Запись информации в элементы 18 и 19 памяти производится положительными перепадами управляющих сигналов на входах С. Схемы 16 и 17 сравнения являются схемами сравнения двоичных трехразрядных кодов. При равенстве кодов на входах схема 16 сравнения формирует сигнал низкого уровня. Схема 17 сравнения формирует сигнал низкого уровня при превышении выходных кодов элемента 18 памяти над входными. Элементы 18 и 19 памяти могут быть реализованы на основе трехразрядных синхронных D-триггеров с входами пред0

5

5

установки. Последовательность кодов дешифратора 14 непосредственно задает порядок подключения анализирующих фильтров к входу схемы анализа периода. Эти же коды посредством элементов 18 и 19 памяти осуществляют выбор анализирующего фильтра для последующего определения периода входного сигнала, причем меньшие по величине коды осуществляют выбор фильтров с меньшими частотами среза.

Так, код 001 на управляющих входах коммутаторов приводит к выбору фильтра с частотой среза 10 Гц, код 010 - фильтра с частотой среза 40 Гц, ОМ - фильтра с частотой среза 160 Гц и т.д. Код 000 приводит к выбору входа коммутатора 3Р непосредственно Q связанного с входом устройства. Появление кода 000 на управляющем входе коммутатора 2 исключено стробировани- ем сигнала записи элемента 18 памяти посредством дешифратора 14 и элемента ИЛИ-НЕ 20. Сигнал с первого выхода дешифратора 15 осуществляет сброс пикового детектора 7. Сигнал с четвертого выхода дешифратора 14 осуществляет сброс пикового детектора 8. Сброс пиковых детекторов производится сигналами низкого уровня.

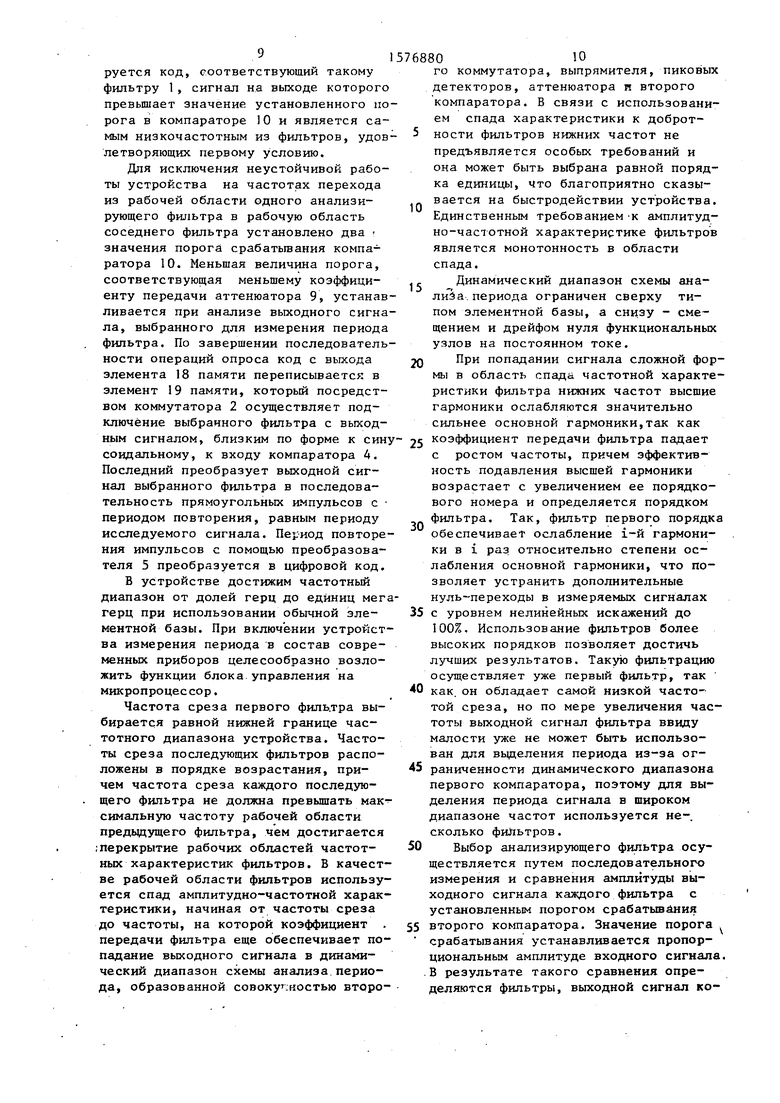

Выходной сигнал старшего разряда счетчика 13 осуществляет переключение запоминающих ячеек пикового детектора 8. Выходной сигнал схемы 16 5 сравнения на время появления низкого уровня переводит регулируемый аттенюатор 9 в режим задания меньшего по величине коэффициента передачи. Компаратор 10 устанавливает сигнал 0 низкого уровня на своем выходе при превьпении сигнала регулируемого аттенюатора. 9. Частота генератора тактовых импульсов установлена равной 10 кГц. При этом частоты сброса пиковых детекторов 7 и 8 в 16 и 256 раз соответственно меньше тактовой частоты.

Устройство работает следующим образом.

При поступлении периодического сигнала сложной формы неизвестного периода время установления выходного сигнала в фильтрах 1 нижних частот определяется частотой среза самого 5 низкочастотного фильтра (10 Гц) и ке превышает величины 25 мс. Выходные сигналы фильтров с частотами среза, меньшими частоты входного сигнала, имеют форму, близкую к синусоидаль- 0

5

0

ной, поэтому для оценки их амплитуд достаточно четверти периода сигнала. Если в интервал времени анализа попадает четверть периода от 0 до н/2, результатом анализа является амплитудное значение сигнала. В худшем случае, когда в интервал анализа попадает четверть периода от - и/4 до If/4, результатом измерения является амплитудное значение выходного сигнала фильтра, умноженное на sin ft/4 0,707,

Таким образом, оценка амплитудного значения за четверть периода сигнала имеет вполне удовлетворительную точность, поэтому в связи с тем , что

во входном сигнале могут одновременно присутствовать спектральные компоненты на частотах 10 Гц и 200 кГц, время анализа выходных сигналов фильтров должно быть около четверти периода сигнала низшей частоты рабочего диапазона, равной в рассматриваемом примере реализации 10 Гц.

Выходы фильтров непрерывно опрашиваются схемой анализа периода .(блоки 6-10) .посредством коммутатора 3, на управляющие входы которого подаются коды блока 11 управления, В последнем запрограммирована последовательность опроса фильтров. Время оп- роса каждого из фильтров, определяется длительностью фиксации кодов на управляющем входе коммутатора 3 и составляет при указанной частоте генератора 12 величину 1,6 мс. Таким образом, установленное время операций опроса превышает период сигналов из рабочих областей фильтров с частотами среза 600 Гц и 2,5, 10 и 40 кГц, и является достаточным для амплитудного анализа в диапазонах частот этих фильтров. При анализе выходного сигнала фильтра с частотой среза 160 Гц этого времени недостаточно, поэтому время анализа данного фильтра установлено равным трем следующим друг за другом описанным операциям опроса. Анализ фильтров с частотами среза 10 и 40 Гц осуществляется посредством четырех операций опроса для каждого фильтра. В реализованном устройстве последовательности операций опроса, предназначенные соответственно для анализа выходных сигналов этих фильтров, равномерно распределены на интервале времени, соответствующем четверти периода сигнала

1C

15

20

25

5768808

частоты 10 Гц и полупериода сигнала частоты 40 Гц. Помимо указанных, коммутатор 3 производит одну операцию опроса входного сигнала устройства. Таким образом, суммарное время анализа сигналов определяется последовательностью из 16 операций опроса и составляет величину 25,6 мс.

В течение каждой операции опроса последовательно происходит двухполу- периодное выпрямление анализируемого сигнала посредством выпрямителя 6 и выделение максимального значения выпрямленного напряжения в пиковом детекторе 7. Сброс последнего производится в начале опроса. Сброс пикового детектора 8 осуществляется в 16 раз реже, что позволяет за 25,6 мс выделить на его выходе оценку амплитуды входного сигнала устройства в виде напряжения, которое используется для задания порога срабатывания компаратора 10.

После установления порога срабатывания компаратора 10 схема анализа периода начинает целенаправленно производить поиск анализирующего фильтра. В момент подключения коммутатора 3 к входу устройства производится установка выходных разрядов элемента 18 памяти в единичное состояние . Одновременно дешифратор 14 формирует импульс запрета на элемент ИЛИ-НЕ 20, исключающий формирование импульса записи в элемент 18 памяти. Тем самым запрещается управляющий сигнал компаратора 10 в блок II управления. В каждом из последующих пятнадцати опросов по завершению анализа текущие коды с шины управления коммутаторов 3 переписываются в элемент памяти при одновременном выполнении двух условий: при превышении уровня сигнала на выходе пикового детектора 7 над уровнем порога срабатывания компаратора 10 и при условии преобладания величины кода на выходе элемента 18 памяти над входным кодом. Первое условие определяется компаратором 10, а второе - схемой 17 сравнения. При их совместном выпол не- нии сигнал со второго выхода детектора 15, формируемый в конце операции опроса, беспрепятственно проходит через элемент ИЛИ-НЕ 20 на вход записи в элемент 18 памяти. В результате. последовательности операций опроса

на выходе элемента 18 памяти фикси30

35

40

45

50

55

руется код, соответствующий такому фильтру 1, сигнал на выходе которого превышает значение установленного порога в компараторе 10 и является самым низкочастотным из фильтров, удовлетворяющих первому условию.

Для исключения неустойчивой работы устройства на частотах перехода из рабочей области одного анализирующего фильтра в рабочую область соседнего фильтра установлено два значения порога срабатывания компаратора 10. Меньшая величина порога, соответствующая меньшему коэффициенту передачи аттенюатора 9, устанавливается при анализе выходного сигнала, выбранного для измерения периода фильтра. По завершении последовательности операций опроса код с выхода элемента 18 памяти переписывается в элемент 19 памяти, который посредством коммутатора 2 осуществляет подключение выбранного фильтра с выходным сигналом, близким по форме к сину- 25 коэффициент передачи фильтра падает

соидальному, к входу компаратора А. Последний преобразует выходной сигнал выбранного фильтра в последовательность прямоугольных импульсов с - периодом повторения, равным периоду исследуемого сигнала. Период повторения импульсов с помощью преобразователя 5 преобразуется в цифровой код.

В устройстве достижим частотный диапазон от долей герц до единиц мегагерц при использовании обычной элементной базы. При включении устройства измерения периода в состав современных приборов целесообразно возложить функции блока управления на микропроцессор.

Частота среза первого филь.тра выбирается равной нижней границе частотного диапазона устройства. Частоты среза последующих фильтров расположены в порядке возрастания, причем частота среза каждого последующего фильтра не должна превышать максимальную частоту рабочей области предыдущего фильтра, чем достигается ;перекрытие рабочих областей частотных характеристик фильтров. В качестве рабочей области фильтров используется спад амплитудно-частотной характеристики, начиная от частоты среза до частоты, на которой коэффициент . передачи фильтра еще обеспечивает попадание выходного сигнала в динамический диапазон схемы анализа периода, образованной совокулзостью второ-

30

35

40

45

50

55

с ростом частоты, причем эффективность подавления высшей гармоники возрастает с увеличением ее порядкового номера и определяется порядком фильтра. Так, фильтр первого порядк обеспечивает ослабление i-й гармоники в i раз относительно степени ослабления основной гармоники, что позволяет устранить дополнительные нуль-переходы в измеряемых сигналах с уровнем нелинейных искажений до 100%. Использование фильтров более высоких порядков позволяет достичь лучших результатов. Такую фильтрацию осуществляет уже первый фильтр, так как. он обладает самой низкой частотой среза, но по мере увеличения час тоты выходной сигнал фильтра ввиду малости уже не может быть использован для выделения периода из-за ограниченности динамического диапазона первого компаратора, поэтому для выделения периода сигнала в широком диапазоне частот используется не-. сколько фильтров.

Выбор анализирующего фильтра осуществляется путем последовательного измерения и сравнения амплитуды выходного сигнала каждого фильтра с установленным порогом срабатывания второго компаратора. Значение порога срабатывания устанавливается пропорциональным амплитуде входного сигнал В результате такого сравнения определяются фильтры, выходной сигнал ко

10

76880Ю

го коммутатора, выпрямителя, пиковых

детекторов, аттенюатора и второго компаратора. В связи с использованием спада характеристики к добротности фильтров нижних частот не предъявляется особых требований и она может быть выбрана равной порядка единицы, что благоприятно сказывается на быстродействии устройства. Единственным требованием -к амплитудно-частотной характеристике фильтров является монотонность в области спада.

Динамический диапазон схемы анализа периода ограничен сверху типом элементной базы, а снизу - смещением и дрейфом нуля функциональных узлов на постоянном токе.

При попадании сигнала сложной формы в область спада частотной характеристики фильтра нижних частот высшие гармоники ослабляются значительно сильнее основной гармоники,так как

15

20

5 коэффициент передачи фильтра падает

0

5

0

5

0

5

с ростом частоты, причем эффективность подавления высшей гармоники возрастает с увеличением ее порядкового номера и определяется порядком фильтра. Так, фильтр первого порядка обеспечивает ослабление i-й гармоники в i раз относительно степени ослабления основной гармоники, что позволяет устранить дополнительные нуль-переходы в измеряемых сигналах с уровнем нелинейных искажений до 100%. Использование фильтров более высоких порядков позволяет достичь лучших результатов. Такую фильтрацию осуществляет уже первый фильтр, так как. он обладает самой низкой частотой среза, но по мере увеличения частоты выходной сигнал фильтра ввиду малости уже не может быть использован для выделения периода из-за ограниченности динамического диапазона первого компаратора, поэтому для выделения периода сигнала в широком диапазоне частот используется не-. сколько фильтров.

Выбор анализирующего фильтра осуществляется путем последовательного измерения и сравнения амплитуды выходного сигнала каждого фильтра с установленным порогом срабатывания второго компаратора. Значение порога срабатывания устанавливается пропорциональным амплитуде входного сигнала В результате такого сравнения определяются фильтры, выходной сигнал коU

торых превышает установленное значение порога срабатывания, k из их числа выбирается фильтр с минимальной частотой среза. Указанная последовательность операций, реализуемая дополнительно введенными в устройство блоками, позволяет однозначно определить фильтры в рабочий диапазон которых попадает основная гармоника измеряемого сигнала, и выбрать путем коммутации из их числа фильтр с максимальным уровнем сигнала для последующего измерения периода.

Формула и бретения

10

15

7688012

5 дешифраторы, первый и второй элементы памяти, первый и второй блоки сравнения, элемент ИЛИ-НЕ, причем выход генератора тактовых импульсов подключен к счетному входу счетчика и входу разрешения выборки второго дешифратора, информационные входы которого подключены к выходам младших разрядов счетчика, выходы старших разрядов которого, кроме первого,подключены к первым информационным входам первого Дешифратора, кроме младшего, который подключен к первому выходу второго дешифратора, а первая

2Q группа выходов первого дешифратора подключена к информационным входам первого элемента памяти и первым входам первого и второго блоков сравнения, вторые входы которых подключены

25 соответственно к выходам первого и второго элементов памяти, информационные входы которого подключены к выходам первого элемента памяти, а выход элемента ИЛИ-НЕ подключен к счетному входу первого элемента памяти, первый вход элемента ИЛИ-НЕ является входом блока управления, второй вход подключен к выходу второго блока сравнения, третий вход - к второму информационному выходу первого

35 дешифратора, четвертый вход - к второму информационному выходу второго дешифратора, первый информационный выход первого дешифратора подключен к установочному входу первого элемен40 та памяти и счетному входу второго элемента памяти, первая группа выходов первого дешифратора является первой группой выходов блока управления, выходы второго элемента памяти явля45 ются второй группой выходов блока управления, младший информационный вход первого дешифратора является первым выходом блока управления,первый информационный выход первого де50 шифратора - вторым выходом блока управления, выход первого старшего информационного разряда счетчика - третьим выходом блока управления, выход первого блока сравнения - четвертым

55 выходом блока управления.

30

а.

Фиг.З

Фиг. 4

ВЫХ.ГТИ11 1U

15 0 1 г 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1

TU1JT4TJTJTJTJTJTJTJT

Фиг. 5

% иФнч-i

Up

Цгв

a

Уфнч-Л

ифнч-г

ЦФНЧ-З

UKH.

КМ-З

Редактор И.Горная

Составитель С.Кротона

Техред Л. Сердюков а Корректор С.Шекмар

Заказ 1846

Тираж 354

ВНИИГШ Государственного комитета по изобретениям и открытиям при ГКНТ C(JCP 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г, Ужгород, ул. Гагарина, 101

Подписное

| Цфировой измеритель длительности периода квазигармонических сигналов | 1973 |

|

SU600513A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-07-07—Публикация

1986-09-22—Подача