ел

о со со о оэ

Изобретение относится к радиотехнике, в частности к устройствам цифровой низкочастотной фильтрации, и может быть использовано в системах цифровой обработки сигналов.

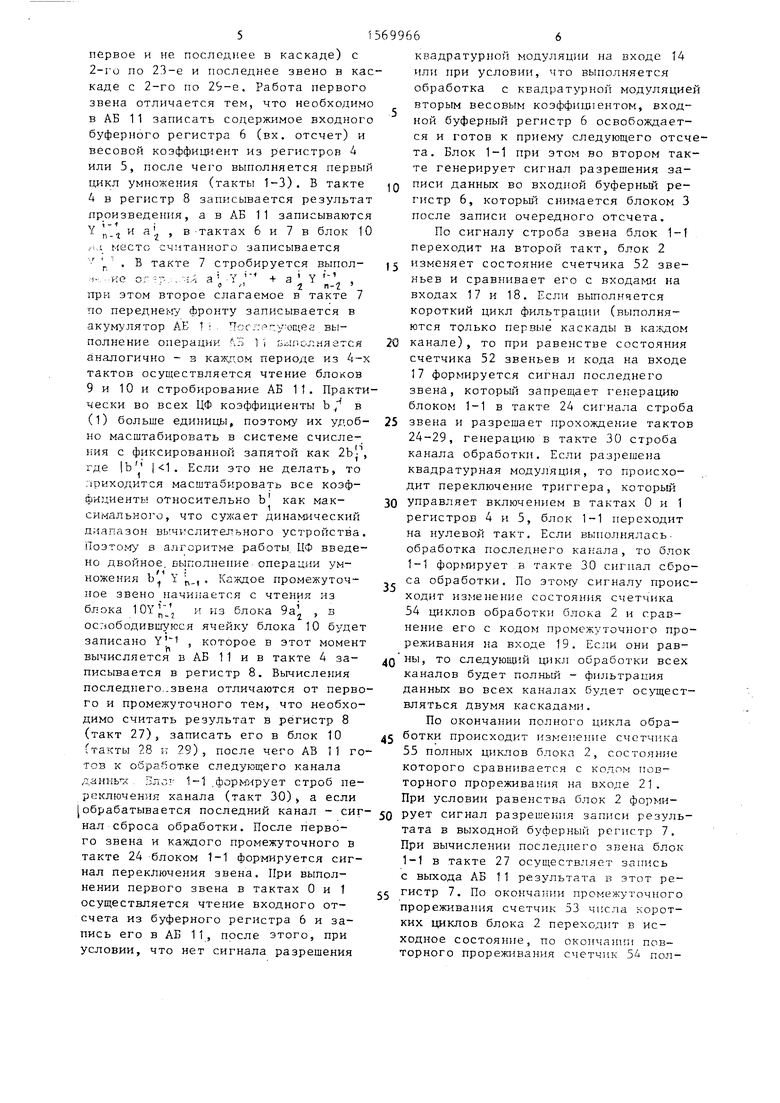

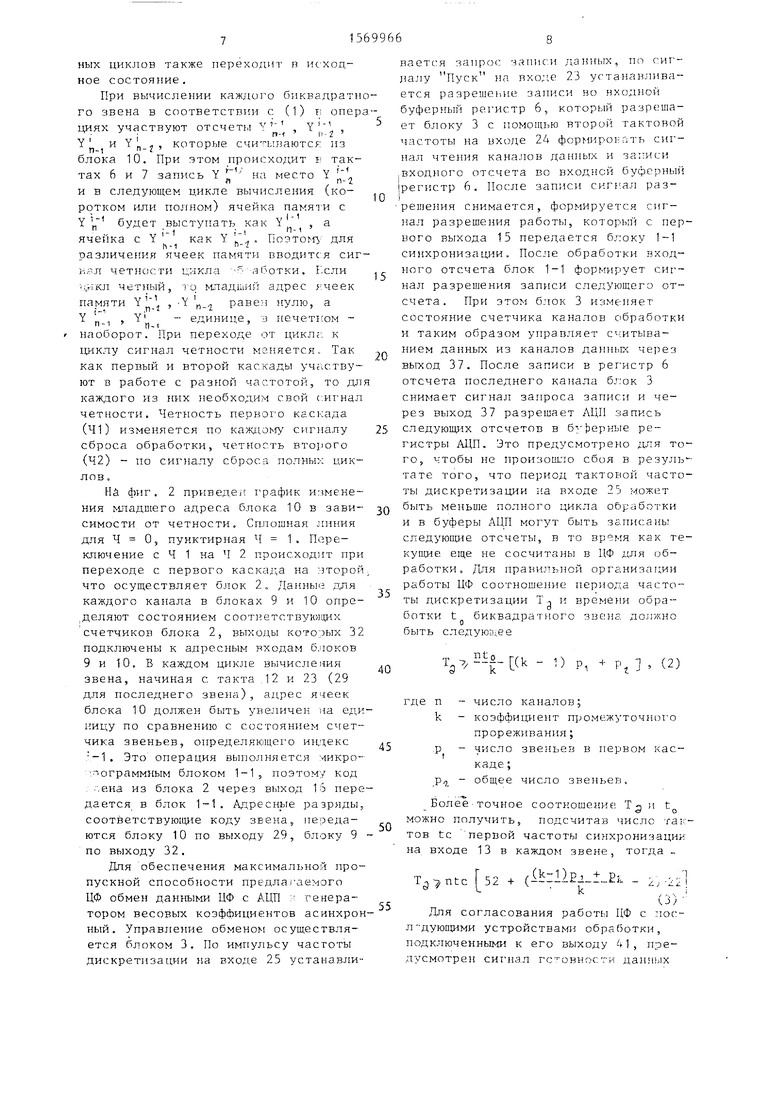

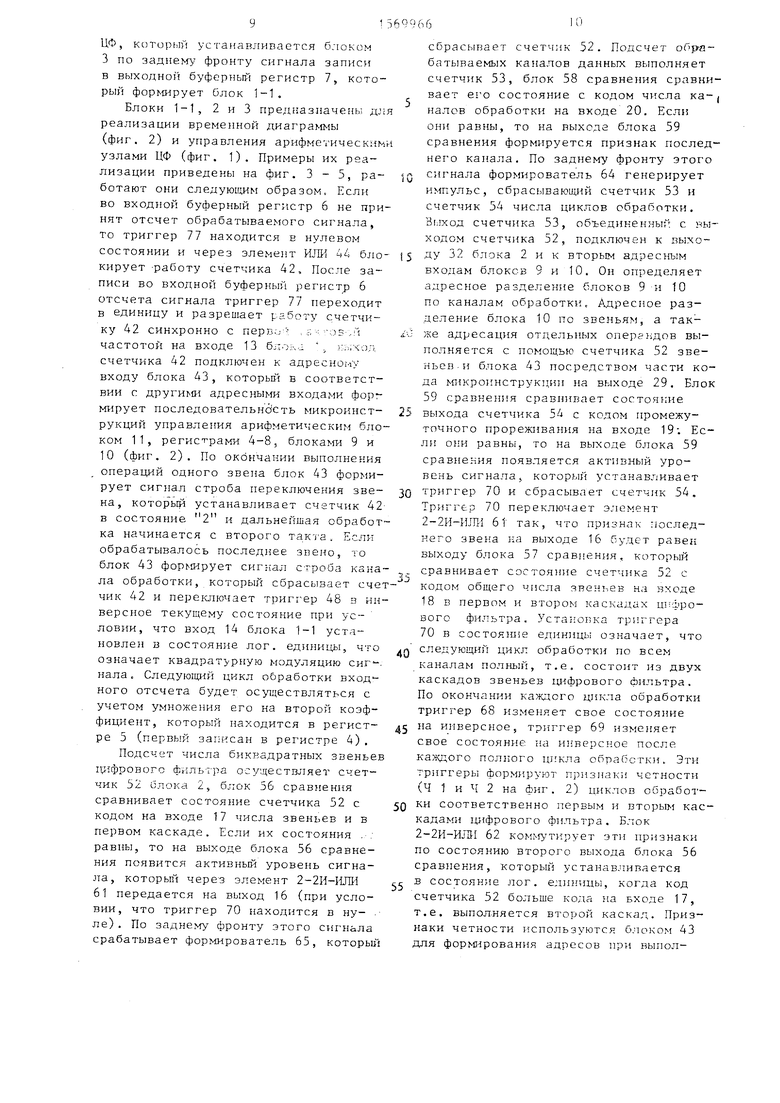

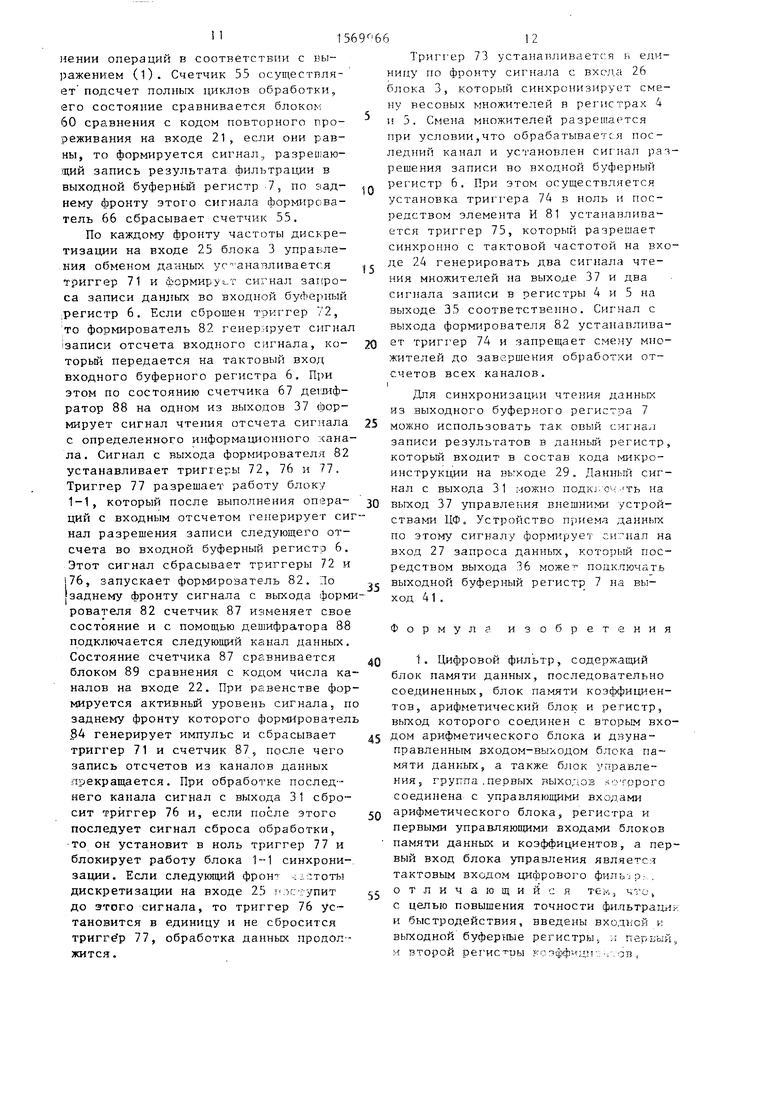

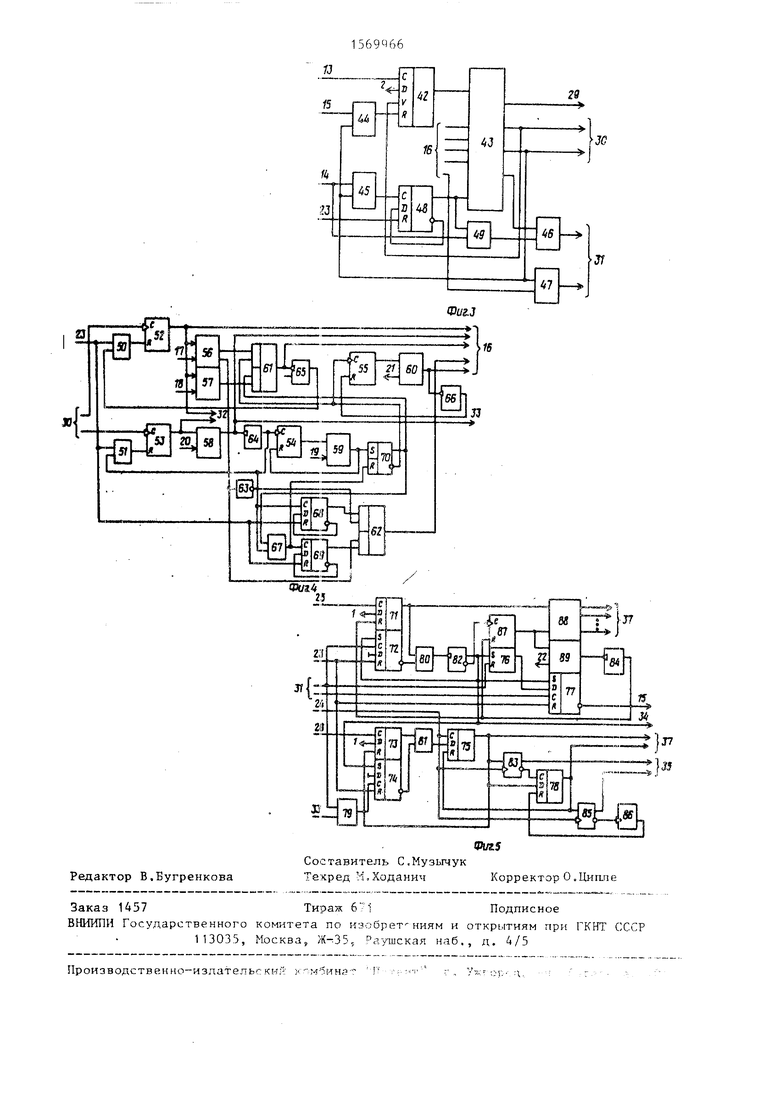

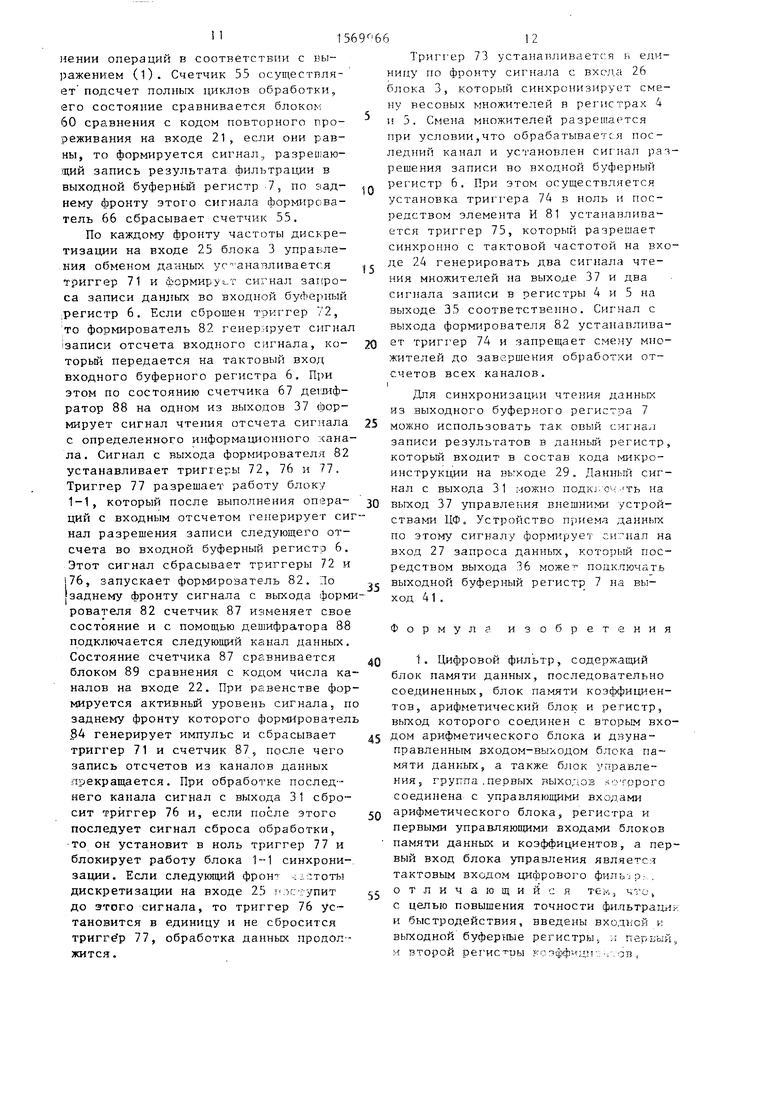

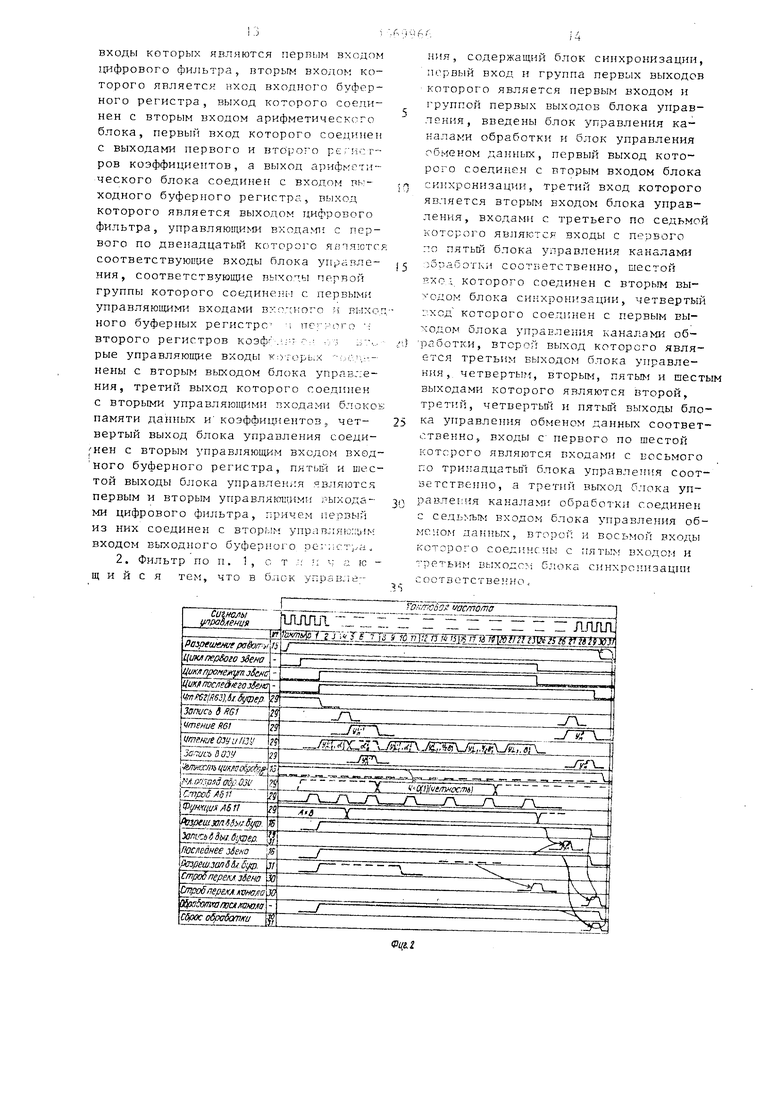

Цель изобретения - повышение точности фильтрации и быстродействия. На фиг. 1 приведена электрическая структурная схема цифрового филь ра; на фиг. 2 - временные диаграммы, поясняющие его работу; на фиг. 3-5 - электрическая структурная схема бло- синхронизации, управления каналами обработки и управлс (ия обменом данных.

Цифровой фильтр содержит блок 1 управления, содержащий блок 1-1 синхронизации, блок 2 управления каналами обработки и блок 3 управления меном данных, первый и второй регистры А и 5 коэффициентов, входной и выходной буферные регистры 6 и 7, регистр 8, блок 9 памяти коэффициентов, блок 10 памяти данных, арифме- тический блок (АБ) 11, первый вход 12, тактовый вход 13, первый управляющий вход 14, первый выход 15 блока управления обменом данных, первый выход 16 блока управления каналами обработки, управляющие входы с второ |го по двенадцатый 17-27, второй вход 28, группу первых выходов 29 блока управления, второй и третий выходы 30 и 31 блока синхронизации, второй и третий выходы 32 и 33 блока управления каналами обработки, второй, третий, четвертый и пятый выхбды 34-37 блока управления обменом данных, первый и второй входы 38 и 39 .и выход 40 арифметического блока и выход 41 цифрового фильтра.

Блок 1-1 синхронизации содержит счетчик 42, блок 43 памяти микрокоманд, элемент ИЛИ 44, элементы И 45-47, триггер 48, элемент ИСКЛЮЧАЮ- ,. ИЛИ 49.

Блок 2 управления каналами обработки содержит элементы И.50 и 51, счетчики 52-55, блоки 56-60 сравнения, элементы 2-2И-ИЛИ 61 и 62, инвертор 63, формирователи 64-66 импульсов, элемент И 67, триггеры 68-70.

Блок 3 управления обменом данных содержит триггеры 71-78, элементы И 79-81, формирователи 82-86 импул„- сов, счетчик 87, дешифратор 88 и бл 89 сравнения.

Q

0

5

Цифровой фильтр работает следующим образом.

В начале сигнал Пуск, поступающий на восьмой управляющий вход 23, устанавливает все триггерные и счетные схемы блоков 1-3 в исходное состояние и состояние Стоп. С помощью кодов, поступающих на входы 14, 17- 22, определяется режим работы ЦФ с квадратурной модуляцией или нет (вход 14), если вводится промежуточное прореживание, то устанавливается число звеньев в первом каскаде (вход 17), общее число звеньев в первом и во втором каскадах (вход 18), код прореживания после первого каскада (вход 19) и коэффициент прореживания после второго каскада (вход 21). Если промежуточного прореживания нет, то код на входе 17 равен коду входа 18. Код на входе 19 равен нулю. Если после второго каскада также нет прореживания, то код на входе 21 равен нулю. Если обрабатываются данные с нескольких каналов, то устанавливаются коды на входах 20 и 22, в противном случае они равны нулю. Если осуществляется квадратурная модуляция, то код на входе 20 в два раза больше кода на входе .22, если нет, то они равны. Все перечисленные коды устанавливаются распайкой соответствующих контактов к логическому нулю или единице.

Блок 1-1 синхронизации предназначен для управления последовательностью выполнения операций АБ 11 и обменом данных в шинах 38 и 39 при реализации биквадратного эвена в соответствии со следующим выражением.

Y а a + a Ybv + Yn ao n + а, п- а 1 п-7

+ + , (1)

где i - номер звена, Y - - входные данные, Y - выходные, b ,1 -b 1 /2, b 14 -b . На фиг. 2 приведена временная диаграмма работы блока 1-1, приведены генерируемые им сигналы и режимы, сигналы управления блоком 1-1 и номера линий, по которым они теое- даются. На фиг. 3 - приведена функциональная схема блока 1-1.

Как показано на фиг. 2, различные звенья ЦФ выполняются за разное время. Первое звено выполняется с нулевого по 23-й такт, промежуточное (HP

первое и не последнее в каскаде) с 2-го по 23-е и последнее звено в каскаде с 2-го по . Работа первого эвена отличается тем, что необходимо в АБ 11 записать содержимое входного буферного регистра 6 (вх. отсчет) и весовой коэффициент из регистров 4 или 5, после чего выполняется первый цикл умножения (такты 1-3). В такте 4 в регистр 8 записывается результат произведения, а в АБ 11 записываются Y и а , в тактах 6 и 7 в блок 10 ч место считанного записывается

V

В такте 7 стробируется выпол- Y Г + а Y ие ог -р -м а

о - - г - n-i при этом второе слагаемое в такте 7

по переднему Фронту записывается в акумулятор АБ 11. Последующее выполнение операции ЛБ 11 в&толняется аналогично - в каждом периоде из 4-х тактов осуществляется чтение блоков 9 и 10 и стробирование АБ 11. Практически во всех ЦФ коэффициенты Ь/ в (1) больше единицы, поэтому их удобно масштабировать в системе счисления с фиксированной запятой как 2b| где |b | 1 . Если это не делать, то приходится масштабировать все коэффициенты относительно Ь как максимального, что сужает динамический диапазон вычислительного устройства. Поэтому в алгоритме работы ЦФ введено двойное выполнение операции умножения b.j Y „., . Каждое промежуточное звено начинается с чтения из

блока и из блока 9а , в освободившуюся ячейку блока 10 будет записано , которое в этот момент вычисляется в АБ 11 и в такте 4 записывается в регистр 8. Вычисления последнего .звена отличаются от первого и промежуточного тем, что необходимо считать результат в регистр 8 (такт 27), записать его в блок 10 (такты 28 и 29), после чего АВ 11 готов к обработке следующего канала данных, Блок 1-1 формирует строб переключения канала (такт 30), а если

0

5

0

5

0

5

0

квадратурной модуляции на входе 14 или при условии, что выполняется обработка с квадратурной модуляцией вторым весовым коэффициентом, входной буферный регистр 6 освобождается и готов к приему следующего отсчета. Блок 1-1 при этом во втором такте генерирует сигнал разрешения записи данных во входной буферный регистр 6, который снимается блоком 3 после записи очередного отсчета.

По сигналу строба звена блок 1-1 переходит на второй такт, блок 2 изменяет состояние счетчика 52 звеньев и сравнивает его с входами на входах 17 и 18. Если выполняется короткий цикл фильтрации (выполняются только первые каскады в каждом канале), то при равенстве состояния счетчика 52 звеньев и кода на входе 17 формируется сигнал последнего звена, который запрещает генерацию блоком 1-1 в такте 24 сигнала строба звена и разрешает прохождение тактов 24-29, генерацию в такте 30 строба канала обработки. Если разрешена квадратурная модуляция, то происходит переключение триггера, который управляет включением в тактах 0 и 1 регистров 4 и 5, блок 1-1 переходит на нулевой такт. Если выполнялась обработка последнего канала, то блок 1-1 формирует в такте 30 сигнал сброса обработки. По этому сигналу происходит -изменение состояния счетчика 54 циклов обработки блока 2 и сравнение его с кодом промежуточного прореживания на входе 19. Если они равны, то следующий цикл обработки всех

каналов будет полный - фильтрация данных во всех каналах будет осуществляться двумя каскадами.

По окончании полного цикла обра- 5 ботки происходит изменение счетчика 55 полных циклов блока 2, состояние которого сравнивается с кодом повторного прореживания на входе 21. При условии равенства блок 2 форми

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Многочастотный цифровой фильтр | 1987 |

|

SU1474827A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для формирования и обработки гистограмм | 1989 |

|

SU1755296A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Устройство для обработки и регистрациидАННыХ СЕйСМичЕСКиХ КОлЕбАНий | 1979 |

|

SU842828A1 |

Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки сигналов. Цель изобретения - повышение точности фильтрации и быстродействия. Цифровой фильтр (ЦФ) содержит блок 1 управления, регистры 4 и 5 коэффициентов, буферные регистры 6 и 7, регистр 8, блок 9 памяти коэффициентов, блок 10 памяти данных, арифметический блок 11. ЦФ по п.2 отличается выполнением блока 1 управления из блока 1 - 1 синхронизации, блока 2 управления каналами обработки и блока 3 управления обменом данных. Повышение точности фильтрации и быстродействия достигается введением буферных регистров 6 и 7, регистров 4 и 5 коэффициентов, их соединением с узлами ЦФ и выполнением блока управления. 1 з.п. ф-лы, 5 ил.

обрабатывается последний канал - сиг- эд рует сигнал разрешения записи результата в выходной буферный регистр 7. При вычислении последнего звена блок 1-1 в такте 27 осуществляет запись с выхода АБ 11 результата в этот ре- 55 гистр 7. По окончании промежуточного прореживания счетчик 53 числа коротких циклов блока 2 переходит в исходное состояние, по окончании повторного прореживания счетчик 54 полнал сброса обработки. После первого звена и каждого промежуточного в такте 24 блоком 1-1 формируется сигнал переключения звена. При выполнении первого звена в тактах 0 и 1 осуществляется чтение входного отсчета из буферного регистра 6 и запись его в АБ 11, после этого, при условии, что нет сигнала разрешения

ных циклов также переходит в исходное состояние.

При вычислении каждого биквадратн го эвена в соответствии с (1) в опер циях участвуют отсчеты , , Y и , которые считыгзаются из блока 10. При этом происходит в тактах 6 и 7 запись Y Ј на место Y и в следующем цикле вычисления (коротком или полном) ячейка памяти с Y „ будет выступать как , a ячейка с как Y . Поэтому для

П 1П-L

различения ячеек памяти вводится сигнал четности цикла обработки. Если цикл четный, то младший адрес ячеек памяти , - равен нулю, а Y n, , Y - единице, в нечетном - наоборот. При переходе от цикла к циклу сигнал четности меняется. Так как первый и второй каскады участвуют в работе с разной частотой, то дл каждого из них необходим свой сигнал четности. Четность первого каскада

(41)изменяется по каждому сигналу сброса обработки, четность второго

(42)- по сигналу сброса полных циклов.

На фиг. 2 приведен график изменения младшего адреса блока 10 в зависимости от четности. Сплошная линия для , пунктирная . Переключение с 4 1 на Ч 2 происходит при переходе с первого каскада на второй что осуществляет блок 2. Данные для каждого канала в блоках 9 и 10 определяют состоянием соответствующих счетчиков блока 2, выходы которых 32 подключены к адресным входам блоков 9 и 10. В каждом цикле вычисления звена, начиная с такта 12 и 23 (29 для последнего звена), адрес ячеек блока 10 должен быть увеличен на единицу по сравнению с состоянием счетчика звеньев, определяющего индекс -1. Это операция выполняется микро- оограммным блоком 1-1 , поэтому код

-,ена из блока 2 через выход 16 передается в блок 1-1. Адресные разряды, соответствующие коду звена, передаются блоку 10 по выходу 29, блоку 9 по выходу 32.

Для обеспечения максимальной пропускной способности предлагаемого ЦФ обмен данными ЦФ с АЦП ,- генератором весовых коэффициентов асинхронный. Управление обменом осуществляется блоком 3. По импульсу частоты дискретизации на входе 25 устанавли

5

0

5

0

5

вается запрос записи данных, по сигналу Пуск на входе 23 устанавливается разрешение записи во входной буферный регистр 6, который разрешает блоку 3 с помощью второй тактовой частоты на входе 24 формировать сигнал чтения каналов данных и записи входного отсчета во входной буферный регистр 6. После записи сигнал разрешения снимается, формируется сигнал разрешения работы, который с первого выхода 15 передается блоку 1-1 синхронизации. После обработки входного отсчета блок 1-1 формирует сигнал разрешения записи следующего отсчета. При этом блок 3 изменяет состояние счетчика каналов обработки и таким образом управляет считыванием данных из каналов данных через выход 37. После записи в регистр 6 отсчета последнего канала блок 3 снимает сигнал запроса записи и через выход 37 разрешает АЦП запись следующих отсчетов в буферные регистры АЦП. Это предусмотрено для того, чтобы не Произошло сбоя в результате того, что период тактовой частоты дискретизации на входе 25 может быть меньше полного цикла обработки и в буферы АЦП могут быть записаны следующие отсчеты, в то время как текущие еще не сосчитаны в ЦФ для обработки. Для правильной организации работы ЦФ соотношение периода частоты дискретизации Т, и времени обработки t биквадратного звена должно быть следующее

40

V k t(k- 1)

Р + Pt , (2)

5

0

5

где п - число каналов;

k - коэффициент промежуточного прореживания;

р - число звеньев в первом каскаде;

рг - общее число звеньев.

Более точное соотношение Т3и t

о о

можно получить, подсчитав число тактов tc первой частоты синхронизации на входе 13 в каждом звене, тогда (Oj:i)Eji.i.Et . 2).22Для согласования работы ЦФ с пог- л дующими устройствами обработки, подключенными к его выходу 41, предусмотрен сигнал готовности данных

52

ЦФ, который устанавливается блоком 3 по заднему фронту сигнала записи в выходной буферный регистр 7, который формирует блок 1-1.

Блоки 1-1, 2 и 3 предназначены дл реализации временной диаграммы (фиг. 2) и управления арифметическим узлами ЦФ (фиг. 1). Примеры их реализации приведены на Фиг. 3-5, pa- ботают они следующим образом. Если во входной буферный регистр 6 не принят отсчет обрабатываемого сигнала, то триггер 77 находится в нулевом состоянии и через элемент ИЛИ 44 бло- кирует работу счетчика 42. После записи во входной буферный регистр 6 отсчета сигнала триггер 77 переходит в единицу и разрешает работу счетчику 42 синхронно с первгг , Ь-- -ОБ,Ч частотой на входе 13 блока , ки:ход счетчика 42 подключен к адресному входу блока 43, который в соответствии с другими адресными входами форг мирует последовательность микроинст- рукций управления арифметическим блоком 11, регистрами 4-8, блоками 9 и 10 (фиг. 2). По окончании выполнения операций одного звена блок 43 формирует сигнал строба переключения зве- на, который устанавливает счетчик 42 в состояние 2 и дальнейшая обработка начинается с второго такта. Если обрабатывалось последнее звено, то блок 43 формирует сигнал строба канала обработки, который сбрасывает счечик 42 и переключает триггер 48 в инверсное текущему состояние при условии, что вход 14 блока 1-1 установлен в состояние лог. единицы, что означает квадратурную модуляцию сигнала. Следующий цикл обработки вход ного отсчета будет осуществляться с учетом умножения его на второй коэффициент, который находится в регистре 5 (первый записан в регистре 4).

Подсчет числа биквадратных звеньев цифрового фильтра осуществляет счетчик 52 блока 2, блок 56 сравнения сравнивает состояние счетчика 52 с кодом на входе 17 числа звеньев и в первом каскаде. Если их состояния . равны, то на выходе блока 56 сравнения появится активный уровень сигнала, который через элемент 2-2И-ИЛИ 61 передается на выход 16 (при условии, что триггер 70 находится в нуле) . По заднему фронту этого сигнала срабатывает формирователь 65, который

Q 5 0 5 0

0

5

0

5

5

сбрасывает счетчик 52. Подсчет обрабатываемых каналов данных выполняет счетчик 53, блок 58 сравнения сравнивает его состояние с кодом числа ка-( налов обработки на входе 20. Если они равны, то на выходе блока 59 сравнения формируется признак последнего канала. По заднему фронту этого сигнала формирователь 64 генерирует импульс, сбрасывающий счетчик 53 и счетчик 54 числа циклов обработки. Выход счетчика 53, объединенный с выходом счетчика 52, подключен к выходу 32 блока 2 и к вторым адресным входам блоков 9 и 10. Он определяет адресное разделение блоков 9 и 10 по каналам обработки. Адресное разделение блока 10 по звеньям, а также адресация отдельных операндов выполняется с помощью счетчика 52 звеньев и блока 43 посредством части кода микроинструкции на выходе 29. Блок 59 сравнения сравнивает состояние выхода счетчика 54 с кодом промежуточного прореживания на входе 19; Если они равны, то на выходе блока 59 сравнения появляется активный уровень сигнала, который устанавливает триггер 70 и сбрасывает счетчик 54. Триггер 70 переключает элемент 2-2И-ИЛИ 61 так, что признак последнего звена на выходе 16 будет равен выходу блока 57 сравнения, который сравнивает состояние счетчика 52 с кодом общего числа звеньев на входе 18 в первом и втором каскадах цифрового фильтра. Установка триггера 70 в состояние единицы означает, что следующий цикл обработки по всем каналам полный, т.е. состоит из двух каскадов звеньев цифрового Фильтра. По окончании каждого цикла обработки триггер 68 изменяет свое состояние на инверсное, триггер 69 изменяет свое состояние на инверсное после каждого полного цикла обработки. Эти триггеры формируют признаки четности (Ч 1 и Ч 2 на фиг. 2) циклов обработки соответственно первым и вторым каскадами цифрового фильтра. Блок 2-2И-ИЛИ 62 коммутирует эти признаки по состоянию второго выхода блока 56 сравнения, который устанавливается в состояние лог. единицы, когда код счетчика 52 больше кода на входе 17, т.е. выполняется второй каскад. Признаки четности используются блоком 43 для формирования адресов при выполнении операций в соответствии с выражением (1). Счетчик 55 осуществляет подсчет полных циклов обработки, его состояние сравнивается блоком 60 сравнения с кодом повторного прореживания на входе 21, если они равны, то формируется сигнал, разрешающий запись результата фильтрации в выходной буферный регистр 7, по зад- нему фронту этого сигнала формирователь 66 сбрасывает счетчик 55.

По каждому фронту частоты дискретизации на входе 25 блока 3 управления обменом данных устанавливается триггер 71 и Формирует сигнал запроса записи данных во входной буферный регистр 6. Если сброшен триггер 72, то формирователь 82 генерирует сигнал записи отсчета входного сигнала, ко- торый передается на тактовый вход входного буферного регистра 6. При этом по состоянию счетчика 67 дешифратор 88 на одном из выходов 37 формирует сигнал чтения отсчета сигнала с определенного информационного канала. Сигнал с выхода формирователя 82 устанавливает триггеры 72, 76 и 77. Триггер 77 разрешает работу блоку 1-1, который после выполнения опера- ций с входным отсчетом генерирует синал разрешения записи следующего отсчета во входной буферный регистр 6. Этот сигнал сбрасывает триггеры 72 и 76, запускает формирователь 82. По заднему фронту сигнала с выхода формрователя 82 счетчик 87 изменяет свое состояние и с помощью дешифратора 88 подключается следующий канал данных. Состояние счетчика 87 сравнивается блоком 89 сравнения с кодом числа каналов на входе 22. При равенстве формируется активный уровень сигнала, п заднему фронту которого формировател 84 генерирует импульс и сбрасывает триггер 71 и счетчик 87, после чего запись отсчетов из каналов данных прекращается. При обработке последнего канала сигнал с выхода 31 сбросит триггер 76 и, если после этого последует сигнал сброса обработки, то он установит в ноль триггер 77 и блокирует работу блока 1-1 синхронизации. Если следующий фронт частоты дискретизации на входе 25 поступит до этого сигнала, то триггер 76 установится в единицу и не сбросится триггер 77, обработка данных продолжится.

Триггер 73 устанавливается в единицу по фронту сигнала с входа 26 блока 3, который синхронизирует смену весовых множителей в регистрах 4 и 5. Смена множителей разрешается при условии,что обрабатывается последний канал и установлен сигнал разрешения записи во входной буферный регистр 6. При этом осуществляется установка триггера 74 в ноль и посредством элемента И 81 устанавливается триггер 75, который разрешает синхронно с тактовой частотой на входе 24 генерировать два сигнала чтения множителей на выходе 37 и два сигнала записи в регистры 4 и 5 на выходе 35 соответственно. Сигнал с выхода формирователя 82 устанавливает триггер 74 и запрещает смену множителей до завершения обработки отсчетов всех каналов. i

Для синхронизации чтения данных

из выходного буферного регистра 7 можно использовать так овый сигнал записи результатов в данный регистр, который входит в состав кода микроинструкции на выходе 29. Данный сигнал с выхода 31 можно подключить на выход 37 управления внешними устройствами ЦФ. Устройство приема данных по этому сигналу формирует сигнал на вход 27 запроса данных, который посредством выхода 36 может подключать выходной буферный регистр 7 на выход 41.

Формула изобретения

входы которых являются первым входом цифрового фильтра, вторым входом которого является вход входного буферного регистра, выход которого соединен с вторым входом арифметического блока, первый вход которого соединен с выходами первого и второго регистров коэффициентов, а выход арифметического блока соединен с входом выходного буферного регистра, выход которого является выходом цифрового фильтра, управляющими входами с первого по двенадцатый которого явпяются соответствующие входы блока управления, соответствующие выходы первой группы которого соединены с первыми управляющими входами вх чного и выходного буферных регистре . пег РОГо ч второго регистров коэф( п i г ч БТ - рые управляющие входы которых нены с вторым выходом блока управления, третий выход которого соединен с вторыми управляющими входами блоков памяти данных и коэффициентов, четвертый выход блока управления соеди- нен с вторым управляющим входом входного буферного регистра, пятый и шестой выходы блока управления являются первым и вторым управляющими выходами цифрового фильтра, причем первый из них соединен с вторым управляющим входом выходного буферного регистра.

6996614

ния, содержащий блок синхронизации, первый вход и группа первых выходов которого является первым входом и группой первых выходов блока управ- ления, введены блок управления каналами обработки и блок управления обменом данных, первый выход которого соединен с вторым входом блока

П синхронизации, третий вход которого является вторым входом блока управления, входами с третьего по седьмой которого являются входы с первого по пятый блока управления каналами

15 обработки соответственно, шестой

вхо-д которого соединен с вторым выходом блока синхронизации, четвертый вход которого соединен с первым выходом блока управления каналами обД) работки, второй выход которого является третьим выходом блока управления, четвертым, вторым, пятым и шестым выходами которого являются второй, третий, четвертый и пятый выходы бло25 ка управления обменом данных соответственно, входы с первого по шестой которого являются входами с восьмого по тринадцатый блока управления соответственно, а третий выход блока упJQ равлеиия каналами обработки соединен с седьмым входом блока управления обменом данных, второй и восьмой входы которого соединены с пятым входом и третьим выходом блока синхронизации соответственно.

IS

16

| Патент США № 4117541, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-04-12—Подача