Изобретение относится к технике встроенного аптоматизнрованного контроля и может быть использовано для контроля различных цифровых блоков в качестве генераторов теста и ана- лизаторов.

Цель изобретения - расширение области применения устройства путем обеспечения возможности работы в анализаторных режимах генератора инкре- ментщ) последовательных состояний, а также обеспечения возможности работы с изменением разрядности и длительности псевдослучайной последовательности состояний.

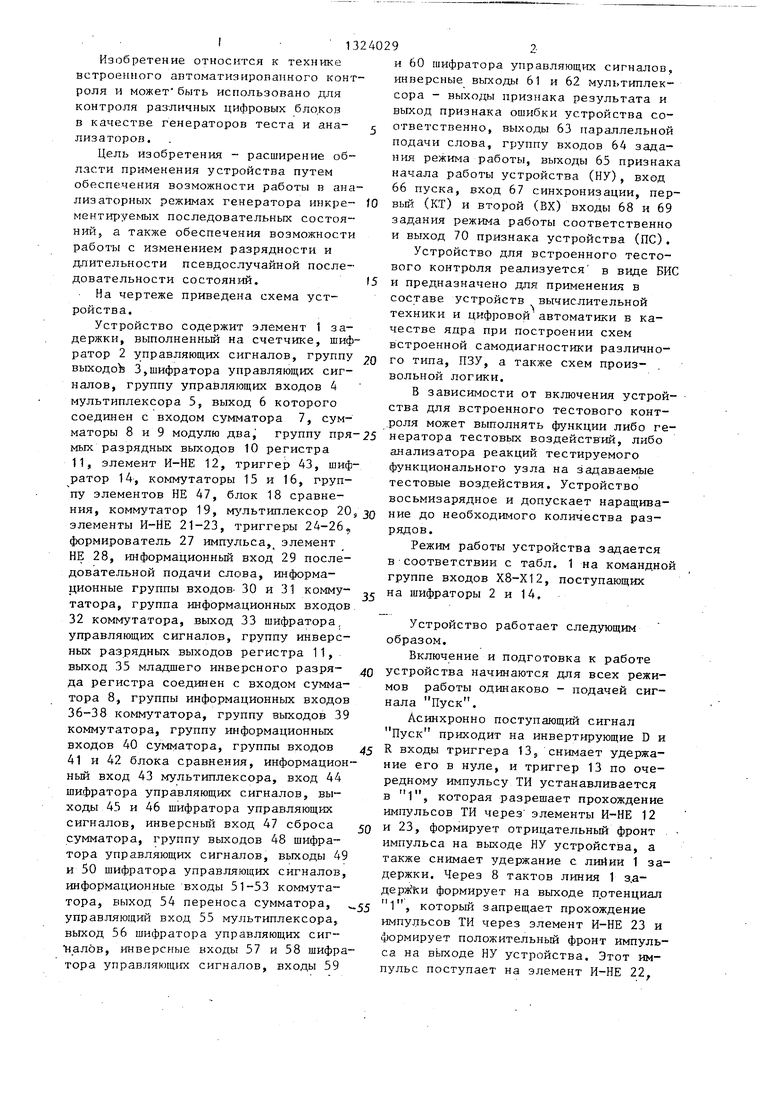

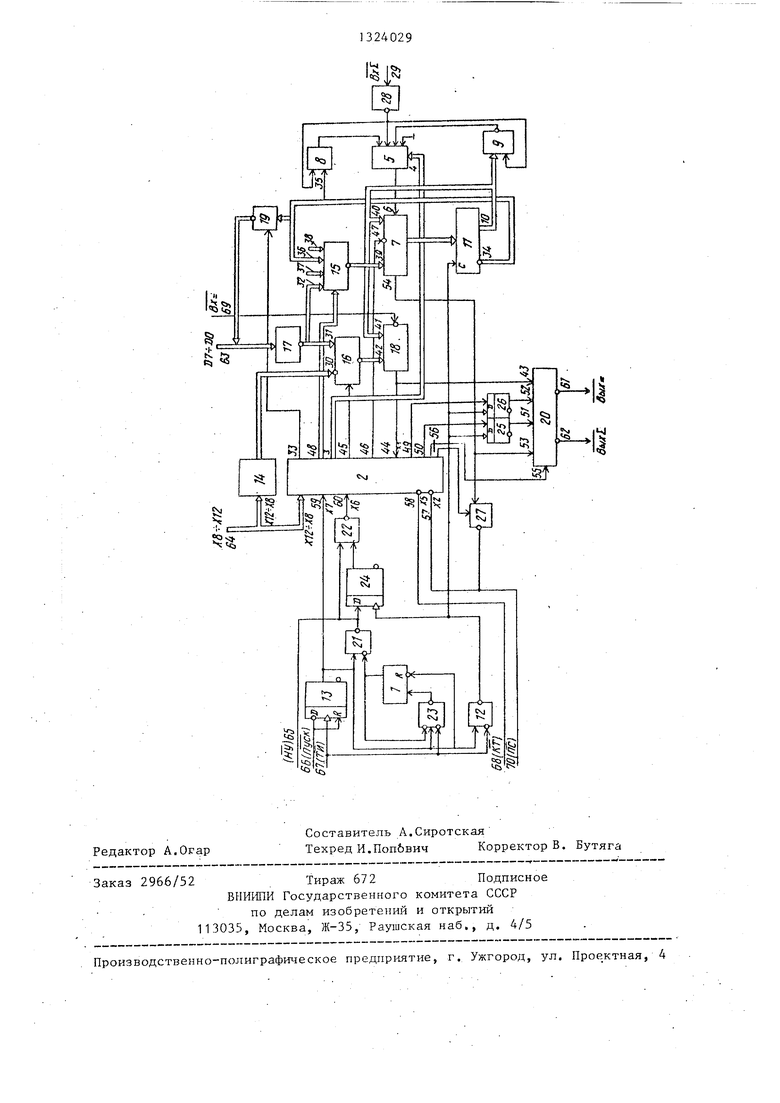

На чертеже приведена схема устройства.

Устройство содержит элемент 1 задержки, выполненный на счетчике, шифратор 2 управляющих сигналов, группу выходов 3,шифратора управляющих сигналов, группу управляющих входов А мультиплексора 5, выход 6 которого соединен с входом сумматора 7, сум

В зависимости от включения устройства для встроенного тестового контроля может выполнять функции либо геанализатора реакции тестируемого функционального узла на задаваемь1е тестовые воздействия. Устройство восьмизарядное и допускает наращиваматоры 8 и 9 модулю два группу пря-25 нератора тестовых воздейств ий, либо мых разрядных выходов 10 регистра 11, элемент И-НЕ 12, триггер 43, шифратор 14, коммутаторы 15 и 16, группу элементов НЕ 47, блок 18 сравнения, коммутатор 19, м льтиплексор 20, зо ние до необходимого количества раз- элементы И-НЕ 21-23, триггеры 24-26,, рядов.

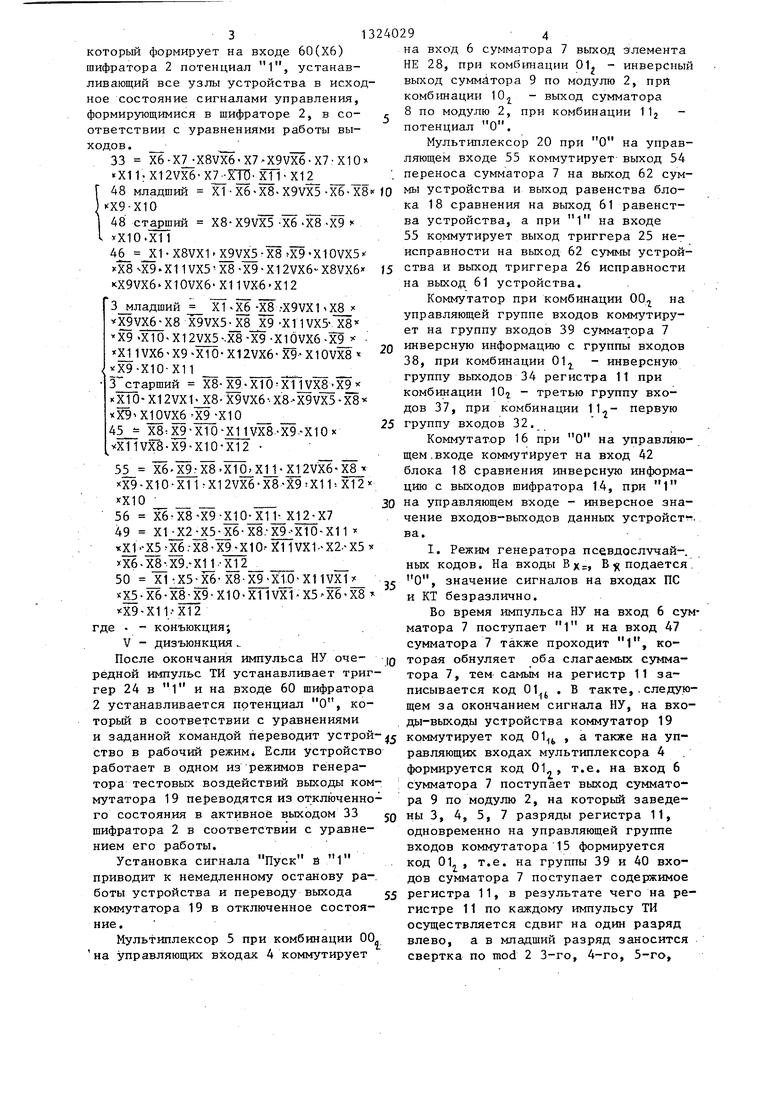

формирователь 27 импульса, элемент Режим работы устройства задается НЕ 28, информационный вход 29 после- всоответствии с табл. 1 на командной довательной подачи слова, информа- группе входов Х8-Х12, поступающих ционные группы входов- 30 и 31 комму- на шифраторы 2 и 14. татора, группа информационных входов

32 коммутатора, выход 33 шифратора, управляющих сигналов, группу инверсных разрядных выходов регистра 11, выход 35 младшего инверсного разряда регистра соединен с входом сумматора 8, группы информационных входов 36-38 коммутатора, группу выходов 39 коммутатора, группу информационных входов 40 сумматора, группы входов 41 и 42 блока сравнения, информацион- ньй вход 43 мультиплексора, вход 44 шифратора управляющих сигналов, выходы 45 и 46 шифратора управляющих сигналов, инверсный вход 47 сброса сумматора, группу выходов 48 шифратора управляющих сигналов, выходы 49 и 50 шифратора управляющих сигналов, информационные входы 51-53 коммутатора, выход 54 переноса сумматора, 55 1 которьш запрещает прохождение управляющий вход 55 мультиплексора, импульсов ТИ через элемент И-НЕ 23 и выход 56 шифратора управляющих сиг- Налов, инверсные входы 57 и 58 шифратора управляющих сигналов, входы 59

формирует положительный фронт импульса на вьгходе НУ устройства. Этот импульс поступает на элемент И-НЕ 22,

го типа

и 60 шифратора управляющих сигналов, инверсные выходы 61 и 62 мультиплексора - выходы признака результата и выход признака ошибки устройства соответственно, выходы 63 параллельной подачи слова, группу входов 64 задания режима работы, выходы 65 признака начала работы устройства (НУ), вход 66 пуска, вход 67 синхронизации, пер- вьш: (КТ) и второй (ВХ) входы 68 и 69 задания режима работы соответственно и выход 70 признака устройства (ПС). Устройство для встроенного тестового контроля реализуется в виде БИС и предназначено для применения в составе устройств вычислительной техники и цифровой автоматики в качестве ядра при построении схем встроенной самодиагностики различно- ПЗУ, а также схем произго типа

вольной логики.

В зависимости от включения устройства для встроенного тестового контроля может выполнять функции либо генератора тестовых воздейств ий, либо ние до необходимого количества раз- рядов.

анализатора реакции тестируемого функционального узла на задаваемь1е тестовые воздействия. Устройство восьмизарядное и допускает наращиванератора тестовых воздейств ий, либо ние до необходимого количества раз- рядов.

Устройство работает следующим образом.

Включение и подготовка к работе

устройства начинаются для всех режимов работы одинаково - подачей сигнала Пуск.

Асинхронно поступающий сигнал Пуск приходит на инвертирующие D и

R входы триггера 13, снимает удержание его в нуле, и триггер 13 по очередному импульсу ТИ устанавливается в 1, которая разрешает прохождение импульсов ТИ через элементы И-НЕ 12

и 23, формирует отрицательный фронт импульса на выходе НУ устройства, а также снимает удержание с лийии 1 задержки. Через В тактов линия 1 з.а- формирует на выходе потенциал

1 которьш запрещает прохождение импульсов ТИ через элемент И-НЕ 23 и

формирует положительный фронт импульса на вьгходе НУ устройства. Этот импульс поступает на элемент И-НЕ 22,

которьй формирует на входе 60(Х6) шифратора 2 потенциал 1, устанавливающий все узлы устройства в исходное состояние сигналами управления, формирующимися в шифраторе 2, в со- ответствии с уравнениями работы выходов.

33 Х6-X7jX8VX6Х7 Х9УХ6Х7 Х10

Х11;Х12УХ6 Х7 Х1ГО-Х1 1-Х12

48 младший Х1Х6-Х8.X9VX5-Хб- В

Xg-XIO

48 ставший X8-X9VX5 -Хб.Х8-ХЭ

ХХ10.Х11

46 X1 X8VX1 X9VX5-X8 X9X10VX5 Х8 -Х9«X11VX5 Х8 Х9 XI2VX6-- X8VX6 KX9VX6 X10VX6 X11VX6 X12

То V 20

25

3 младший ХЬХб -Х8 .X9VXbX8j X9VX6 X8 X9VX5- X8 JC9 -Xl 1VX5- X8 X9«X10.X12VX5-.X8-X9-X16VX6-X9J Xl 1VX6 X9 -XIO- X12VX6- X9- X10VX8

X9-X10-X11

З старший X8-X9-X10 X1J VX X9j

XXJO-X12VX1OC8-X9VX6-.X8--X9VX5-X8

X9 X9jX10

45 - X8 X9-X10-X11VX8.-X9-X1Qx

VX11VX8-X9-X10-X12

55 .-X8 XTO X11-X12VX6 X8 XX9-X10X11:XI2VX6X8X9 Xl1 X12 x

XX10 ;

56 X6-X8-X9-X10-X11- X12-X7

49 X1 2-X5-X6-X8,-X9--X10-X11 «X1--X5 X6;X8-X9-X10 XI 1VX1.-X2.-X5 X6..-X1J.-)

50 XI :X5-X6-X8-X9-X1.0-X11VX1 Х5-Хб-Х8уХ9-Х10-Х11УХ1 Х5 Хб Х8 X9-X11-X12

де . - конъюкция ,

V - дизъюнкция ..

После окончания импульса НУ очеёдной импульс ТИ устанавливает тригер 24 в 1 и на входе 60 шифратора устанавливается потенциал О, коорый в соответствии с уравнениями

30

эг

.10

и заданной командой переводит устрой- коммутирует код 01 , а также на уп50

ство в рабочий режим Если устройство работает в одном из режимов генератора тестовых воздействий выходы коммутатора 19 переводятся из отключенного состояния в активное вькодом 33 шифратора 2 в соответствии с уравнением его работы.

Установка сигнала Пуск в 1 приводит к немедленному останову ра-. боты устройства и переводу выхода 55 коммутатора 19 в отключенное состояние.

Мультиплексор 5 при комбинации 00- на управляющих входах 4 коммутирует

равняющих входах мультиплексора 4 формируется код 01 , т.е. на вход 6 сумматора 7 поступает выход сумматора 9 по модулю 2, на который заведены 3, 4, 5, 7 разряды регистра 11, одновременно на управляющей группе входов коммутатора 15 формируется код 01, , т.е. на группы 39 и 40 входов сумматора 7 поступает содержимое регистра 11, в результате чего на регистре 11 по каждому импульсу ТИ осуществляется сдвиг на один разряд влево, а в младший разряд заносится свертка по mod 2 3-го, 4-го, 5-го,

г

13240294

на вход 6 сумматора 7 выходэлемента

НЕ 28, при комбинации 01, -инверсный

вькод суммйтора 9 по модулю2, при

г

O

комбинации lOj - выход сумматора

5

0

5

8 по модулю 2, при комбинации 112 - потенциал О.

Мультиплексор 20 при О на управляющем входе 55 коммутирует- выход 54 переноса сумматора 7 на выход 62 суммы устройства и выход равенства блока 18 сравнения на выход 61 равенства устройства, а при 1 на входе 55 коммутирует выход триггера 25 неисправности на выход 62 суммы устройства и выход триггера 26 исправности на выход 61 устройства.

Коммутатор при комбинации 00 на управляющей группе входов коммутирует на группу входов 39 сумматора 7 инверсную информацию с группы входов 38, при комбинации 01 - инверсную группу выходов 34 регистра 11 при комбинации Юг - третью группу входов 37, при комбинации 11-,- первую группу входов 32.

Коммутатор 16 при О на управляющем, входе коммутирует на вход 42 блока 18 сравнения инверсную информацию с выходов шифратора 14, при 1 0 на управляющем входе - инверсное значение входов-выходов данных устройст . ва,

I. Режим генератора псевдослучай-, ных кодов. На входы BX, Б подается . эг О, значение сигналов на входах ПС и КТ безразлично.

Во время импульса НУ на вход 6 сумматора 7 поступает 1 и на вход 47 сумматора 7 также проходит 1, которая обнуляет оба слагаемых сумматора 7, тем самым на регистр 11 записывается код . В такте, . следующем за окончанием сигнала НУ, на вхо- ды-вькоды устройства коммутатор 19

.10

равняющих входах мультиплексора 4 формируется код 01 , т.е. на вход 6 сумматора 7 поступает выход сумматора 9 по модулю 2, на который заведены 3, 4, 5, 7 разряды регистра 11, одновременно на управляющей группе входов коммутатора 15 формируется код 01, , т.е. на группы 39 и 40 входов сумматора 7 поступает содержимое регистра 11, в результате чего на регистре 11 по каждому импульсу ТИ осуществляется сдвиг на один разряд влево, а в младший разряд заносится свертка по mod 2 3-го, 4-го, 5-го,

7-го разрядов. Таким образом реализуется 8-разрядньм генератор псевдослучайной последовательности.

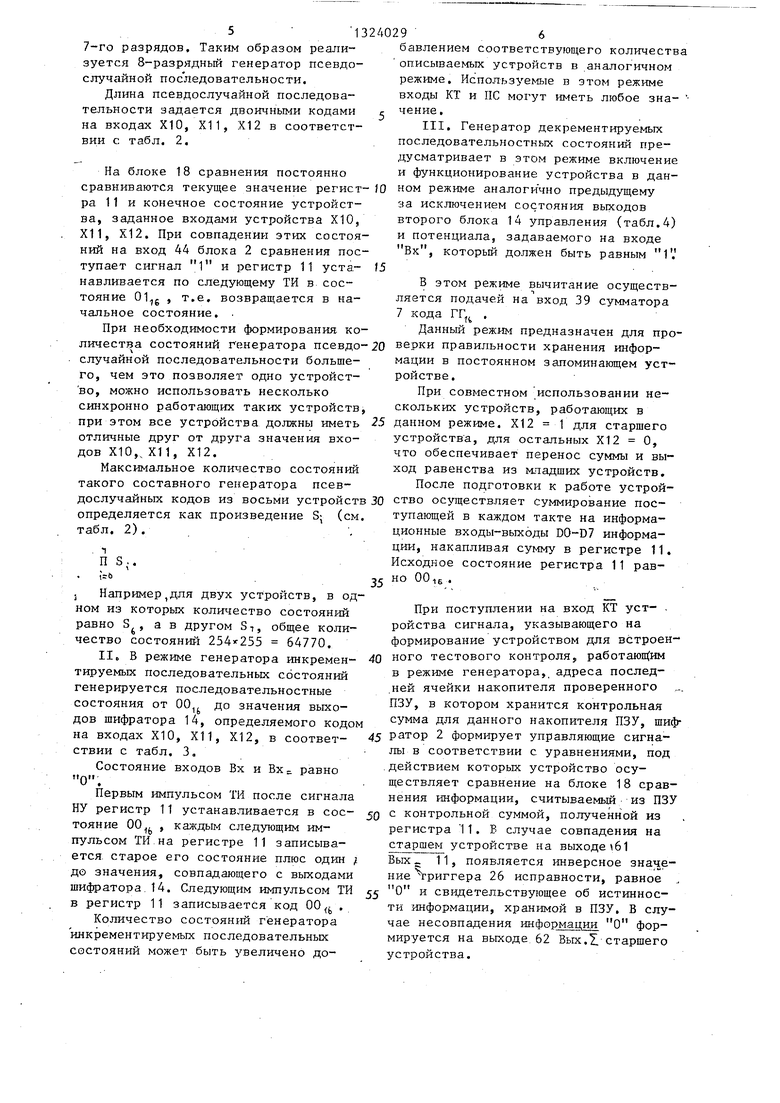

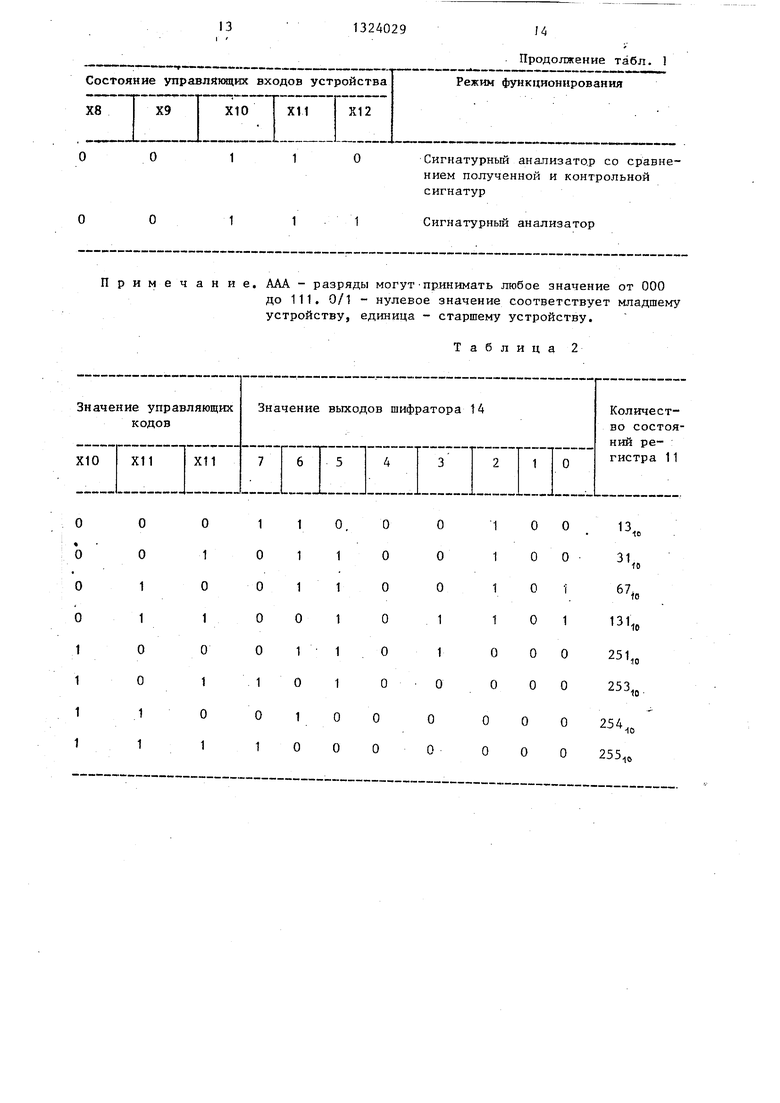

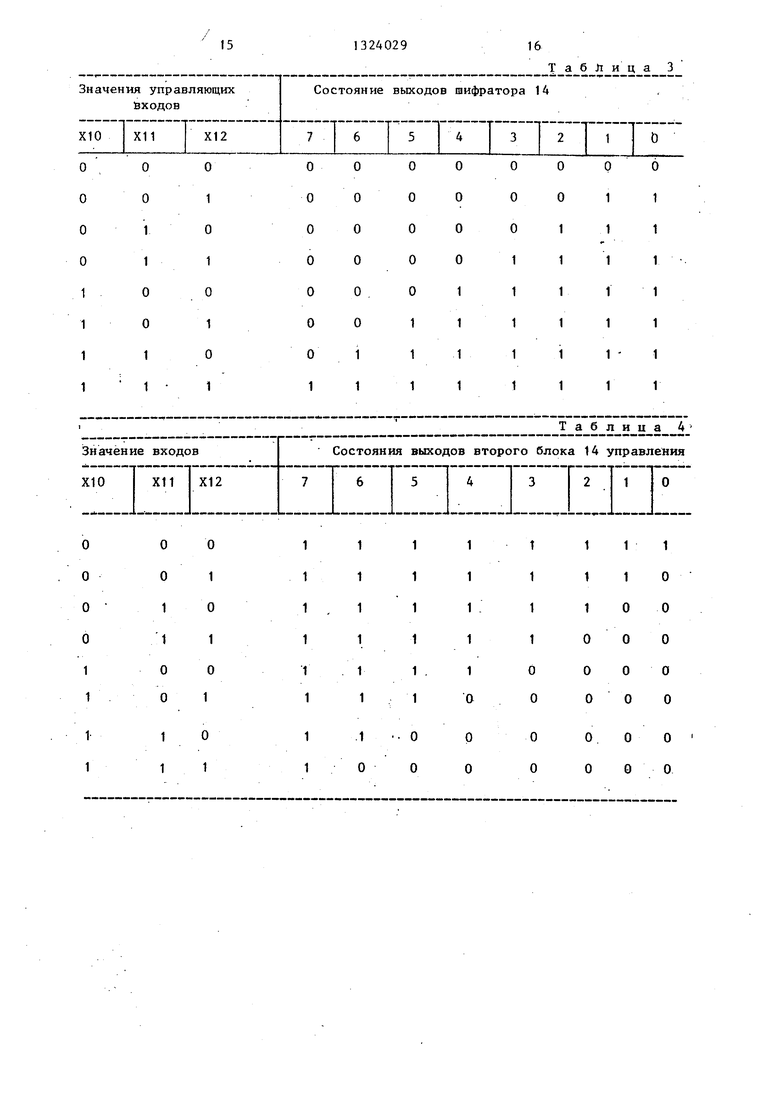

Длина псевдослучайной последовательности задается двоичными кодами на входах Х10, XI1, XI2 в соответствии с табл. 2.

На блоке 18 сравнения постоянно

сравниваются текущее значение регист- (О ном режиме аналогично предыдущему

ра 11 и конечное состояние устройства, заданное входами устройства Х10, Xll, XI2. При совпадении этих состояний на вход 44 блока 2 сравнения поступает сигнал 1 и регистр 11 уста- f5 навливается по следующему ТИ в состояние 01., , т.е. возвращается в наза исключением состояния выходов второго блока 14 управления (табл.4) и потенциала, задаваемого на входе Вх, который должен быть равным iV

В этом режиме вычитание осуществляется подачей на вход 39 сумматора 7 кода ГГ, .

Данный режим предназначен для проi g , т.е. возвращается чальное состояние. .

При необходимости формирования количества состояний Генератора псевдо-20 верки правильности хранения инфор- случайной последовательности больше- мадии в постоянном запоминающем уст- го, чем это позволяет одно устройст- ройстве.

во, можно использовать несколько При совместном использовании несинхронно работающих таких устройств, скольких устройств, работающих в при этом все устройства должны иметь 25 данном режиме. Х12 1 для старшего отличные друг от друга значения вхо- устройств а, для остальных XI2 О, дов Х10,, XII, Х12.что обеспечивает перенос суммы и выход равенства из младших устройств.

После подготовки к работе устрой- дослучайных кодов из восьми устройств 30 ство осуществляет суммирование пос- определяется как произведение S; (см. тупающей в каждом такте на информационные входы-выходы информации, накапливая сумму в регистре 11. Исходное состояние регистра 11 равно OOiE .

Максимальное количество состояний такого составного генератора псевтабл. 2).

П S ; .

I rb

i Например,ДЛЯ двух устройств, в одном из которых количество состояний равно S, а в другом Si, общее количество состояний 64770.

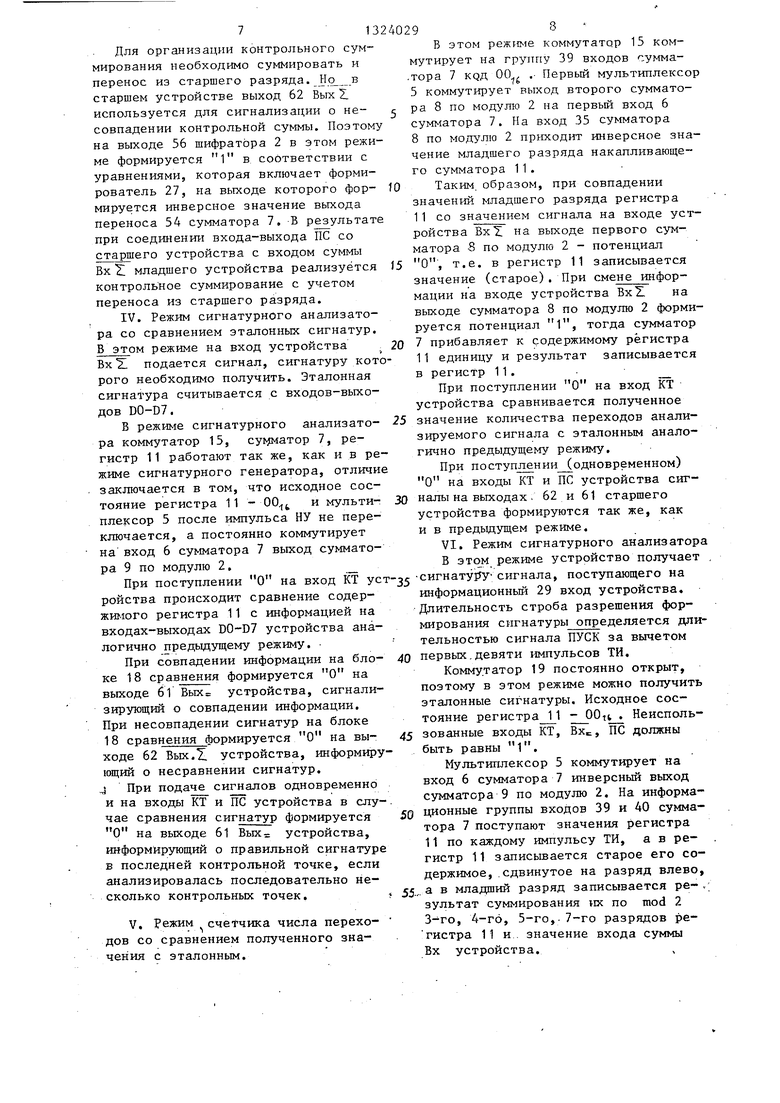

Но В режиме генератора инкремен- тируемых последовательных состояний генеррфуется последовательностные состояния от 00, до значения выходов шифратора 14, определяемого кодом на входах Х10, XI1, XI2, в соответствии с табл. 3,

Состояние входов Вх и Вх- равно

nil

40

О

Первым импульсом ТИ после сигнала

35

При поступлении на вход КТ уст- . ройства сигнала, указывающего на формирование устройством для встроенного тестового контроля, работаюп им в режиме генератора,, адреса послед- .ней ячейки накопителя проверенного ПЗУ, в котором хранится контрольная сумма для данного накопителя ПЗУ, шиф 45 ратор 2 формщ)ует управляющие сигналы в соответствии с уравнениями, под .действием которых устройство осуществляет сравнение на блоке 18 сравнения информации, считываемый из ПЗУ

НУ регистр 11 устанавливается в сое- Q с контрольной суммой, полученной из

тояние 00 , каждым следующим импульсом ТИ на регистре 11 записывается старое его состояние плюс один f. до значения, совпадающего с выходами шифратора.14. Следующим импульсом ТИ в регистр 11 записывается код 00 . Количество состояний генератора инкрементируемых последовательных состояний может быть увеличено до55

регистра 11. Б случае совпадения на старшем устройстве на выходе б1 Вых 11, появляется инверсное значе ние триггера 26 исправности, равное О и свидетельствующее об истинности :информации, хранимой в ПЗУ. В слу чае несовпадения информации О формируется на выходе. 62 Вых. старшего устройства.

бавлением соответствующего количества описываемых устройств в аналогичном режиме. Используемые в этом режиме входы КТ и ПС могут иметь любое зна- чение.

III. Генератор декрементируемых последовательностных состояний предусматривает в этом режиме включение и функционирование устройства в данза исключением состояния выходов второго блока 14 управления (табл.4) и потенциала, задаваемого на входе Вх, который должен быть равным iV

В этом режиме вычитание осуществляется подачей на вход 39 сумматора 7 кода ГГ, .

Данный режим предназначен для проверки правильности хранения инфор- мадии в постоянном запоминающем уст- ройстве.

После подготовки к работе устрой- 30 ство осуществляет суммирование пос- тупающей в каждом такте на информационные входы-выходы информации, накапливая сумму в регистре 11. Исходное состояние регистра 11 равно OOiE .

40

35

При поступлении на вход КТ уст- . ройства сигнала, указывающего на формирование устройством для встроенного тестового контроля, работаюп им в режиме генератора,, адреса послед- .ней ячейки накопителя проверенного ПЗУ, в котором хранится контрольная сумма для данного накопителя ПЗУ, шиф 45 ратор 2 формщ)ует управляющие сигналы в соответствии с уравнениями, под .действием которых устройство осуществляет сравнение на блоке 18 сравнения информации, считываемый из ПЗУ

5

регистра 11. Б случае совпадения на старшем устройстве на выходе б1 Вых 11, появляется инверсное значение триггера 26 исправности, равное , О и свидетельствующее об истинности :информации, хранимой в ПЗУ. В случае несовпадения информации О формируется на выходе. 62 Вых. старшего устройства.

15

Для организации контрольного суммирования необходимо суммировать и перенос из старшего разряда. Но в старшем устройстве выход 62 Вых 2. используется для сигнализации о не- совпадении контрольной суммы. Поэтому на выходе 56 шифратора 2 в этом режиме формируется 1 в соответствии с уравнениями, которая включает формирователь 27, на выходе которого фор- 10 мируется инверсное значение выхода переноса 54 сумматора 7, В результате при соединении входа-выхода ПС со старшего устройства с входом суммы Вх 21 младшего устройства реализуется контрольное суммирование с учетом переноса из старшего разряда.

IV. Режям сигнатурного анализатора со сравнением эталонных сигнатур. В этом режиме на вход устройства ВхX подается сигнал, сигнатуру которого необходимо получить. Эталонная сигнатура считывается с входов-выходов DO-D7.

В режиме сигнатурного анализатора коммутатор 15, суь матор 7, регистр 11 работают так же, как и в режиме сигнатурного генератора, отличие заключается в том, что исходное состояние регистра 11 - 00 и мультиплексор 5 после импульса НУ не переключается, а постоянно коммутирует на вход 6 сумматора 7 выход сумматора 9 по модулю 2.

В этом режиме коммутатор 15 коммутирует на группу 39 входов сумма- .тора 7 кдд ОСХ . Первый мультиплексор 5 коммутирует выход второго сумматора 8 по модулю 2 на первьй вход 6 сумматора 7. На вход 35 сумматора 8 по модулю 2 приход1гг инверсное значение младшего разряда накапливающего сумматора 11.

Таким, образом, при совпадении значений младшего разряда регистра 11 со значением сигнала на входе устПри поступлении О

ройства ВхТ на выходе первого сумматора -8 по модулю 2 - потенциал О, т.е. в регистр 11 записывается значение (старое). При смене инфор- мации на входе устройства BxZ на выходе сумматора 8 по модулю 2 формируется потенциал 1, тогда сумматор 7 прибавляет к содержимому регистра 11 единицу и результат записывается в регистр 11.

При поступлении О на вход КТ устройства сравнивается полученное значение количества переходов анализируемого сигнала с эталонным аналогично предыдущему режиму.

При поступлении (одновременном) О на входы КТ и ПС устройства сигналы на выходах . 62 и 61 старшего устройства формируются так же, как и в предыдущем режиме,

VI. Режим сигнатурного анализатора

В этом режиме устройство получает , на вход КТ уст-35 сигнату11У сигнала, поступающего на

20

25

30

информационный 29 вход устройства. Длительность строба разрешения формирования сигнатуры определяется длительностью сигнала ПУСК за вычетом

ройства происходит сравнение содер- жш.юго регистра 11 с информацией на входах-выходах DO-D7 устройства аналогично предьщущему режиму.

При совпадении информации на блоке 18 сравнения формируется О на выходе б1 ВыХс устройства, сигнализирующий о совпадении информации. При несовпадении сигнатур на блоке 18 сравнения формируется О на выходе 62 Вых.1 устройства, информщ)у ющий о несравнении сигнатур. При подаче сигналов одновременно и на входы W и ПС устройства в случае сравнения сигнатур формируется О на выходе 61 Вых устройства, информирующий о правильной сигнатуре в последней контрольной точке, если анализировалась последовательно несколько контрольных точек.

V, режим счетчика числа перехо- ДОН со сравнением полученного значения с эталонным.

В этом режиме коммутатор 15 коммутирует на группу 39 входов сумма- .тора 7 кдд ОСХ . Первый мультиплексор 5 коммутирует выход второго сумматора 8 по модулю 2 на первьй вход 6 сумматора 7. На вход 35 сумматора 8 по модулю 2 приход1гг инверсное значение младшего разряда накапливающего сумматора 11.

Таким, образом, при совпадении значений младшего разряда регистра 11 со значением сигнала на входе уст15

10

20

25

30

В этом режиме устройство получает , сигнату11У сигнала, поступающего на

информационный 29 вход устройства. лительность строба разрешения формирования сигнатуры определяется длительностью сигнала ПУСК за вычетом

первых.девяти импульсов Тй.

Коммутатор 19 постоянно открыт, поэтому в этом режиме можно получить эталонные сигнатуры. Исходное состояние регистра 1 1 - 00 . Неиспользованные входы КТ, Вх, ПС должны быть равны 1.

Мультиплексор 5 коммутирует на вход 6 сумматора 7 инверсный выход сумматора 9 по модулю 2. На информационные группы входов 39 и 40 сумматора 7 поступают значения регистра 11 по каждому импульсу ТИ, а в регистр 11 записьшается старое его содержимое, .сдвинутое на разряд влево,

а в младший разряд записывается ре- .; зультат суммирования vix по mod 2 3-го, 4-г6, 5-го,.7-го разрядов ре- гистра 11 и. значение входа суммы Вх устройства.,

Таким образом реализуется режим работы сигнатур шго анализатора в устройстве.

VII. Режим счетчика числа переходов .

Этот режим предназначен для получения эталонных значений числа переходов анализируемого сигнала. Сумматор 8 по модулю 2, мультиплексор 5, коммутатор 15, сумматор 7 и регистр 11 работают так же, как и в режиме счетчика числа переходов со сравнением полученного значения с эталонным. В этом режиме открыт коммутатор 19, а коммутатор 16, мультиплексор 20 и блок 18 сравнения не работают.

Таким образом, изобретение обеспе .-i HBaeT работу устройства в режимах генератора псевдослучайных кодов, генератора инкрементируемых последова- тельностных состояний, генератора декрементируемых последовательностньг состояний, счетчика числа переходов, счетчика числа переходов со сравнением полученного значения с эталон- ным, сумматора со сравнением полученной суммы с контрольной, сигнатурного анализатора со сравнением полученной и контрольной сигнатур и сигнатурного анализатора.

Формула изобретения

Устройство для встроенного тестового контроля, содержащее шифратор управляющих сигналов, первьй триггер элемент задержки, выполненный на счетчике, первый элемент И-НЕ, два коммутатора, первый мультиплексор, i- регистр, сумматор, два сумматора по модулю два, причем вход пуска устройства соединен с входом сброса и инверсным первого триггера, выход которого соединен с инверсным входом сброса счетчика, с третьим входом первого элемента И-НЕ, выход которого соединен с синхровходом регистра, информационные входы которого соединены с выходами первого сумматора, первая группа информадион ных входов которого соединена с индексной группой выходов первого коммутатора, разрешающий вход первого сумматора соединен с выходом первого мультиплексора, первый и второй ий- (1юрмационные входы которого соединены прям{ 1м и инверсным выходами перво- го и второго сумматоров по модулю два .соответственно, первая группа выходов и первый выход шифратора управляющих сигналов соединена с группой управляющих входов и управляющим пхо- щом первого и второго коммутаторов соответственно, синхровход устройства соединен с входом первого триггера, группа.прямых разрядных выходов регистра соединена с группой входов первого сумматора по модулю два, третий информационный вход первого мультиплексора подключен к шине нулевого потенциала устройства, первый вход задания режима работы которого соединен с первым инверсным входом шифратора управляющих сигналов, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности работы в анализаторных режимах и в режимах генератора инкрементируемых последо- вательностных состояний, а также обеспечения возможности работы с из- менешием разрядности и длительности псевдослучайной последовательности состояний, оно содержит второй, третий и четвертый триггеры, шифратор, группу элементов НЕ, третий коммутатор, блок сравнения, элемент НЕ, формирователь :нмпульсов, второй, третий и четвертьй элементы И-НЕ и второй мультиплексор, причём синхровход устройства соединен с инверсным входом первого элемента И-НЕ, с первым инверсным входом второго элемента И-НЕ, выход первого элемента И-НЕ соединен с входами второго, третьего и четвертого триггеров, выход перво - го триггера соединен с прямыми входами второго и третьего элементов И-НЕ и первым прямым входом шифратора управляющих сигналов, группа входов которого соединена с группой входов задания режима работы устройства и через шифратор с группой инверсных информационных входов второго коммутатора, группа прямых информационных входов которого соединена с группой выходов элементов НЕ группы и с первой группой информационных входов первого коммутатора, вторая и третья группы информационных входов которого подключены к шинам нулевого и единичного потенциалов устройства соответственно, группа инверсных разрядных выходов регистра соединена.с четвертой группой информационных входов первого коммутатора и через группу информационных входов третьего коммутатора с инверс11

HbtNfo выходами устройства, группа входов элементов НЕ является группой информационных входов параллельной подачи слова устройства, выход второго элемента И-НЕ соединен со счетным входом счетчика задержки, вькод переполнения которого соединен с инверсным входом третьего элемента И-НЕ и с вторым инверсным входом вто132

iporo элемента И-НЕ, выход третьего элемента И-НЕ соединен с D-входом второго триггера, с первым входом четвертого элемента И-НЕ и является выходом признака начала работы устройства, выход четвертого элемента И-НЕ соединен с вторым прямым входом шифратора управляющих сигналов, второй инверсный вход которого соединен с инверсным выходом формирователя импульсов и является выходом переноса устройства, информационный вход формирователя импульсов соединен с выходом переноса первого сумматора и с первым информационным входом втоJO вертого триггеров соответственно, седьмой выход шифратора управляющих сигналов соединен с инверсным входом сброса первого сумматора, третий прямой вход шифратора управлякнцих сигна J5 лов соединен с выходом Равно блока сравнения и с вторьгм информационным входом второго мультиплексора, третий и четвертый информационный входы которого соединены с выходами

20 третьего и четвертого триггеров соответственно, первая группа входов блока сравнения соединена с инверс- ными входами второго коммутатора, вторая группа входов сравнения соерого мультиплексора, первьй и второй 25 динена с группой прямых разрядньк вы- инверсные выходы которого являются выходами признаков результата и ошибки устройства соответственно, инверс- ньй вход разрешения блока сравнения соединен с вторым входом задания ре- 30 жима работы устройства, выход второго триггера соединен с вторым входом четвертого элемента И-НЕ, второй выход шифратора управляющих сигналов соединен с управляющим входом третье-35 го коммутатора, вторая группа выходов шифратора, управляющих сигналов сое-

ходов регистра и с второй группой информационных входов первого сумматора, выход элемента НЕ соединен с входом первого сумматора по модулю два, с первым входом второго сумматора и с четвертым информационным входом первого мультиплексора, вхЬд элемента НЕ является входом последовательной подачи информационного слова, а инверсный выход первого разряда регистра соединен с вторым вхо- ,|дом второго сумматора по модулю два,

Т

О О

О

О

01

10/1

о 0/1

2402912

динена с группой управляющих .входов первого мультиплексора, третий и , четвертый выходы шифратора управляющих сигналов соединены с синхровхо- дом формирователя импульсов и управляющим входом второго мультиплексора соответственно, пятый и шестой выходы шифратора управляющих сигналов соединены с D-входами третьего и четJO вертого триггеров соответственно, седьмой выход шифратора управляющих сигналов соединен с инверсным входом сброса первого сумматора, третий прямой вход шифратора управлякнцих сигна J5 лов соединен с выходом Равно блока сравнения и с вторьгм информационным входом второго мультиплексора, третий и четвертый информационный входы которого соединены с выходами

20 третьего и четвертого триггеров соответственно, первая группа входов блока сравнения соединена с инверс- ными входами второго коммутатора, вторая группа входов сравнения соединена с группой прямых разрядньк вы-

ходов регистра и с второй группой информационных входов первого сумматора, выход элемента НЕ соединен с входом первого сумматора по модулю два, с первым входом второго сумматора и с четвертым информационным входом первого мультиплексора, вхЬд элемента НЕ является входом последовательной подачи информационного слова, а инверсный выход первого разряда регистра соединен с вторым вхо- ,|дом второго сумматора по модулю два,

Т

Генератор инкрементйруемых последовательных состояний

Генератор декрементируемых последовательных состояний

Счетчик числа переходов

Счетчик числа переходов со сравнением полученного значения с эталонным

Сумматор со сравнением полученной суммы с контрольной

Примечание, ААА - разряды могут Принимать любое значение от 000

до 111. 0/1 - нулевое значение соответствует младшему устройству, единица - старшему устройству.

Таблица2

Продолжение табл. 1

Сигнатурный анализатор со сравнением полученной и контрольной сигнатур

Сигнатурньй анализатор

О О

1 1 о о 1 1

о 1

о 1 о 1 о 1

о о о о о о о 1

Таблица 3

о о о о о 1 1 1

о о о о 1 1 1 1

о о о 1 1 1 1 1

о о 1 1 1 1 i 1

о 1 1 1 1 1 1 1

о 1 1 1 1 1 1 1

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

Изобретение относится к технике :встроенного автоматизированного контроля и может быть использовано для контроля различных цифровых блоков. Цель изобретения - расширение функциональных возможностей за счет возможности работы в анализаторных режимах и в режимах генератора гакремен- тируемых последовательных состояний, а также обеспечения возможности работы с изменением разрядности и длительности псевдослучайной последовательности состояний. Устройство содержит шифратор управляющих сигналов, три сумматора, два мультиплексера, три коммутатора, шифратор. Устройство может вьшолнять функции генератора I (генератор псевдослучайных кодов, гене- ратор инкрементируемых последователь- ностных состояний, генератор декремен- тируемых последовательностных состояний) , счетчика (числа переходов, .числа переходов со сравнением полученного значения с эталонным), сумматора с контролем, сигнатурного анализатора. 1 шт., 4 табл. с (Л OQ ю 4 О to со

Редактор А.Огар

Составитель А.Сиротская

Техред И.Попбвич Корректор В. Бутяга

2966/52

Тираж 672Подписное

ВНИШИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Прое ктная, 4

| Устройство для обнаружения и диагностики неисправностей логических блоков | 1976 |

|

SU615492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для встроенного тестового контроля | 1984 |

|

SU1196877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-15—Публикация

1986-01-14—Подача