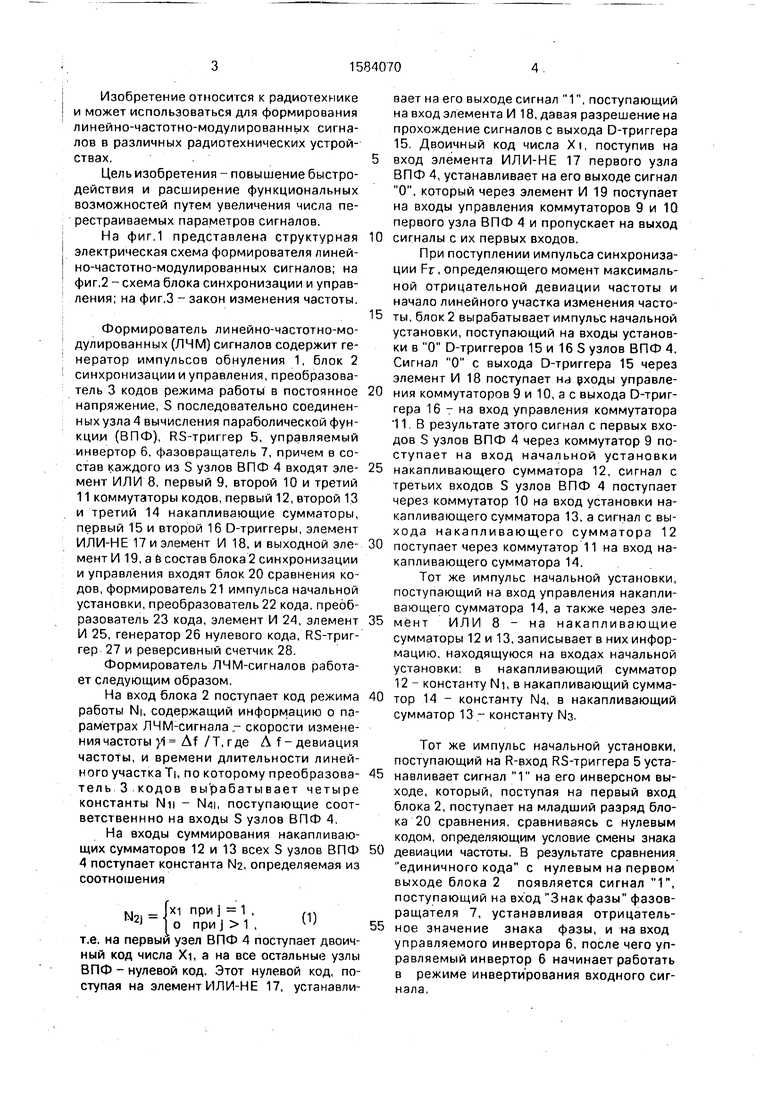

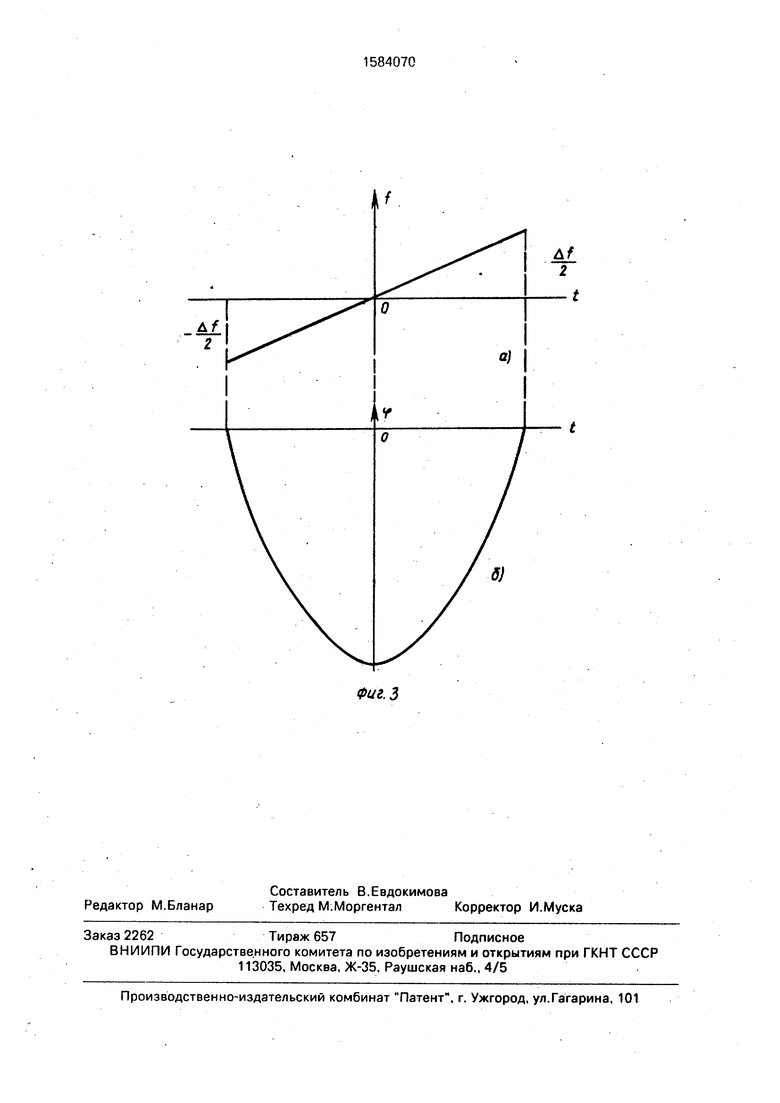

Фиг.1

Изобретение относится к радиотехнике и может использоваться для формирования линейно-частотно-модулированных сигналов в различных радиотехнических устройствах,

Цель изобретения - повышение быстродействия и расширение функциональных возможностей путем увеличения числа перестраиваемых параметров сигналов.

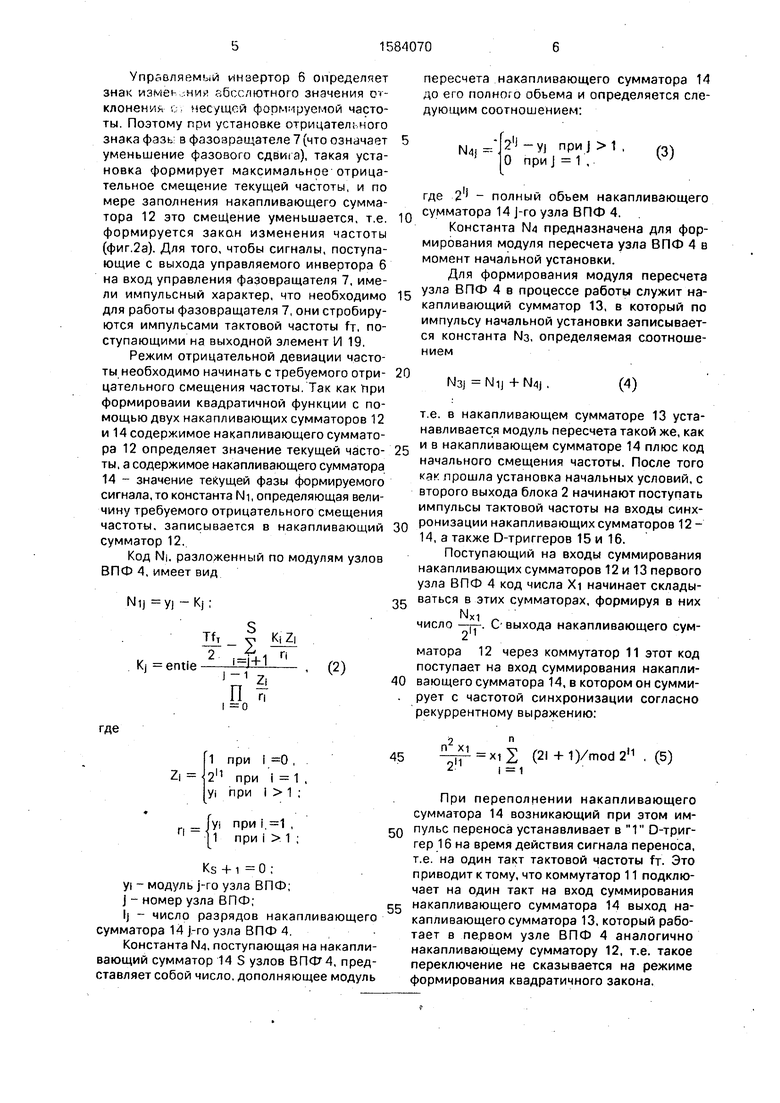

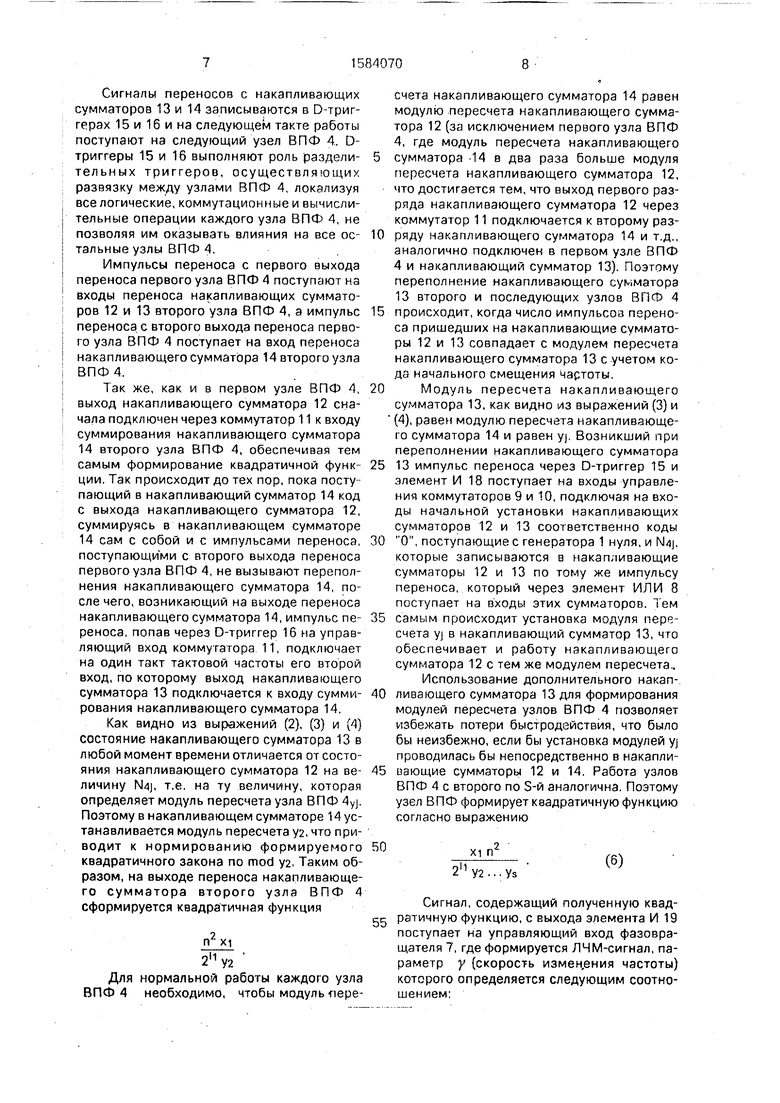

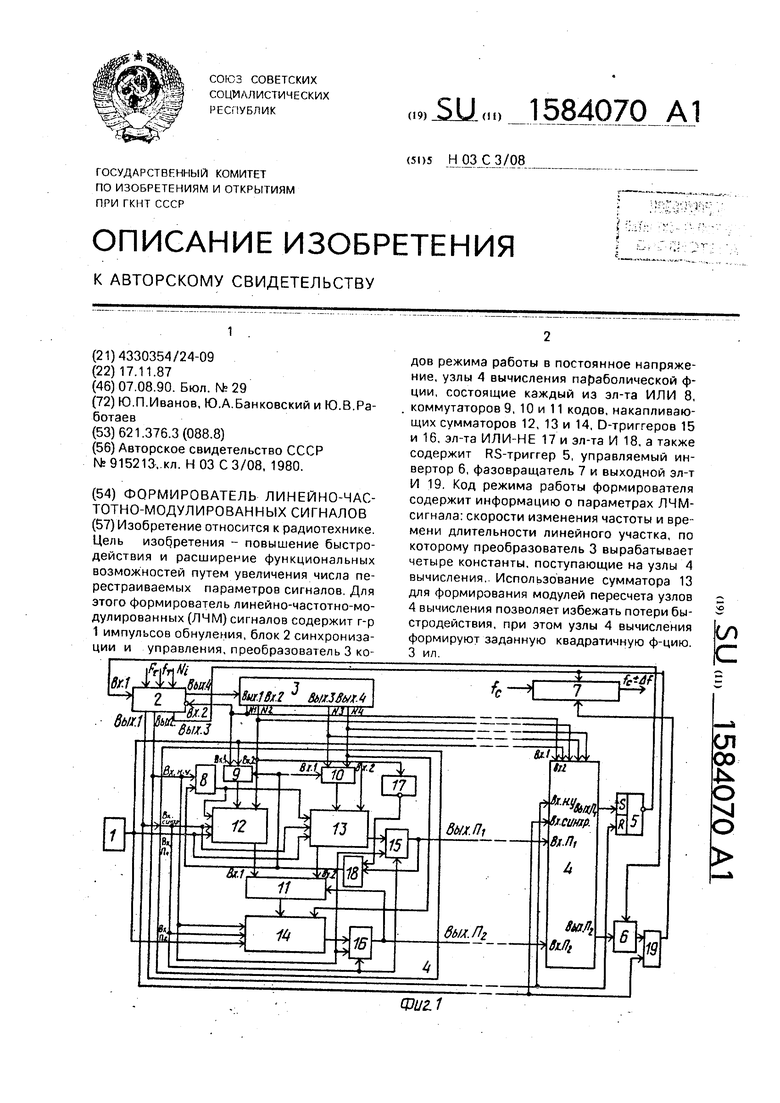

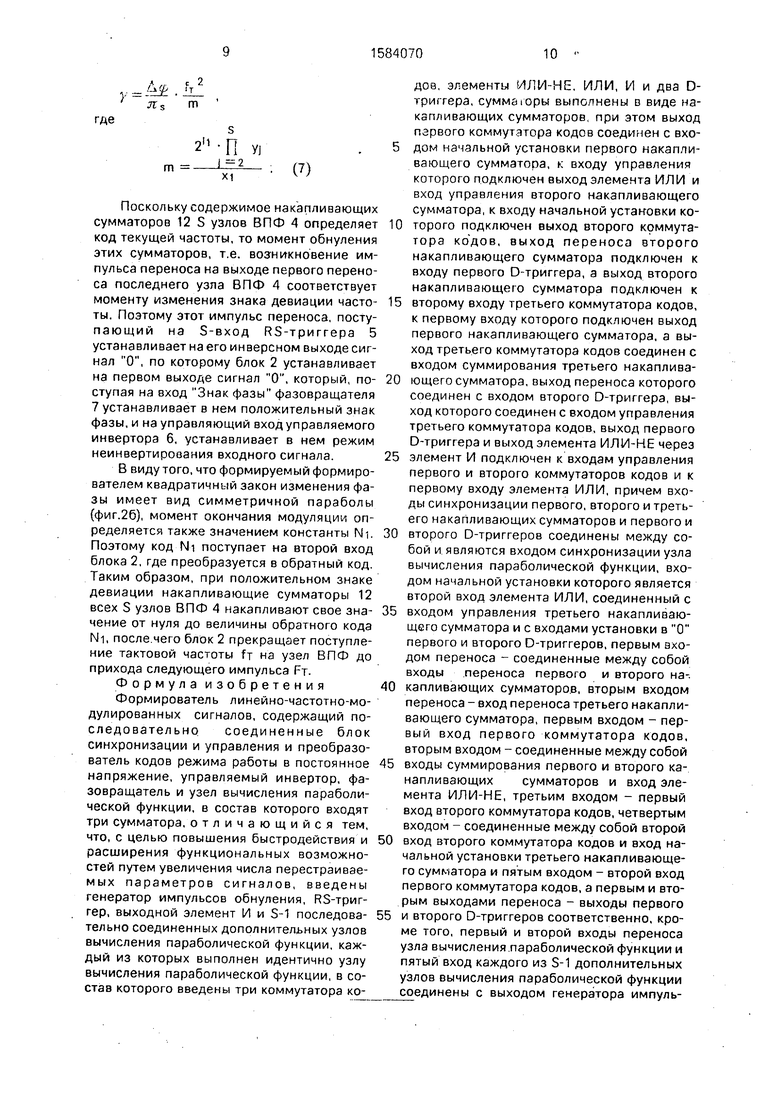

На фиг.1 представлена структурная электрическая схема формирователя линейно-частотно-модулированных сигналов; на фиг.2 - схема блока синхронизации и управления; на фиг.З - закон изменения частоты.

Формирователь линейно-частотно-модулированных (ЛЧМ) сигналов содержит генератор импульсов обнуления 1, блок 2 синхронизации и управления, преобразователь 3 кодов режима работы в постоянное напряжение, S последовательно соединен- ныхузла 4 вычисления параболической функции (ВПФ), RS-триггер 5, управляемый инвертор 6, фазовращатель 7, причем в состав каждого из S узлов ВПФ 4 входят элемент ИЛИ 8, первый 9, второй 10 и третий 11 коммутаторы кодов, первый 12, второй 13 и третий 14 накапливающие сумматоры, первый 15 и второй 16 D-триггеры, элемент ИЛИ-НЕ 17 и элемент И 18, и выходной элемент И 19, а в состав блока 2 синхронизации и управления входят блок 20 сравнения кодов, формирователь 21 импульса начальной установки, преобразователь 22 кода, преобразователь 23 кода, элемент И 24, элемент И 25, генератор 26 нулевого кода, RS-триггер 27 и реверсивный счетчик 28.

Формирователь ЛЧМ-сигналов работает следующим образом.

На вход блока 2 поступает код режима работы NI, содержащий информацию о параметрах ЛЧМ-сигнала,- скорости изменения частоты yi Af /Т, где Л f- девиация частоты, и времени длительности линейного участка Т|, по которому преобразова- тель 3 кодов вырабатывает четыре константы NII - N41, поступающие соот- ветственнно на входы S узлов ВПФ 4.

На входы суммирования накапливающих сумматоров 12 и 13 всех S узлов ВПФ 4 поступает константа Na, определяемая из соотношения

О)

N Jxi при j 1 ,

N2J 1 о при 1 , т.е. на первый узел ВПФ 4 поступает двоичный код числа Xi, а на все остальные узлы ВПФ - нулевой код. Этот нулевой код, поступая на элементИЛИ-НЕ 17, устанавливает на его выходе сигнал 1, поступающий на вход элемента И 18, давая разрешение на прохождение сигналов с выхода D-триггера 15. Двоичный код числа Xi, поступив на

вход элемента ИЛИ-НЕ 17 первого узла ВПФ 4, устанавливает на его выходе сигнал О, который через элемент И 19 поступает на входы управления коммутаторов 9 и 10 первого узла ВПФ 4 и пропускает на выход

0 сигналы с их первых входов.

При поступлении импульса синхронизации Fr, определяющего момент максимальной отрицательной девиации частоты и начало линейного участка изменения часто5 ты, блок 2 вырабатывает импульс начальной установки, поступающий на входы установки в О D-триггеров 15 и 16 S узлов ВПФ 4. Сигнал О с выхода D-триггера 15 через элемент И 18 поступает на входы управле0 ния коммутаторов 9 и 10, а с выхода D-триггера 16 - на вход управления коммутатора 11 В результате этого сигнал с первых входов S узлов ВПФ 4 через коммутатор 9 поступает на вход начальной установки

5 накапливающего сумматора 12, сигнал с третьих входов S узлов ВПФ 4 поступает через коммутатор 10 на вход установки накапливающего сумматора 13, а сигнал с выхода накапливающего сумматора 12

0 поступает через коммутатор 11 на вход накапливающего сумматора 14.

Тот же импульс начальной установки, поступающий на вход управления накапливающего сумматора 14, а также через эле5 мент ИЛИ 8 - на накапливающие сумматоры 12 и 13, записывает в них информацию, находящуюся на входах начальной установки: в накапливающий сумматор 12 - константу NI, в накапливающий сумма0 тор 14 - константу N4, в накапливающий сумматор 13 - константу Мз.

Тот же импульс начальной установки, поступающий на R-вход RS-триггера 5уста5 навливает сигнал 1 на его инверсном выходе, который, поступая на первый вход блока 2, поступает на младший разряд блока 20 сравнения, сравниваясь с нулевым кодом, определяющим условие смены знака

0 девиации частоты. В результате сравнения единичного кода с нулевым на первом выходе блока 2 появляется сигнал 1, поступающий на вход Знак фазы фазовращателя 7, устанавливая отрицатель5 ное значение знака фазы, и на вход управляемого инвертора 6, после чего управляемый инвертор 6 начинает работать в режиме инвертирования входного сигнала.

Управляемой инвертор 6 определяет знак измен ни .с,бсслютного значения отклонен и , чес/щей формируемой частоты. Поэтому при установке отрицател; чого знака фазь в фазоаращзтеле 7 (что означает уменьшение фазового сдвша), такая установка формирует максимальное отрицательное смещение текущей частоты, и по мере заполнения накапливающего сумматора 12 это смещение уменьшается, т.е. формируется закон изменения частоты (фиг.2а). Для того, чтобы сигналы, поступающие с выхода управляемого инвертора 6 на вход управления фазовращателя 7, имели импульсный характер, что необходимо для работы фазовращателя 7, они стробиру- ются импульсами тактовой частоты тт, поступающими на выходной элемент И 19.

Режим отрицательной девиации частоты необходимо начинать с требуемого отрицательного смещения частоты. Так как при формироваии квадратичной функции с помощью двух накапливающих сумматоров 12 и 14 содержимое накапливающего сумматора 12 определяет значение текущей частоты, а содержимое накапливающего сумматора 14 - значение текущей фазы формируемого сигнала, то константа NI, определяющая величину требуемого отрицательного смещения частоты, записывается в накапливающий сумматор 12.

Код NI, разложенный по модулям узлов ВПФ 4, имеет вид

,-Kj;

TfT KJ entie

y M

2 ,4+1 ri

П

где

Zi .

1 при i 0,

2й при i 1 , у, при i 1 ;

n

/у, при i 1 , 1 при i 1

Ks + 1 0 ;

yi - модуль j-го узла ВПФ,

j - номер узла ВПФ;

Ij - число разрядов накапливающего сумматора 14 j-ro узла ВПФ 4.

Константа N4, поступающая на накапливающий сумматор 14 S узлов ВПФ 4, представляет собой число, дополняющее модуль

пересчета накапливающего сумматора 14 до его полного объема и определяется следующим соотношением:

М4,Р-У1 , 4J 0 при 1 ,

(3)

где 2lj - полный объем накапливающего

сумматора 14 J-ro узла ВПФ 4.

Константа N4 предназначена для формирования модуля пересчета узла ВПФ 4 в момент начальной установки.

Для формирования модуля пересчета

узла ВПФ 4 в процессе работы служит накапливающий сумматор 13, в который по импульсу начальной установки записывается константа Мз, определяемая соотношением

20

N3J Nij +N«j

(4)

5

0

5

0

5

т.е. в накапливающем сумматоре 13 устанавливается модуль пересчета такой же, как и в накапливающем сумматоре 14 плюс код начального смещения частоты. После того кз прошла установка начальных условий, с второго выхода блока 2 начинают поступать импульсы тактовой частоты на входы синхронизации накапливающих сумматоров 12 - 14, а также D-триггеров 15 и 16.

Поступающий на входы суммирования накапливающих сумматоров 12 и 13 первого узла ВПФ 4 код числа Xi начинает складываться в этих сумматорах, формируя в них

NXI

21Г

матора 12 через коммутатор 11 этот код поступает на вход суммирования накапливающего сумматора 14, в котором он суммирует с частотой синхронизации согласно рекуррентному выражению:

2

ПХ1 xi2 (2l + 1)/mod211 . (5)

число

С-выхода накапливающего сум2И

i i

При переполнении накапливающего сумматора 14 возникающий при этом импульс переноса устанавливает в 1 D-триг- гер 16 на время действия сигнала переноса, т.е. на один такт тактовой частоты fr. Это приводит к тому, что коммутатор 11 подключает на один такт на вход суммирования

накапливающего сумматора 14 выход накапливающего сумматора 13, который работает в первом узле ВПФ 4 аналогично накапливающему сумматору 12, т.е. такое переключение не сказывается на режиме формирования квадратичного закона.

Сигналы переносов с накапливающих сумматоров 13 и 14 записываются n D-триг- герах 15 и 16 и на следующем такте работы поступают на следующий узел ВПФ 4. D- триггеры 15 и 16 выполняют роль разделительных триггеров, осуществляющих. развязку между узлами ВПФ 4, локализуя все логические, коммутационные и вычисли- тельные операции каждого узла ВПФ 4, не позволяя им оказывать влияния на все ос- тальные узлы ВПФ 4.

Импульсы переноса с первого выхода переноса первого узла ВПФ 4 поступают на входы переноса накапливающих сумматоров 12 и 13 второго узла ВПФ 4, а импульс переноса с второго выхода переноса первого узла ВПФ 4 поступает на вход переноса накапливающего сумматора 14 второго узла ВПФ 4.

Так же, как и в первом узле ВПФ 4, выход накапливающего сумматора 12 сначала подключен через коммутатор 11 к входу суммирования накапливающего сумматора 14 второго узла ВПФ 4, обеспечивая тем самым формирование квадратичной функции. Так происходит до тех пор, пока поступающий в накапливающий сумматор 14 код с выхода накапливающего сумматора 12, суммируясь в накапливающем сумматоре 14 сам с собой и с импульсами переноса, поступающими с второго выхода переноса первого узла ВПФ 4, не вызывают переполнения накапливающего сумматора 14, после чего, возникающий на выходе переноса накапливающего сумматора 14, импульс переноса, попав через D-триггер 16 на управляющий вход коммутатора 11, подключает на один такт тактовой частоты его второй вход, по которому выход накапливающего сумматора 13 подключается к входу суммирования накапливающего сумматора 14.

Как видно из выражений (2), (3) и (4) состояние накапливающего сумматора 13 в любой момент времени отличается от состояния накапливающего сумматора 12 на величину N4), т.е. на ту величину, которая определяет модуль пересчета узла ВПФ 4yj. Поэтому в накапливающем сумматоре 14 устанавливается модуль пересчета у2, что приводит к нормированию формируемого квадратичного закона по mod y2, Таким образом, на выходе переноса накапливающего сумматора второго узла ВПФ 4 сформируется квадратичная функция

n2 xi

2И У2

Для нормальной работы каждого узла ВПФ 4 необходимо, чтобы модуль пересчета накапливающего сумматора 14 равен модулю пересчета накапливающего сумматора 12 (за исключением первого узла ВПФ 4, где модуль пересчета накапливающего

сумматора 14 в два раза больше модуля пересчета накапливающего сумматора 12, что достигается тем, что выход первого разряда накапливающего сумматора 12 через коммутатор 11 подключается к второму разряду накапливающего сумматора 14 и т.д., аналогично подключен в первом узле ВПФ 4 и накапливающий сумматор 13). Поэтому переполнение накапливающего сумматора 13 второго и последующих узлов ВПФ 4

происходит, когда число импульсоз переноса пришедших на накапливающие сумматоры 12 и 13 совпадает с модулем пересчета накапливающего сумматора 13 с учетом кода начального смещения частоты.

Модуль пересчета накапливающего сумматора 13, как видно из выражений (3) и (4), равен модулю пересчета накапливающего сумматора 14 и равен у). Возникший при переполнении накапливающего сумматора

13 импульс переноса через D-триггер 15 и элемент И 18 поступает на входы управления коммутаторов 9 и 10, подключая на входы начальной установки накапливающих сумматоров 12 и 13 соответственно коды

О, поступающие с генератора 1 нуля, и N/JJ, которые записываются в накапливающие сумматоры 12 и 13 по тому же импульсу переноса, который через элемент ИЛИ 8 поступает на входы этих сумматоров. Тем

самым происходит установка модуля пересчета у; в накапливающий сумматор 13, чго обеспечивает и работу накапливающего сумматора 12 с тем же модулем пересчета.. Использование дополнительного накап0 ливающего сумматора 13 для формирования модулей пересчета узлов ВПФ 4 позволяет избежать потери быстродействия, что было бы неизбежно, если бы установка модулей yj проводилась бы непосредственно в накапли5 вающие сумматоры 12 и 14. Работа узлов ВПФ 4 с второго по S-й аналогична. Поэтому узел ВПФ формирует квадратичную функцию согласно выражению

xi n

211

У2 -.. Уз

(6)

Сигнал, содержащий полученную квад- ратичную функцию, с выхода элемента И 19 поступает на управляющий вход фазовращателя 7, где формируется ЛЧМ-сигнал, параметр у {скорость изменения частоты) которого определяется следующим соотношением:

,,ЈЈ .IL

jr.

m

где

2 1-П У1

I 2

X1

(7)

Поскольку содержимое накапливающих сумматоров 12 S узлов ВПФ 4 определяет код текущей частоты, то момент обнуления этих сумматоров, т.е. возникновение импульса переноса на выходе первого переноса последнего узла ВПФ 4 соответствует моменту изменения знака девиации частоты. Поэтому этот импульс переноса, поступающий на S-вход RS-триггера 5 устанавливает на его инверсном выходе сигнал О, по которому блок 2 устанавливает на первом выходе сигнал О, который, поступая на вход Знак фазы фазовращателя 7 устанавливает в нем положительный знак фазы, и на управляющий вход управляемого инвертора 6, устанавливает в нем режим неинвертирования входного сигнала.

В виду того, что формируемый формирователем квадратичный закон изменения фазы имеет вид симметричной параболы (фиг.2б), момент окончания модуляции определяется также значением константы NI. Поэтому код NI поступает на второй вход блока 2, где преобразуется в обратный код. Таким образом, при положительном знаке девиации накапливающие сумматоры 12 всех S узлов ВПФ 4 накапливают свое значение от нуля до величины обратного кода NI, после чего блок 2 прекращает поступление тактовой частоты fr на узел ВПФ до прихода следующего импульса FT.

Формула изобретения

Формирователь линейно-частотно-модулированных сигналов, содержащий последовательно соединенные блок синхронизации и управления и преобразователь кодов режима работы в постоянное напряжение, управляемый инвертор, фазовращатель и узел вычисления параболической функции, в состав которого входят три сумматора, отличающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем увеличения числа перестраивае- мых параметров сигналов, введены генератор импульсов обнуления, RS-триг- гер, выходной элемент И и S-1 последовательно соединенных дополнительных узлов вычисления параболической функции, каждый из которых выполнен идентично узлу вычисления параболической функции, в состав которого введены три коммутатора кодов, элементы ИЛИ-НЕ, ИЛИ, И и два D- триггера, сумма юры выполнены в виде накапливающих сумматоров, при этом выход пэрвого коммутатора кодов соединен с вхо- 5 дом начальной установки первого накапливающего сумматора, к входу управления которого подключен выход элемента ИЛИ и вход управления второго накапливающего сумматора, к входу начальной установки ко0 торого подключен выход второго коммутатора кодов, выход переноса второго накапливающего сумматора подключен к входу первого D-триггера, а выход второго накапливающего сумматора подключен к

5 второму входу третьего коммутатора кодов, к первому входу которого подключен выход первого накапливающего сумматора, а выход третьего коммутатора кодов соединен с входом суммирования третьего накаплива0 ющего сумматора, выход переноса которого соединен с входом второго D-триггера, выход которого соединен с входом управления третьего коммутатора кодов, выход первого D-триггера и выход элемента ИЛИ-НЕ через

5 элемент И подключен к входам управления первого и второго коммутаторов кодов и к первому входу элемента ИЛИ, причем входы синхронизации первого, второго и третьего накапливающих сумматоров и первого и

0 второго D-триггеров соединены между собой и являются входом синхронизации узла вычисления параболической функции, входом начальной установки которого является второй вход элемента ИЛИ, соединенный с

5 входом управления третьего накапливающего сумматора и с входами установки в О первого и второго D-триггеров, первым входом переноса - соединенные между собой входы переноса первого и второго на-.

0 капливающих сумматоров, вторым входом переноса - вход переноса третьего накапливающего сумматора, первым входом - первый вход первого коммутатора кодов, вторым входом - соединенные между собой

5 входы суммирования первого и второго ка- напливающих сумматоров и вход элемента ИЛИ-НЕ, третьим входом - первый вход второго коммутатора кодов, четвертым входом - соединенные между собой второй

0 вход второго коммутатора кодов и вход начальной установки третьего накапливающего сумматора и пятым входом - второй вход первого коммутатора кодов, а первым и вторым выходами переноса - выходы первого

5 и второго D-триггеров соответственно, кроме того, первый и второй входы переноса узла вычисления параболической функции и пятый вход каждого из S-1 дополнительных узлов вычисления параболической функции соединены с выходом генератора импульсов обнуления, первый и второй выходы переноса узла вычисления параболической функции подключены соответственно к первому и второму входам переноса первого дополнительного узла вычисления параболической функции, а первый и второй выходы переноса S-1 дополнительного узла вычисления параболической функции подключены соответственно к S-входу RS-триг- гера и к входу управляемого1 инвертора, выход которого через выходной элемент И соединен с входом управления фазовращателя, аход Знак фазы которого соединен с входом управления управляемого инвертора и первым выходом блока синхронизации и управления, второй выход которого соединен с входами синхронизации узла вычисле- ния параболической функции и S-1 дополнительных узлов вычисления параболической функции и с вторым входом выходного элемента И , а третий выход - с входами начальной установки узла вычисления параболической функции и S-1 дополнительных узлов вычисления параболической функции и CR-входом RS-триггера, инверсный выход которого соединен с первым входом блока синхронизации и управления, второй вход которого соединен с первыми

входами узла вычисления параболической функции и S-1 дополнительных узлов вычисления параболической функции и первым выходом преобразователя кодов режима работы в постоянное напряжение, другие

выходы которого подключены соответственно к вторым, третьим и четвертым входам узла вычисления параболической функции и S-1 дополнительных узлов, вычисления параболической функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Процессор для цифровой обработки сигналов | 1985 |

|

SU1257662A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Цифровой фильтр | 1979 |

|

SU860286A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Спектроанализатор кардиосигналов | 1984 |

|

SU1170371A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Спектроанализатор биологических сигналов | 1980 |

|

SU868613A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия и расширение функциональных возможностей путем увеличения числа перестраиваемых параметров сигналов. Для этого формирователь линейно-частотно-модулированных (ЛЧМ) сигналов содержит г-р 1 импульсов обнуления, блок 2 синхронизации и управления, преобразователь 3 кодов режима работы в постоянное напряжение, узлы 4 вычисления параболической ф-ции, состоящие каждый из эл-та ИЛИ 8, коммутаторов 9, 10 и 11 кодов, накапливающих сумматоров 12, 13 и 14, D-триггеров 15 и 16, эл-та ИЛИ-НЕ 17 и эл-та И 18, а также содержит RS-триггер 5, управляемый инвертор 6, фазовращатель 7 и выходной эл-т И 19. Код режима работы формирователя содержит информацию о параметрах ЛЧМ-сигнала: скорости изменения частоты и времени длительности линейного участка, по которому преобразователь 3 вырабатывает четыре константы, поступающие на узлы 4 вычисления. Использование сумматора 13 для формирования модулей пересчета узлов 4 вычисления позволяет избежать потери быстродействия, при этом узлы 4 вычисления формируют заданную квадратичную ф-цию. 3 ил.

0И/.1

вш 4

Bit

But f

б)

Фиг.З

| Авторское свидетельство СССР № 915213.кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-07—Публикация

1987-11-17—Подача