Изобретение относится к автоматике и вычислительной технике и может быть использовано для отображения формы иссле- дуемого сигнала в радиоизмерительных устройствах, управляемых микропроцессором.

Цель изобретения - повышение быстродействия устройства.

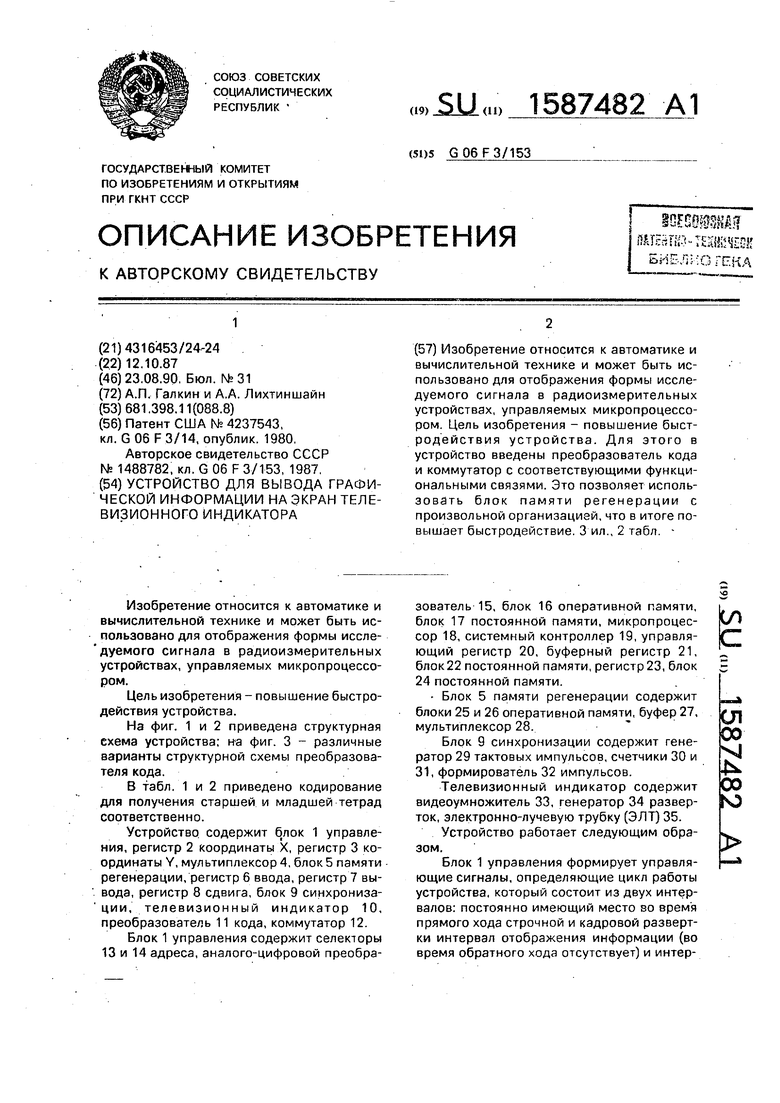

На фиг. 1 и 2 приведена структурная схема устройства; н-а фиг. 3 - различные варианты структурной схемы преобразователя кода.

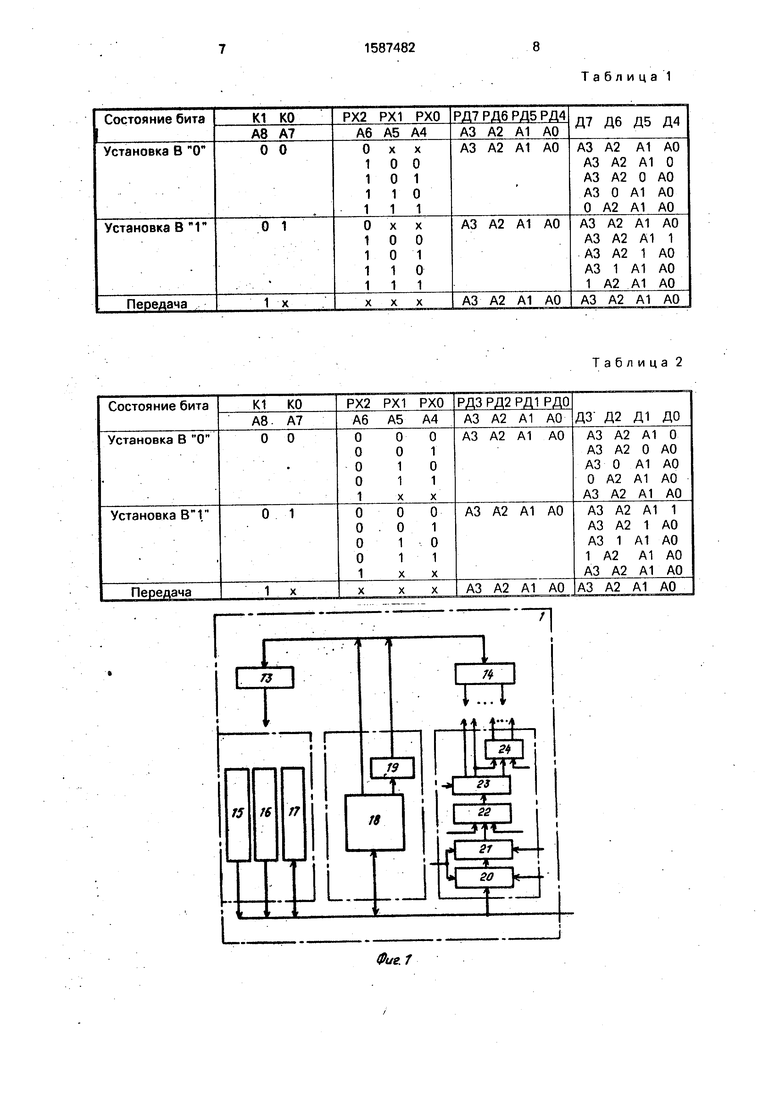

В табл. 1 и 2 приведено кодирование для получения старшей и младшей тетрад соответственно.

Устройство, содержит 1 управления, регистр 2 координаты X, регистр 3 координаты Y, мультиплексор 4, блок 5 памяти регенерации, регистр 6 ввода, регистр 7 вывода, регистр 8 сдвига, блок 9 синхронизации, телевизионный индикатор 10, преобразователь 11 кода, коммутатор 12.

Блок 1 управления содержит селекторы 13 и 14 адреса, аналого-цифровой преобразователь 15, блок 16 оперативной памяти, блок 17 ПОСТОЯННОЙ памяти, микропроцессор 18, системный контроллер 19, управляющий регистр 20, буферный регистр 21, блок22 постоянной памяти, регистр23, блок 24 постоянной памяти.

Блок 5 памяти регенерации содержит блоки 25 и 26 оперативной памяти, буфер 27, мультиплексор 28.

Блок 9 синхронизации содержит генератор 29 тактовых импульсов, счетчики 30 и 31, формирователь 32 импульсов.

Телевизионный индикатор содержит видеоумножитель 33, генератор 34 разверток, электронно-лучевую трубку (ЭЛТ) 35.

Устройство работает следующим образом.

Блок 1 управления формирует управляющие сигналы, определяющие цикл работы устройства, который состоит из двух интервалов: постоянно имеющий место во время прямого хода строчной и кадровой развертки интервал отображения информации (во время обратного хода отсутствует) и интер(Л

с

ел

00

00

ю

вал смены информации в блоке 5, который программно задается по мере необходимости.

В интервале отображения информации блок 9 синхронизации производит обращение к блоку 5 памяти регенерации с целью чтения очередного слова информации, которое в следующем цикле отображается на экране ЭЛТ 35. Считанная информация заносится в регистр 8 сдвига, в котором преобразуется в последовательность видеосигналов, которые поступают на видеовход индикатора 10. К моменту времени, когда информация регистра 8 последовательно преобразована в видеосигналы блоком 9 синхронизации, совместно с блоком 1 управления подготавливается следующее слово информации и заносится в регистр 8 сдвига, образуя таким образом непрерывную последовательность видеосигналов во время прямого хода разверток. На входы телевизионного индикатора 10, кроме последовательности видеосигналов, поступают синхронизирующие сигналы кадровой и строчной разверток из блока 9.

Время преобразования слова информации в последовательность видеосигналов гораздо больше, чем необходимое время для подготовки следующего слова и поэтому остальное время цикла отображения отводится для обращений микропроцессора 18 к блоку 5 памяти регенерации. Блоки 20-24 составляют микропрограммное устройство управления, которое совместно с сигналами блока 9 синхронизации обеспечивает выполнение следующих операций: запись байта в блок 5 памяти регенерации, чтение байта информации из блока 5 памяти регенерации, установка определенного бита в байте, очистка определенного бита в байте.

Микропроцессор 18 производит обработку информации, находящейся в блоках 16 и 17 и подготовку данных, необходимых для выполнения указанных операций над блоком 5 памяти. При записи байта микропроцессором 18 выполняются следующие действия; записывается адрес байта в адресные регистры 2 и 3 через шину данных, заносятся данные в регистр 6 ввода через шину данных, устанавливается код операции записи в управляющий регистр 20.

Содержимое регистра 6 ввода переда- ется через преобразователь 11 кода на ин- . формационные входы блока 5 памяти по адресу, определяемому содержимым регистров 2 и 3 в интервале времени, предназначенном для обслуживания обращений микропроцессора 18. В конце указанного интервала управляющий регистр 20 устанавливается в исходное состояние. Время выполнения операции записи байта, как правило, равно половине времени одного цикла отображения.

При чтении байта информации из блока

5 памяти программно производятся следующие действия: записывается адрес байта в регистры 2 и 3, устанавливается код чтения в управляющий регистр 20, производится 0 чтение байта из регистра 7 вывода в микропроцессор 18 по шине данных.

В конце интервала чтения, как и в случае других операций, управляющий регистр 20 возвращается в исходное состояние. Опера- 5 ции чтения и записи могут использоваться, например, для выполнения оперативного - тестирования блока 5 памяти.

Для выполнения операции установки бита микропроцессором производятся сле- 0 дующие действия: запись адреса бита, определяемого координатами X и Y элемента отображения, в регистры 2 и 3,- установка в управляющий регистр 20 кода операции установки бита.

5После получения указанного кода операции в текущем или очередном цикле отображения производится чтение из блока 5 байта информации, в котором находится указанный бит, запись в регистр 7 вывода, 0 передача на вход преобразователя 11 кода, выполнение последним обработки байта, заключающейся в установке в единицу бита, определяемого младшими разрядами координаты X РХ2...РХО, передача на информа- 5 ционные входы блока 5 и запись обработанного байта по указанному адресу, т.е. в данном случае выполняется цикл чтение-модификация-запись. При этом адрес байта определяется как конкатенация со- 0 держимого регистра 3 и старшей части регистра 2, младшая часть координаты X РХ2...РХО определяет номер бита в байте. Указанная операция производится в интервалы времени, предназначенные для обслу- 45 живания обращений микропроцессора 18, после выполнения которой производится установка в исходное состояние управляющего регистра 20.

Для выполнения операции очистки бита микропроцессором выполняются действия, аналогичные для операции установки бита, за исключением того, что в управляющий регистр 20 заносится код битовой очистки.

Далее выполняются те же действия, что м при битовой установке. Отличие заключается в том. что преобразователь 11 кода под управлением сигналов блока 1 производит очистку бита в байте, определяемого координатами РХ2...РХО.

В блоках 16.и 17 хранятся один или несколько массивов информации (например, цифровой сигнал из 256 выборок и за- нимающий 256 байт), которые отображаются в текущий момент времени на экране ЭЛТ. При необходимости смены одного из отображаемых графиков необходимо выполнить последовательность операций очистки и установки битов.

Преобразователь 11 кода осуществляет передачу содержимого регистра вывода или регистра ввода на информационные входы блока 5, установки бита или очистку, задаваемого координатой РХ2...РХО, под управлением сигналов К1, КО блока 1. Несколько вариантов реализации преобразователя приведено на фиг, 3.

Для получения старшей (табл. 1) и младшей (табл. 2) тетрад преобразователем кода (фиг. 36) выполняются следующие действия: при коде управления К1, (очистка бита) устанавливается указанный бит в нулевое состояние, остальные передаются на выход в неизменном состоянии; при коде К1, (установка бита) указанный бит устанавливается в единичное состояние, остальные передаются на выход в неизменном состоянии; при коде К1, информация передается на выход без изменения.

Таким образом, введение преобразователя 11 кода, коммутатора 12 и соответствующих функциональных связей позволяет Использовать блок 5 памяти регенерации с произвольной организацией и повысить быстродействие устройства.

Формула изобретения

Устройство для вывода графической информации на зкран телевизионного индикатора, содержащее блок управления, регистры координаты X и координаты Y, регистр ввода, регистр вывода, регистр сдвига, мультиплексор, блок памяти регенерации, блок синхронизации, первый и второй выходы которого соединены соответственно с кадровым и строчным синх- ровходами телевизионного индикатора, видеовход которого подключен к выходу регистра сдвига, информационные входы которого подключены к выходам блока памяти регенерации, соединенным с информационными входами регистра вывода, вход управления записью которого соединен с первым выходом блока управления, информационные входы-выходы которого подключены к информационным входам регистров координат X и Y и регистра ввода, вход

управления записью которого соединен с вторым выходом блока управления, третий и четвертый выходы которого подключены соответственно к входам управления записью регистров координат X и Y, выход

регистра координаты Y и первый выход регистра координаты X подключены к первому информационному входу мультиплексора. второй информационный вход которого подключен к третьему выходу блока синхронизации, четвертый выход которого подключен к тактовым входам регистра сдвига и блока управления, пятый выход которого подключен к управляющему входу мультиплексора, выход которого подключен к адресным входам блока памяти регенерации, шестой выход блока управления соединен с входом управления записью регистра сдвига, седьмой выход блока управления соединен с входами управления считыванием

регистров ввода и вывода, первый адресный вход блока управления соединен с пятым выходом блока синхронизации, шестой вы- ход которого подключен к синхровходу блока управления, информационный вход

которого является информационным входом устройства, отличающееся тем. что, с целью повышения быстродействия устройства, оно содержит преобразователь кода, коммутатор, выходы которого подключены к информационным входам-выходам блока управления, выходы первой группы которого соединены с управляющими входами блока памяти регенерации, выходы второй группы блока управления соединены

с информационными входами группы преобразователя кода, первый информационный вход которого соединен с выходами регистров ввода и вывода, второй выход регистра координаты X соединен с вторым информационным входом преобразователя кода, выход которого подключен к информационному входу блока памяти регенерации, управляющий вход преобразователя кода соединен с восьмым выходом блока управления. второй адресный вход которого подключен к выходу мультиплексора, информационный вход коммутатора соединен с выходом регистра вывода, управляющий вход коммутатора соединен с девятым

выходом блока управления.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1697074A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1682997A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для формирования тестов | 1988 |

|

SU1573457A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для отображения формы исследуемого сигнала в радиоизмерительных устройствах, управляемых микропроцессором. Цель изобретения - повышение быстродействия устройства. Для этого в устройство введены преобразователь кода и коммутатор 12 с соответствующими функциональными связями. Это позволяет использовать блок памяти регенерации с произвольной организацией, что в итоге повышает быстродействие. 3 ил., 1 табл.

Таблица 2

чт г I г

;Г

J

ЛГ2..Ли AMlMW

УпрвЙаичг nt.nt т И

| Патент США № 4237543, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1987-10-12—Подача