ел

00

ел

Изобретение относится к вычислительной технике и может быть использовано в качестве формирователя адреса буферного запоминающего устройства для последовательной адресации ячеек памяти.

Цель изобретения - упрощение устройства

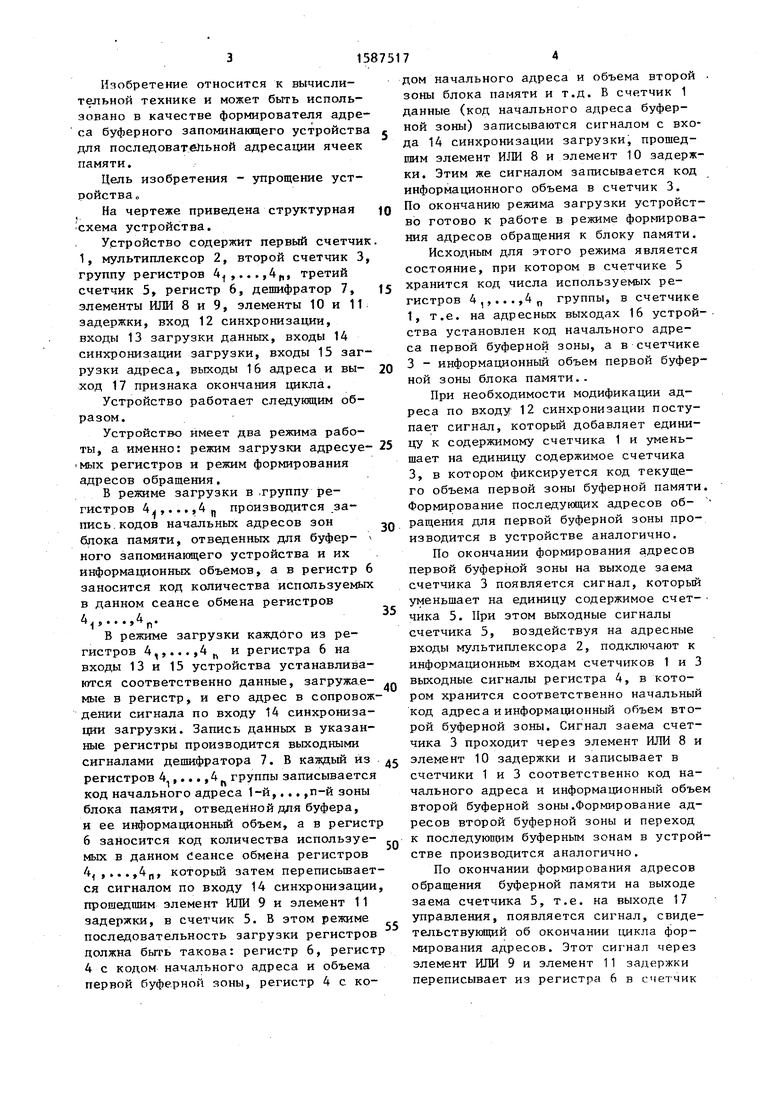

На чертеже приведена структурная схема устройства.

Устройство содержит первый счетчик 1, мультиплексор 2, второй счетчик 3, группу регистров 4,..,,4, третий счетчик 5, регистр 6, дешифратор 7, элементы ИЛИ 8 и 9, элементы 10 и 11 задержки, вход 12 синхронизации, входы 13 загрузки данных, входы 14 синхронизации загрузки, входы 15 загрузки адреса, выходы 16 адреса и вы- ход 17 признака окончания цикла.

Устройство работает следующим образом.

Устройство имеет два режима работы, а именно: режим загрузки адресуе- 1МЫХ регистров и режим формирования

адресов обращения.

В режиме загрузки в .группу регистров 4,. .. ,4 д производится .запись, кодов начальных адресов зон блока памяти, отведенных для буфер- ного запоминанщего устройства и их информационных объемов, а в регистр 6 заносится код количества используемых в данном сеансе обмена регистров

j...

В режиме загрузки каждого из регистров 4,,...,4 и регистра 6 на входы 13 и 15 устройства устанавливаются соответственно данные, загружае- мые в регистр, и его адрес в сопровождении сигнала по входу 14 синхрониза- 1ЩИ загрузки. Запись данных в указанные регистры производится выходными сигналами дешифратора 7. В каждый из

регистров группы записывается

код начального адреса 1-й,... ,п-й зоны блока памяти, отведенной для буфера, и ее информационный объем, а в регист 6 заносится код количества используе- мьк в данном Сеансе обмена регистров 4,...,4п, который затем переписывается сигналом по входу 14 синхронизации прошедшим элемент ИЛИ 9 и элемент 11 задержки, в счетчик 5. В этом режиме последовательность загрузки регистров должна бьп ь такова: регистр 6, регист 4 с кодом начального адреса и объема первой буферной зоны, регистр 4 с ко

O

5 0

5

о

.„ j

п

5

дом начального адреса и объема второй . зоны блока памяти и т.д. В счетчик 1 данные (код начального адреса буферной зоны) записываются сигналом с входа 14 синхронизации загрузки, прошедшим элемент ИЛИ 8 и элемент 10 задержки. Этим же сигналом записывается код информационного объема в счетчик 3. По окончанию режима загрузки устройство готово к работе в режиме формирования адресов обращения к блоку памяти. Исходным для этого режима является состояние, при котором в счетчике 5 хранится код числа используемых регистров 4,,...,4п группы, в счетчике 1, т.е. на адресных выходах 16 устройства установлен код начального адреса первой буферной зоны, а в счетчике 3 - информационный объем первой буферной зоны блока памяти..

При необходимости модификации адреса по входу 12 синхронизации поступает сигнал, который добавляет единицу к содержимому счетчика 1 и уменьшает на единицу содержимое счетчика 3, в котором фиксируется код текущего объема первой зоны буферной памяти. Формирование последующих адресов обращения для первой буферной зоны производится в устройстве аналогично.

По окончании формирования адресов первой буферной зоны на выходе заема счетчика 3 появляется сигнал, которьй уменьшает на единицу содержимое счет- чика 5. При этом выходные сигналы счетчика 5, воздействуя на адресные входы мультиплексора 2, подключают к информационным входам счетчиков 1 и 3 выходные сигналы регистра 4, в котором хранится соответственно начальный код адреса и информационный объем второй буферной зоны. Сигнал заема счетчика 3 проходит через элемент ИЛИ 8 и элемент 10 задержки и записывает в счетчики 1 и 3 соответственно код начального адреса и информационный объем второй буферной зоны.Формирование адресов второй буферной зоны и переход к последуюп им буферным зонам в устройстве производится аналогично.

По окончании формирования адресов обращения буферной памяти на выходе заема счетчика 5, т.е. на выходе 17 управления, появляется сигнал, свиде- тельствукяций об окончании цикла формирования адресов. Этот сигнал через элемент ИЛИ 9 и элемент 11 задержки переписывает из регистра 6 в счетчик

5158 5 код количества используемых регистров группы.

После выполнения записи в счетчик 5 из регистра 6 данных сигналом с выхода элемента 10 задержки (сигналом заема счетчика 3, прошедшим элемент ШШ 8 и элемент 10 задержки) производится запись информационного объема и начального адреса первой буферной зоны соответственно - счетчики 3 и 1,

Для нормальной работы устройства величины задержек распространения сигналов на элементах 10 и 11 должны удовлетворять условиям: величина за- держки распространения сигнала на эле Менте 11 задержки должна быть больше длительности сигнала по входу 12 синхронизации (длительности сигнала заема счетчика 3); величина задержки рас пространения сигнала на элементе 10 задержки должна быть больше суммы времен задержки распространения сигналов на элементе 11 задержки, счетчике 5 (по информационным входам запис и) и задержки срабатьюания мультиплексора 2.

Формула изобрет е-н и я

Устройство для адресации буферной памяти, содержащее дешифратор, группу регистров, регистр, два элемента ИЛИ, первый элемент задержки, мультиплексор и три счетчика, информационный вход и вход синхронизации дешифратора соединены с входами загрузки адреса и синхронизации загрузки устройства соответственно, выходы дешиф

5 0 5

0

5

76

ратора соединены с входами записи регистра и регистров группы, информаци онные входы которых соединены с входом загрузки да нньк устройства, выходы регистров группы соединены с информационными входами мультиплексора, первый выход которого соединен с информационным входом первого счетчика, выход которого является адресным выходом устройства, входы считьгеания первого и второго счетчиков соединены с входом синхронизации устройства, а входы записей первого и второго счетчиков соединены с выходом первого элемента задержки, вход которого соединен с входом синхронизации загрузки устройства и с первым входом второго элемента ИЛИ, информационный вход третьего счетчика соединен с выходом регистра, информационный выход третьего счетчика соединен с адресным входом мультиплексора, отличающееся тем, что, с целью упрощения устройства, оно содержит второй элемент задержки, вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом устройства признака окончания цикла и выходом заема, третьего счетчика, вход записи которого соединен с выходом второго элемента задержки, а вход вычитания - с входом заема второго счетчика и вторым входом первого элемента ШШ, счетный вход вто- pori5 счетчика соединен с входом синхронизации устройства, а информационный вход второго счетчика соединен с вторым выходом мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1647579A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Устройство для контроля качества проводного монтажа | 1983 |

|

SU1108466A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

Изобретение относится к вычислительной технике и может быть использовано для последовательной адресации ячеек памяти буферного запоминающего устройства. Цель изобретения - упрощение устройства. Устройство содержит счетчики 1, 3, 5, мультиплексор 2, группу регистров 4 1,...,4 N, регистр 6, дешифратор 7, элементы ИЛИ 8 и 9, элементы 10 и 11 задержки, вход 12 синхронизации, входы 13 загрузки данных, входы 14 синхронизации загрузки, входы 15 загрузки адреса, выходы 16 адреса, выход 17 признака окончания цикла. Устройство позволяет в системах обработки данных с общим полем (блоком) памяти формировать адрес обращения к буферной памяти, которая может представлять собой как постоянную и непрерывную часть блока памяти, так и ряд буферных зон, разнесенных между собой в блоке памяти системы обработки данных. 1 ил.

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР 1485255, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1988-08-01—Подача