ный блок 2, первый 3 и второй 4 блоки коммутации, блок 5 прямого преоб- разования даннык, блок 6 обратного преобразования данных, шифратор 7 и блок 8 местного управления. Блок 5 прямого преобразования данных и блок 6 обратного преобразования дан ных содержат каждый регистры сдвига, мультиплексор, элемент НЕ, два элемента И и группу элементов И. Каждый Из блоков 3 и А коммутации содержит два счетчика, матрицу элементов И, два дешифратора. Блок 8 местного управления содержит регистр .начального адреса, регистр текущего адреса, регистр следЗ Пощего адреса, выходной регистр, регистр режимов работы, программируемую логическую матрицу, распределитель импульсов, элемемг ilTlK с входами пуска устройства. В устройстве обеспечивается повышение надежности путем повышения устойчивости

к отказам разрядных сечений накопителя 1 при записи в него слов, содержащих по одному сообщению, для чего используется метод распределения потерь данных за счет избыточпости информации, получаемой в многоканальных измерительных системах с временным разделением каналов. Этот метод основан на наличии сообщений, не попавших в отказавшее разрядное сечение накопителя 1, что позволяет при изменении положения упакованных сообщений в слове, добиться распределения потерь между каналами. Для обеспечения воз- МОЖНОСТ1 применения этого метода используется при записи прямое (в бло-. ке 5) и обратное (в блоке 6) при чтении транспортирования матрицы предварительно накопленных в блоке 5 и накопителе 1 сообщений, 2 з.п.ф-лы, 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1048516A1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании подсистем сбора и каналов ввода измерительной информации. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель 1, адрес0t e.1

1

Изобретение относится к вычислительной технике и может быть использовано при создании подсистем сбора и каналов ввода измерительной информции.

Цель изобретения - повышение надежности устройства.

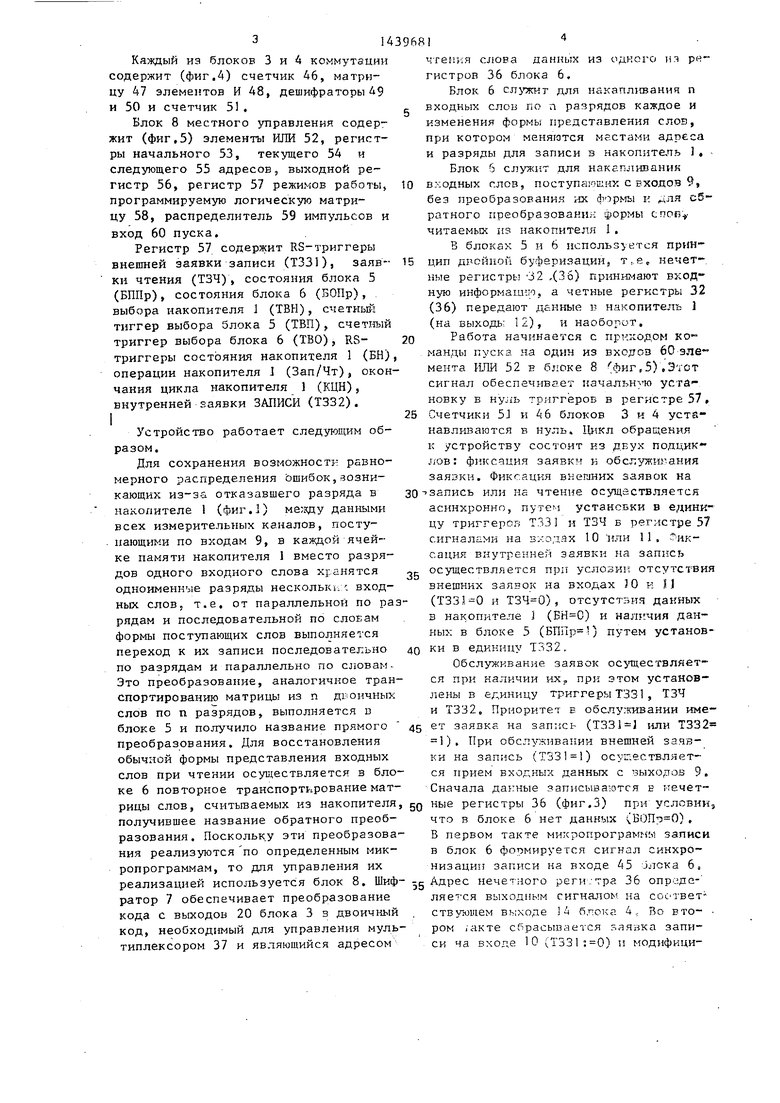

На фиг. показана функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема блока прямого преобразования данных; на фиг.З - функциональная схема блока оратного преобразования данных; на фиг. 4 - функциональные схемы каяодого из

блоков коммутации; на фиг . 5 - функций- нальная схема блока местного управления .

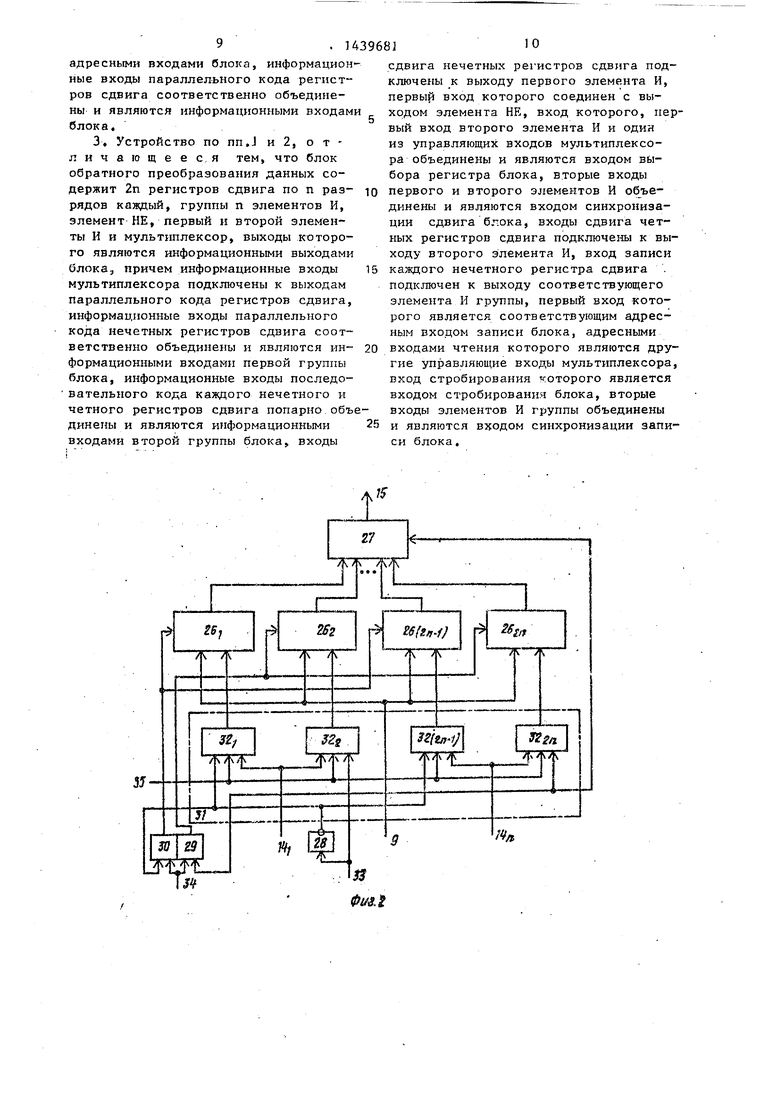

Устройство содержит (фиг.) накопитель 1, адресный блок 2, пе{)вьп1 3 и второй 4 блоки коммутации, блоки прямого 5 и обратного 6 преобразования данных, шифратор 7 и блок 8 местного управления, информационные входы 9, записи ,10 и чтения И информационные выходы 12.

Кроме того, устройство имеет (фиг,) счетный вход 13 и группу выходов 14i-J.4i, второго блока 4 комму

5

0 5

0

5

тации, информационные входы 15 и выходы 16 накопителя Д, адресные входы 17 чтения блока 6 обратного преобразования данных, счетный вход 18, вход 19 установки и выходы 20 и 21 первого блока 3 коммутации, вход 22 установки и выход 23 второго блока 4 коммутации, входы 24 модификации адреса адресного блока 2 и входы 25 и 25/J установки блока 8 местного управления .

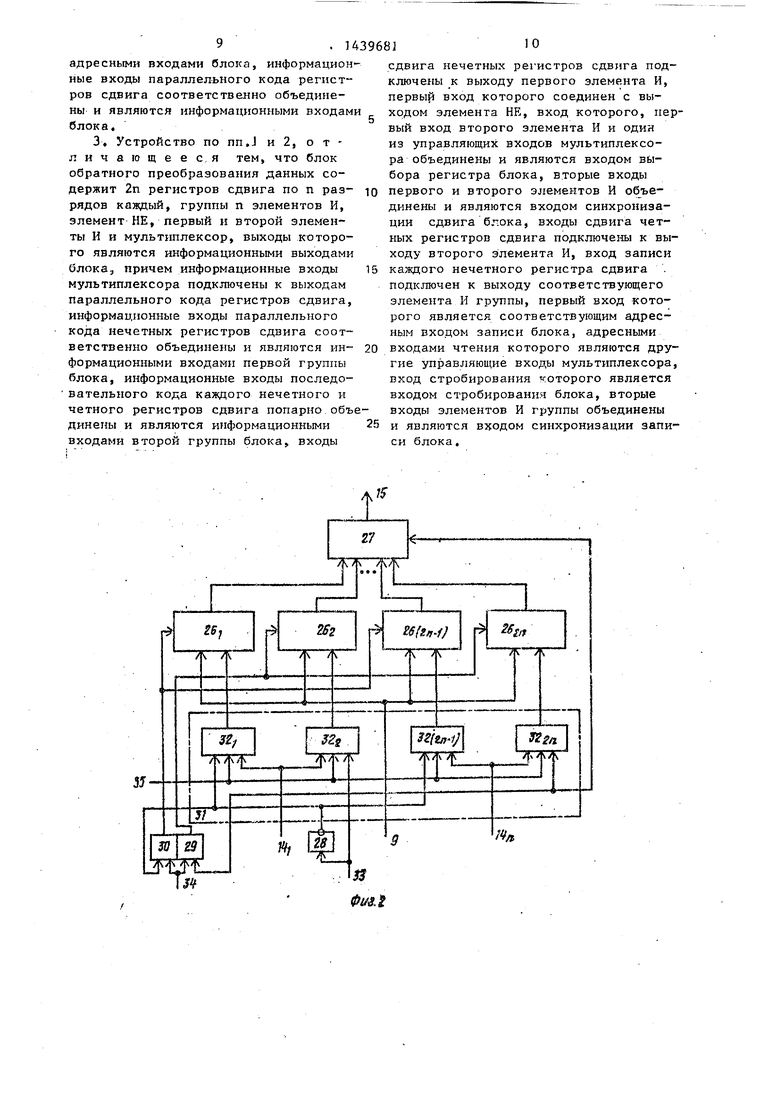

Блок 5 прямого преобразования данных содержит (фиг,2) регистры 26,-26 сдвига, мультиплексор 27, элемент НЕ 28, первый 29 и второй-30 элементы И и группу 31 элементов И ,j, а также вход 33 запуска и входы синхронизации сдвига 34 и синхронизации записи 35.

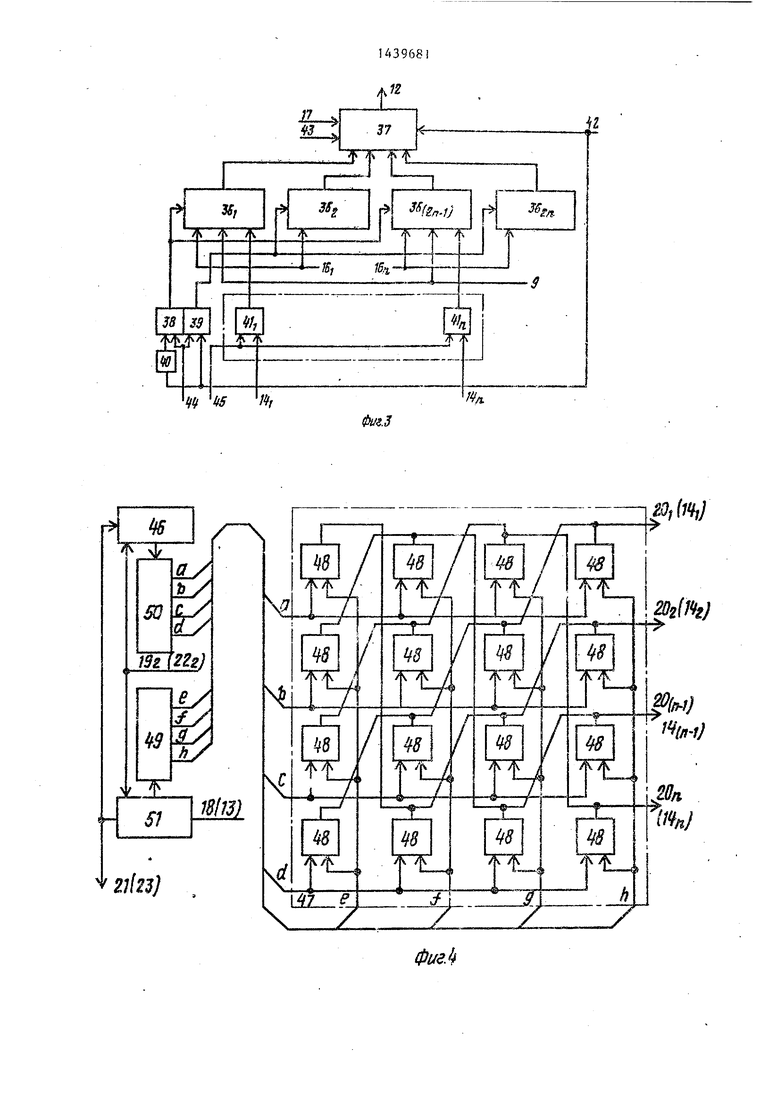

Блок 6 обратного преобразования данных содержит (фиг.З) регистры 36 сдвига, мультиплексор 37, первый 38 и второй 39 элементы И, элемент НЕ 40 и группу элементов И 41.,4 f, а также вход 42 запуска, вход 43 стробирования и входы синхронизации сдвига 44 и синхронизации записи 45.

314

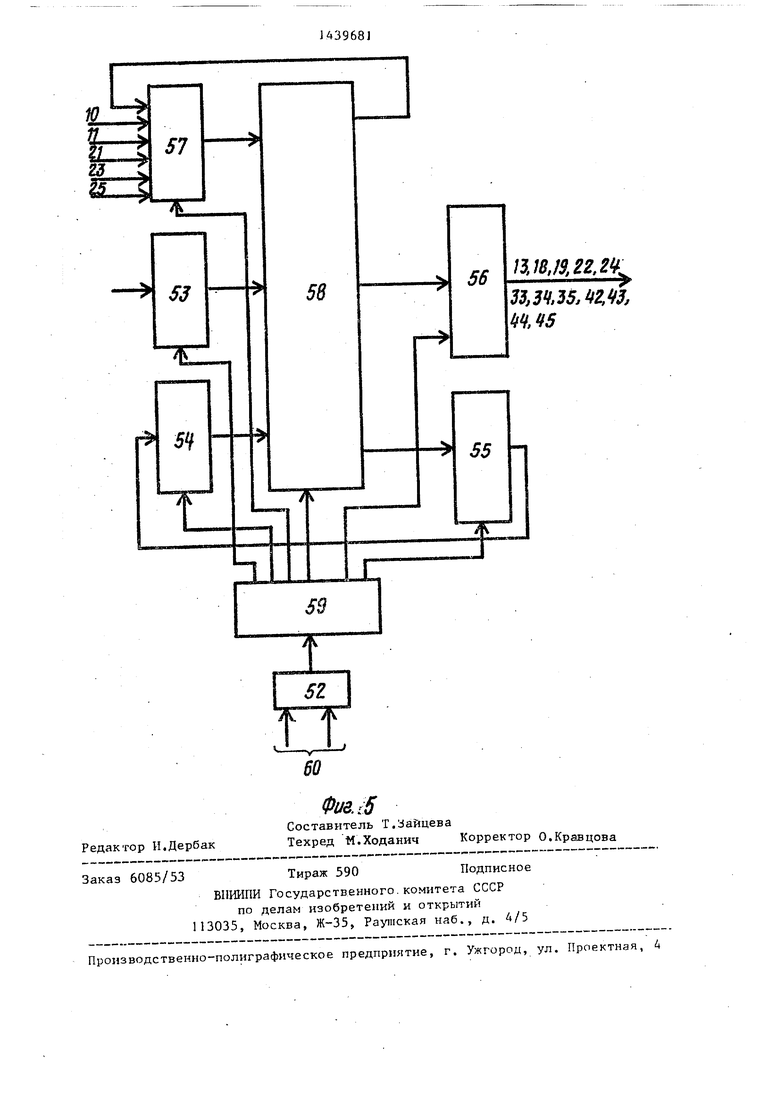

Каждый из блоков 3 и А коммутации содержит (фиг.А) счетчик 46, матрицу 47 элементов И 48, дешифраторы 49 и 50 и счетчик 51.

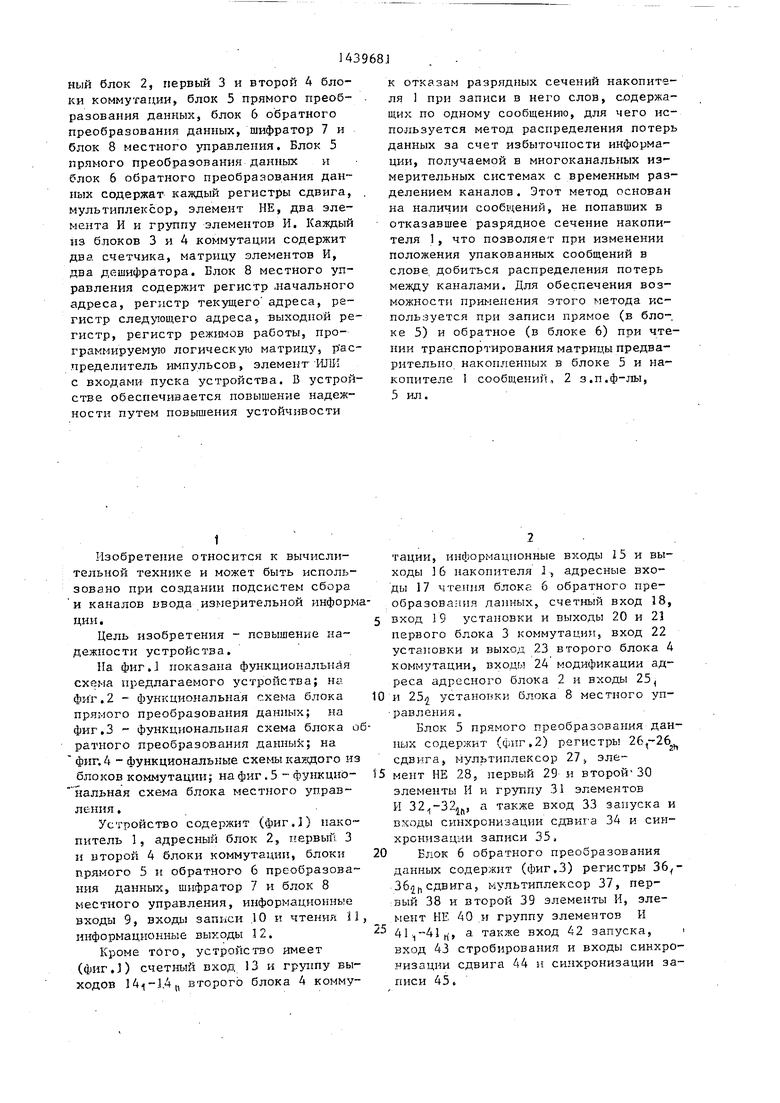

Блок 8 местного управления содержит (фиг,5) элементы ИЛИ 52, регистры начального 53, текущего 54 и следующего 55 адресов, выходной регистр 56, регистр 57 режимов работы, программируемую логическую матрицу 58, распределитель 59 импульсов и вход 60 пуска.

Регистр 57 содержит RS-триггеры внешней заявки записи (Т331), заявки чтения (ТЗЧ), состояния блока 5 (БППр), состояния блока 6 (БОПр), выбора накопителя J (ТВН), счетньш тиггер выбора блока 5 (ТБП), счетт1й триггер выбора блока 6 (ТВО), RS- триггеры состояния накопителя 1 (БН) операции накопителя J (Зап/Чт), окончания цикла накопителя 1 (КЦН), внутренней заявки ЗАПИСИ (Т332). 1

Устройство работает след-уюЕ им образом.

Для сохранения возможности равномерного распределения ошибок,возникающих из-за отказавшего разряда в накопителе 1 (фиг,1) ме;вду данными всех измерительных каналов, посту- . пающими по входам 9, в каждой ячейке памяти нако.пителя 1 вместо разрядов одного входного слова хранятся одноименные разряды нескольк.: . входных слов. т.е. от параллельной по рарядам и последовательной по словам формы поступающих слов выполняется переход к их записи последовательно По разрядам и параллельно по словам- Это преобразование, аналогичное транспортированию матриць из п двоичных

слов по п разрядов, выполняется в блоке 5 и получило название прямого преобразования. Для восстановления обычной формы представления входных слов при чтении осуществляется в блоОбслуживание заявок ос тдествляет- ся при налр;чии их, при этом установлены в единицу триггеры Т331 , ТЗЧ и Т332. Приоритет в обслу:кивании име- 45 ет заявка на зап1;сь (Т331 или 1332 1). При обслуживании внешней заявки на запись () осуг.ествляет- ся прием входных данных с зыходов 9. Сначала данные записываются Е нечетке 6 повторное транспортьрование матрицы слов, считьшаемых из накопителя, gg ные регистры 36 (фиг.З) при условии, получившее название обратного преоб- что в блоке 6 нет данных (). разования. Поскольк.у эти преобразования реализуются по определенным микропрограммам, то для управления их

В первом такте микpoпpoгpaм sы записи в блок 6 формируется сигнал синхро- низациь записи на входе 45 йлока 6,

реализацией используется блок 8. Шиф- -g Адрес нечетного реги:тра 36 опреде- ратор 7 обеспечивает преобразование ляет ся выходным сигналом на сос твет- кода с выходов 20 блока 3 в двоичный

с выходов 20 блока 3 код, необходимый для управления нуль- ром /акте cf типлексором 37 и являющийся адресом си ча входе

ствумшем выходе 1ч блока , Во вторасьшается заявка запи- 10 (Т331: 0) и модифици0

5

0

5

40

чтеп1-:я слова данных из одкого ия регистров 36 блока 6.

Блок 6 служит для накапливания п входных слов по п разрядов каждое и изменения формы представления слов, при котором меняются местами адреса и разряды для записи в накопите,пь 1 , Блок 6 служит для накапливания входных слов, поступающих с входов 9 без преобразования их формы н ля с5 ратного преобразования формы спов .- читаемых из накопителя 1.

В блоках 5 и 6 используется принцип дрсйной буферизации, т..е, нечет-, ные регистры 32 ,(36) прин5 1ают входную информаш-:ю, а четные регистры 32 (36) передают данные в накопитель 1 (на выходы 12), и наоборот.

Работа начинается с приходом ко- манды пуска на один из входов 60 эле мента РШИ 52 в блоке 8 ,фиг,5) «Этот сигнал обеспечивает начальную устЗ ковку в нуль триггеров в регистре 37, Счетчики 5J и 46 блоков 3 и 4 устанавливаются в нуль. Ц11кл обращения к устройству состоит из двух подцик- jiOB: фиксация заявки к обслуживания заявки. Фиксация внешних заявок на О запись или на чтение осущаствляется асинхронно, путс - установки в единк цу триггеров T33I и ТЗЧ в регистре 57 сигналами на входах 10 или 11, Фиксация внутренней заявки на запись осуществляется при услози ; отсутствия внешних заявок на входах 30 и П ( и ), отсутствия данных в накопителе I () и нахшчия данных в блоке 5 () путем установки в единицу Т332.

Обслуживание заявок ос тдествляет- ся при налр;чии их, при этом установлены в единицу триггеры Т331 , ТЗЧ и Т332. Приоритет в обслу:кивании име- 45 ет заявка на зап1;сь (Т331 или 1332 1). При обслуживании внешней заявки на запись () осуг.ествляет- ся прием входных данных с зыходов 9. Сначала данные записываются Е нечет5

gg ные регистры 36 (фиг.З) при условии, что в блоке 6 нет данных ().

ные регистры 36 (фиг.З) при условии, что в блоке 6 нет данных ().

В первом такте микpoпpoгpaм sы записи в блок 6 формируется сигнал синхро- низациь записи на входе 45 йлока 6,

реги:тра 36 опреде- сигналом на сос твет-

1ч блока , Во вторасьшается заявка запи- 10 (Т331: 0) и модифицируется адрес, т.е. содержимое счетчика 51 в блоке А« Если после этого позиикает сигнал переноса на выходе 23 счетчика 51 в блоке 4, то триггер БОПр в регистре 57 устанавливается в единицу (БОПр: 1), а счетчики 51 и Аб - D нуль. Если же переноса не было, то осуществляется возврат к подциклу фиксации заявок , т,ео записи данных в блок 6. При на- Л11чии сигнала , что свидетель- ствует о заполнении блока 6, и заявки записи ( или ) вход- 1ые данные записываются в блок 5.

В первом такте микропрограммы записи в блок 5 формируется сигнал.синхронизации записи на входе 35 блока 5 (фиг,2). Адрес регистра 26 определяется сигналом с соответствую- щего пх выходов 14 блока 4 и сигналом на входе 33. Если , т.е. сигнал на входе 33 равен нулю, то запись осуществляется в нечетные ре- гистрь 26, если же , то в чет- jUbie регистры 26. После этого анали- зируется состояние блока 5, Если в нем нет данных,, то модифицируется адрес в счетчнке 5J блока 4 и сбрасывается заявка записи () снгна лом на выходе 23, При возникновении переноса на выходе 23 счетчика 51 из меняется 3ia противоположное состояние триггера ТВП в регистре 57, а триггер БППр устанавливается в еди- ницу, В случае отсутствия переноса на выходе 23 осуществляется возврат к подциклу фиксации завки. При наличии данных в блоке 5 (БППр) и незанятости накопителя 1,() трнг- геры Зап/Чт и ТВН в регистре 57 устанавливаются в единицу и сбрасывается заявка записи на вкоде 10, тем самым содержимое старших разрядов регистров 26 через мультшшексор 11 передается из блока 5 на входы 15.накопителя 1 ,

, После окончания щшла накопителя 1 () в регнстре 57 устанав:- ливается в нуль триггер ТВН, подает- ся по входу 24 сигнал моднфикаци адреса записи в блоке 2, по сигналу па входе 13 модифицируется содержимо счетчиков 51 и 46 блока .4, осуществляется сдвиг данных в регистрах 26 и зади1ш фронтом этого снгнала сдвига на входе 34 записывается нуль (КЦ1-5: 0) в соответствующий триггер регистра 57 . Если обсл -живается

внешняя заявка (), то. после возникновения на вь коде 23 сигнала переноса счетчика 51 в блоке 4 luменяется на противоположное состояние триггера ТВП в регистре 57, При обслуживании внутренней заявки записи () микропрограмма перезаписи содержимого блока 5 в накопитель 1 циклически повторяется, начиная с анализа состояния блока 5 до появления сигнала переноса .из счетчика 5 в блоке 4, после чего сбрасывается внутренняя заявка () и триггер БППр (БППр: 0) в регистре 57, Затем анализируются сигналы на выходах 25 и 25. блока 2 о наличии данных в накопителе 1 . Если число занятых ячеек в накопителе 1 больше или равно п, то 13 триггер БИ регистра 57 записывается единица ( 1), в противном случае - , Па этом микропрограмма перезаписи из блока 5 в накопитель 1 заканчивается.

Микропрограмма чтения из блока 6 и перезаписи данных из накопителя 3 в блок б выполняется при отсутствгн заявок на запись ( или ) н наличии па входе 1 заявки чтения (ТЗЧ), Ecjr.ii 33 блоке 6 есть данные () и накопитель 1 свободен (), то триггер Зап/Чт устанавливается в пуль (Зан/Чт: 0), а триггер ТВН в едр П11ду () и сбрасывается заявка чтения (). Пос- ле окончания цикла чтения из накопителя 1 () формируется сигнал строб муль типлексора на входе 43 и сигнал синхронизации сдвига на входе 44 блока 6, При этом на вьтходы 12 через мультиплексор 37 передаются данные с выходов параллельного кода того из рег истров 36, адрес которого образован кодом с выходов 11 шифратора 7 и сигналом младшего разряда адреса с входа Если при этом со- стояние триггера , то в зависи- ;мости от кода нл входах 17 подключа- 1ется один из нечет1п-1х регистров 36, а в четные регистры 36 сигналом па входе 45 записывается с входов 6 носледозательн.ый код данных из накопителя 1, (в каж,13,ый регистр свое слово), а при ТВО I наоборот, Ч1 тают:;я дан.ые из четных регистров 36 н записываются в нечетные. Затем сбрасывается триггер ТВН (), модифицируется адрес записи в блоке 2 и содержимое счетчиков 51 и 46 в блоке 3

и сбрасывается триггер КЦН () Если нет сигнала заема на выходе 21 счетчика 51 блока 3, то анализируется сигнал наличия данных в накопителе 1 и в триггер БН записывается соответствующий код. Если же есть сигнал заема на выходе 21, то сначала анализируется состояние тригге- ipa БН в регистре 57 и изменяется на противоположное состояние триггера ТВО, а при триггер БОПр устанпв ливается в нуль (БОПр: 0). После этого также анализируется сигнал на- пичия данных в накопителе .

Таким образом, обеспечивается ус- 1тойчивость к отказам разрядных сече- ний накопителя J независимо от того, упаковывается в одно слово накопи- теля 1 несколько входных слов или од но входное слово, что повышает надежность устройства.

Формула изобретения

1, Буферное запоминающее устройство, содержащее накопитель, первый и второй блоки коммутации и адресный блок, выходы первой группы которого

соединены с адресными входами накопи- 30 2п регистров сдвига по п разрядов

теля, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок прямого преобразования данных, шифратор, блок обратного преобразования данных и блок местного управления, вход управления записью и вход управления чтением которого являются соответственно входом записи и входом чтения устройства, информационными выходами которого являются выходы блока обратного преобразования данных, информационные входы первой группы которого и информационные входы блока прямого преобразования объединены и являются информационными входами устройства, причем информационные входы и информационные выходы накопителя подключены соответственно к выходам блока

прямого преобразования данных и к ин- 50 сора объединены и являются входом ры- формационным входам второй группы блока обратного преобразования данных, адресные входы записи которого соединены с выходами группы второго блока коммутации и адресными входами блока прямого преобразования данных, вход запуска, вход -синхронизации сдвига и вход синхронизации записи которого подключены к выходам первой- .

бора регистра блока, вторые входы первого и второго элементов И объединены и являются входом синхронизации сдвига блока, вторые входы элемен- 55 тов И группы объединеНь и являются входом синхронизации записи блока, третьи входы предыдущего нечетного и последующего четного элементов И группы попарно объединены и являются

143968J

0

5

группы блока местного управления,вы-, ходы второй группы которого соедине- ны соответственно с входом запуска, входом синхронизации записи, входом синхронизации сдвига и входом строби рования блока обратного преобразования данных, адресные входы чтения которого подкл че1гы к выходам шифратора, входы которого соединены с выходами группы первого блока коммутации, выход которого подключен к первому счетному входу блока местного управления, выходы третьей группы которого соединены со счетным входом и входом установки первого блока кo мyтa- ции, выходы четвертой группы блока местного управления подключены к входу установки м счетному входу второго блока коммутации, выход которого соединен с вторым счетным входом блока местного управления, первый и второй входы установки и вы.ходы пятой группы которого подключены к выходам 5 второй группы и входам модификации адреса адресного блока.

каждый, где п - разрядность входного слова, мультиплексор, элемент НЕ, группу элементов И по числу регистров сдвига, первый и второй элементы И, причем информационные входы мультиплексора подключены к выходам последовательного кода регистров сдвига, вход записи каждого из которых соединен с выходом одноименного элемента И группы, входы сдвига нечетных регистров сдвига соединены с выходом второго элемента И, первый вход которого и первые входы нечетных элементов И группы подключены к выходу элемента НЕ, входы сдвига четных регистров сдвига соединены с выходом пер- ,, вого элемента И, первый вход котороЧ го, первые входы четных элементов И группы и управляющий вход мультиплексора объединены и являются входом ры-

бора регистра блока, вторые входы первого и второго элементов И объединены и являются входом синхронизации сдвига блока, вторые входы элемен- тов И группы объединеНь и являются входом синхронизации записи блока, третьи входы предыдущего нечетного и последующего четного элементов И группы попарно объединены и являются

адресными входами блока, информационые входы параллельного кода регистров сдвига соответственно объединены и являются информационными входа блока.

10

сдвига нечетных регистров сдвига подключены к выходу первого элемента И, первый вход которого соединен с выходом элемента НЕ, вход которого, первый вход второго элемента И и один из управляющих входов мультиплексора объединены и являются входом выбора регистра блока, вторые входы первого и второго элементов И объединены и являются входом синхронизации сдвига блока, входы сдвига четных регистров сдвига подключены к выходу второго элемента И, вход записи каждого нечетного регистра сдвига . подключен к выходу соответствующего элемента И группы, первый вход которого является соответствующим адресным входом записи блока, адресными входами чтения которого являются другие управляющие входы мультиплексора, вход стробирования которого является входом стробирования блока, вторые входы элементов И группы объединены и являются входом синхронизации записи блока.

А

t

±.

М

т

9

А/

/ч

18113)

2ll23)

o.d h)

Фиг

| Буферное запоминающее устройство | 1981 |

|

SU982095A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1049968A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1988-11-23—Публикация

1987-01-12—Подача