Изобретение относится к вычисли- отельной технике и может, быть использовано для имитации информационных сигналов на входах цифровых устройств при их автономной настройке, проверке работоспособности и диагностирования неисправностей.

Цель изобретения - сокращение аппаратурных затрат устройства.

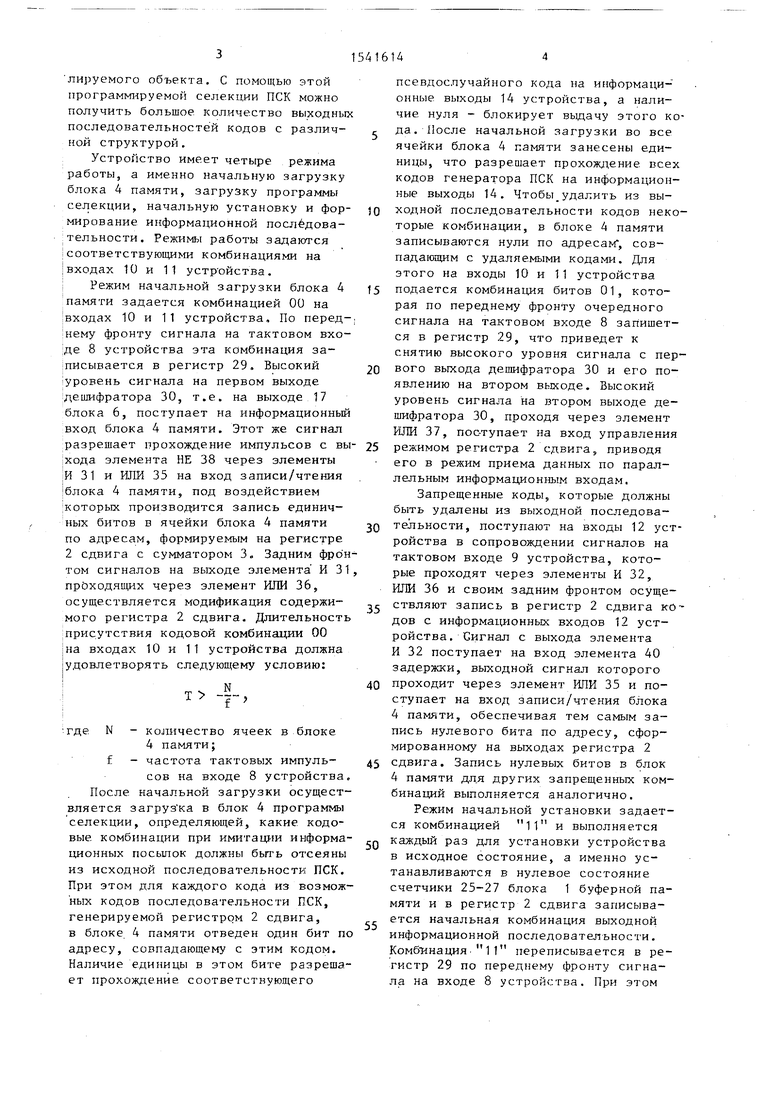

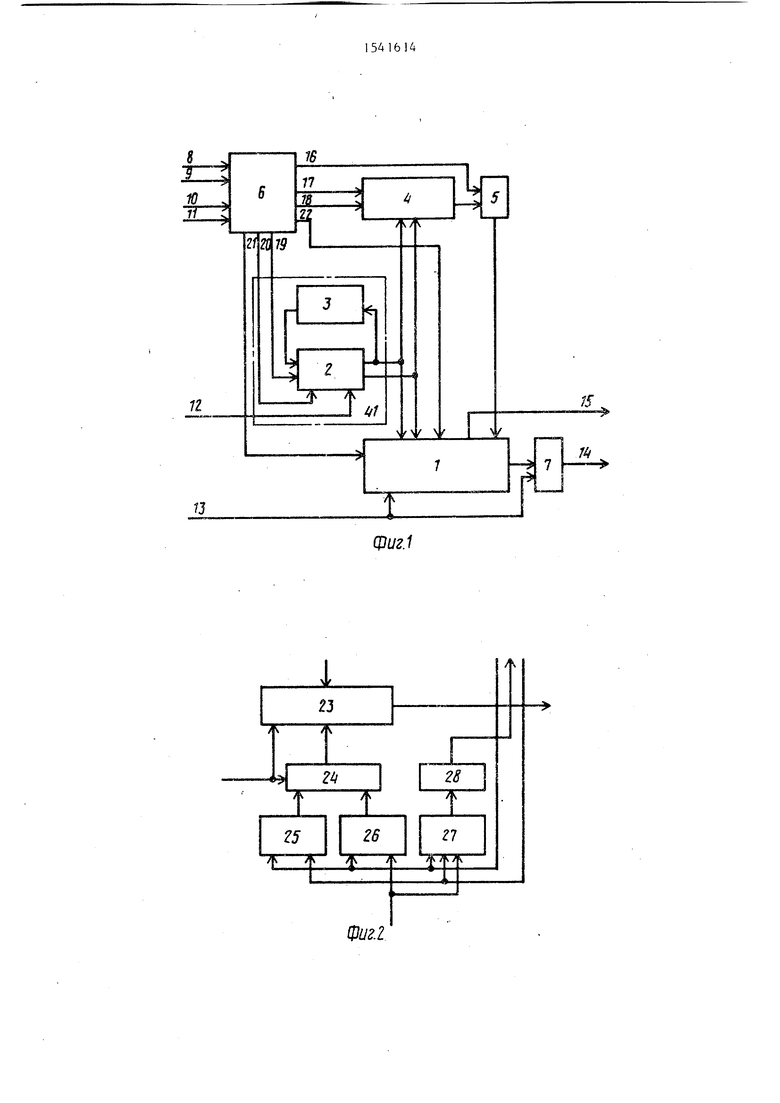

На фиг.1 приведена блок-схема устройства ; на фиг. 2 - схема блока буферной памяти; на фиг.З - схема блока управления.

Устройство содержит блок 1 буферной памяти, регистр 2 сдвига, сумматор 3 по модулю два, блок 4 памяти, элемент И 5, блок 6 управления, группу элементов И 7, тактовые входы 8 и 9, входы 10 и 11 задания режима работы, информационные входы 12, вход 13 чтения, информационные выходы 14, выход 15 синхроимпульсов устройства, выходы 16-22 блока 6 управления .

Блок 1 буферной памяти содержит блок 23 памяти, мультиплексор 24, счетчик 25 адреса записи, счетчик 26 адреса чтения, счетчик 27 объема и дешифратор 28.

Блок 6 управления содержит регистр 29, дешифратор 30, элементы И 31-33, элемент 34 задержки, элементы ИЛИ 35-37, элемент НЕ 38, одновибратор 39, элемент 40 задержки. Регистр 2 и сумматор J образуют генератор 41 псевдослучайного кода (фиг.1).

Устройство работает следующим образом.

В устройстве в основу формирования информационных сигналов для настраиваемых и контролируемых объектов положено программируемое отсеивание из исходной последовательно- , сти псевдослучайных кодов (ПСК), получаемой с помощью генератора 41 ПСК на базе регистра 2 сдвига с сумматором 3, кодовых комбинаций, которые являются запрещенными для контроi

(Л

ел

4-

м

О Јь

лируемого объекта. С помощью этой программируемой селекции ПСК можно получить большое количество выходных последовательностей кодов с различ- ной структурой.

Устройство имеет четыре режима работы, а именно начальную загрузку блока 4 памяти, загрузку программы селекции, начальную установку и фор- мирование информационной последовательности. Режимы работы задаются соответствующими комбинациями на входах 10 и 11 устройства.

Режим начальной загрузки блока 4 памяти задается комбинацией 00 на входах 10 и 11 устройства. По переднему фронту сигнала на тактовом входе 8 устройства эта комбинация записывается в регистр 29. Высокий уровень сигнала на первом выходе дешифратора 30, т.е. на выходе 17 блока 6, поступает на информационный вход блока 4 памяти. Этот же сигнал разрешает прохождение импульсов с вы хода элемента НЕ 38 через элементы И 31 и ШШ 35 на вход записи/чтения блока 4 памяти, под воздействием которых производится запись единичных битов в ячейки блока 4 памяти по адресам, формируемым на регистре 2 сдвига с сумматором 3„ Задним фронтом сигналов на выходе элемента И 31 проходящих через элемент ИЛИ 36, осуществляется модификация содержи- мого регистра 2 сдвига. Длительность присутствия кодовой комбинации 00 на входах 10 и 11 устройства должна удовлетворять следующему условию:

т -Ј- Т f ,

где N - количество ячеек в блоке

4 памяти; f - частота тактовых импуль-

сов на входе 8 устройства. После начальной загрузки осуществляется загруз ка в блок 4 программы селекции, определяющей, какие кодовые комбинации при имитации информа- ционных посылок должны быть отсеяны из исходной последовательности ПСК. При этом для каждого кода из возможных кодов последовательности ПСК, генерируемой регистром 2 сдвига, в блоке 4 памяти отведен один бит по адресу, совпадающему с этим кодом. Наличие единицы в этом бите разрешает прохождение соответствующего

5 0 5 о

0

5

5

псевдослучайного кода на информационные выходы 14 устройства, а наличие нуля - блокирует выдачу этого кода. После начальной загрузки во все ячейки блока 4 памяти занесены единицы, что разрешает прохождение всех кодов генератора ПСК на информационные выходы 14. Чтобы удалитъ из выходной последовательности кодов некоторые комбинации, в блоке 4 памяти записываются нули по адресам, совпадающим с удаляемыми кодами. Для этого на входы 10 и 11 устройства подается комбинация битов 01, которая по переднему фронту очередного сигнала на тактовом входе 8 запишется в регистр 29, что приведет к снятию высокого уровня сигнала с первого выхода дешифратора 30 и его появлению на втором выходе. Высокий уровень сигнала на втором выходе дешифратора 30, проходя через элемент ИЛИ 37, пос-тупает на вход управления режимом регистра 2 сдвига, приводя его в режим приема данных по параллельным информационным входам.

Запрещенные коды,, которые должны быть удалены из выходной последовательности, поступают на входы 12 устройства в сопровождении сигналов на тактовом входе 9 устройства, которые проходят через элементы И 32, ИЛИ 36 и своим задним фронтом осуществляют запись в регистр 2 сдвига кодов с информационных входов 12 устройства. Сигнал с выхода элемента И 32 поступает на вход элемента 40 задержки, выходной сигнал которого проходит через элемент ИЛИ 35 и поступает на вход записи/чтения блока 4 памяти, обеспечивая тем самым запись нулевого бита по адресу, сформированному на выходах регистра 2 сдвига. Запись нулевых битов в блок 4 памяти для других запрещенных комбинаций выполняется аналогично.

Режим начальной установки задается комбинацией 11 и выполняется каждый раз для установки устройства в исходное состояние, а именно устанавливаются в нулевое состояние счетчики 25-27 блока 1 буферной памяти и в регистр 2 сдвига записывается начальная комбинация выходной информационной последовательности. Комбинация 11 переписывается в регистр 29 по переднему фронту сигнала на входе 8 устройства. При этом

51

снимается высокий уровень сигнала с второго выхода дешифратора 30 и появляется высокий уровень на его третьем выходе, который поступает на выход 22 блока 6 для установки в исходное состояние блока 1 буферной памяти, На информационных входах 12 устройства до задания режима начальной установки должна быть установлена начальная комбинация последовательности, которая записывается в регистр 2 сдвига по заднему фронту сигнала на третьем выходе дешифратора 30, прошедшего элемент ИЛИ 36.

После выполнения загрузки программ селекции и начальной установки устройства на входы 10 и 11 устройства устанавливается комбинация 10 битов, которая по переднему фронту очередного сигнала на тактовом входе 8 запишется в регистр 29, что приведет к снятию высокого уровня сигнала с третьего выхода дешифратора 30 и его появлению на четвертом выходе. Высокий уровень сигнала на четвертом выходе дешифратора 30 разрешает прохождение тактовых сигналов с входа 8 через элемент И 33 на выход 21 и через элементы И 33 и ИЛИ 36 на выход 19 блока 6. По переднему фронту сигнала на выходе элемента И 33, задержанного на элементе ЗА задержки, срабатывает одновибратор 39, выходной сигнал которого поступает на выход 16 бло ка 6. Низкий уровень сигнала на выходе элемента ИЛИ 37 обеспечивает работу регистра 2 сдвига в режиме сдвига информации, который осуществляется по заднему фронту сигнала на выходе 19 блока 6. При этом на выходах регистра 2 сдвига с сумматором 3 по модулю два в обратной связи формируются элементы последовательности ПСК. Каждый псевдослучайный код на выходах регистра 2 сдвига поступает на адресные входы блока 4 памяти и информационные входы блока 23 памяти. Низкий уровень сигнала на выходе 18 блока 6 задает для блока 4 памяти режим чтения.

Сигнал на выходе 21 блока 6 поступает в блок 1 буферной памяти на адресный вход мультиплексора 24 и вход записи блока 23 памяти. Мультиплексор 24 подключает к адресным входам блока 23 памяти счетчик 25 адреса записи. По адресу, храняще6146

муся в счетчике 25, в блок 23 памяти записывается псевдослучайной код с выходов регистра 2 сдвига. На информационном выходе блока ч памяти появляется содержимое ячейки, адрес которой равен содержимому регистра 2 сдвига. Выходной сигнал блока 4 памяти подается на вход элеменд та И 5. Сигнал на выходе 16 блока 6 проходит через элемент И 5 на вход модификации адреса записи блока 1 буферной памяти, если на выходе блока 4 памяти установлен сигнал логи5 чес,кой 1, т.е. на выходах регистра 2 сдвига сформирован разрешенный псевдослучайный код. Если на выходе блока 4 памяти установлен сигнал логического О, т.е. на выходах ре0 гистра 2 сдвига присутствует запрещенный код, прохождение сигнала с выхода 16 блока 6 через элемент И 5 блокируется. При разрешенном псевдослучайном коде импульс с выхода эле5 мента И 5 увеличивает на единицу содержимое счетчика 25 адреса записи и счетчика 27 объема блока 1 буферной памяти.

Таким образом, по каждому такто0 вому импульсу на сихровходе регистр 2 сдвига с сумматором 3 по модулю два формирует псевдослучайный код, который независимо от программы селекции запоминается в блоке 23 памяти. Однако адрес записи и объем хранящейся информации в блоке 1 буферной памяти модифицируется только при разрешенных комбинациях, т.е. в блоке 1 буферной памяти остаются

Q лишь разрешенные псевдослучайные коды. После накопления m разрешенных кодов в блоке 23 памяти на выходе дешифратора 28 формируется сигнал логической 1. Дешифратор 28 форми5 РУет сигнал логической 1, если содержимое счетчика 27 объема больше или равно т, т.е. в блоке 23 памяти присутствует m слов, при этом формируется на управляющем выходе

Q 15 сигнал, который сообщает объекту контроля, что из устройства может быть считан информационный блок из m слов. Обмен имитируемой информацией между устройством и объектом контроля осуществляется блоками по

5

5

m слов.

После получения разрешения на чтение данных объект контроля выдает на вход 13 чтения данных пачку из

tn синхросигналов. Для синхронизации устройства и объекта контроля необходимо, чтобы тактовые импульсы на входе 8 и синхроимпульсы на входе 13 формировались из одной тактовой Частоты (для этого может быть использован тактовый генератор объек- ta контроля). В этом случае опера- ton записи и чтения данных из блока 23 памяти довольно просто разнести по времени. При чтении данных из устройства на входе записи блока 23 памяти присутствует сигнал логиче- фкого О. При этом блок 23 памяти находится в режиме чтения, а мультиплексор 24 подключает к адресным йходам блока 23 памяти выходы счетчика 26 адреса чтения. На выходах Флока 23 памяти устанавливается код хранящийся в нем по адресу, формируемому счетчиком 26 адреса чтения. С приходом на вход 13 чтения Данных синхроимпульса открываются Элементы И 7 группы и на информационных выходах 14 устанавливается код, считанный из блока 1 буферной цамяти. По заднему фронту синхроимпульса увеличивается на единицу содержимое счетчика 26 адреса чтения и уменьшается на единицу содержимое Счетчика 27 объема. Аналогичным о.б- разом из устройства считывается очередной код.

По окончании информационного блока из m кодов объект контроля про- йеряет состояние выхода 15. Если на выходе 15 установлен сигнал логической 1, то начинается чтение из устройства следующего блока данных. 3 противном случае объект контроля переходит в режим ожидания. При Имитации информации блок 1 буферной памяти осуществляет сглаживание выходного информационного потока. В результате отсеивания запрещенных комбинаций из последовательности ИСК формируется неравномерный информационный поток, который в ряде случаев не может быть использован для ввода в контролируемые устройства, н то время как с информационных выходов 14 происходит выдача с рав- номерной частотой.

Формула изобретения

Устройство для задания тестовых воздействий, содержащее блок памяти, генератор псевдослучайного кода, элемент И, группу элементов И, блок буферной памяти и блок управления, первый и второй тактовые входы которого являются соответственно первым и вторым входами тактовых импульсов устройства, первый и второй входы элемента И соединены соответственно с первым выходом блока управления и

5 выходом блока памяти, выход элемента И подключен к вх цу модификации адреса записи блока буферной памяти, вход записи которого соединен с вторым выходом блока, управления, инфор0 мационный вход блойа буферной памяти соединен с выходом генератора псевдослучайного кода, группа информационных выходов блока буферной памяти соединена с первыми входами

5 элементов И группы, вторые входы которых объединены и являются входом чтения устройства и соединены с дом чтения блока буферной памяти, выход признака заполнения которого яв0 ляется выходом синхроимпульсов устройства, выходы элементов И группы соединены с группой информационных выходов устройства, отличающееся тем, что, с целью сокра5 щения аппаратурных затрат устройства, первый и второй входы задания режима работы блока управления соединены соответственно с входами задания режима работы устройства, тре0 тий и четвертый выходы блока управления соединены соответственно с информационным входом и входом записи блока памяти, адресные входы которого подключены к выходу генератора

5 псевдослучайного кода, информационный вход которого соединен с информационным входом устройства, тактовый вход и вход записи генератора псевдослучайного кода подключены со

ответственно к пятому и шестому выходам блока управления, седьмой выход которого соединен с входом установки блока буферной памяти.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых устройств | 1988 |

|

SU1509901A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сортировки информации | 1986 |

|

SU1606972A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

Изобретение относится к вычислительной технике и может быть использовано для имитации информационных сигналов на входах цифровых устройств при их автономной настройке, проверке работоспособности и диагностировании неисправностей. Цель изобретения - сокращение аппаратурных затрат устройства за счет изменения функциональных связей между его составными частями. Устройство содержит блок буферной памяти, генератор псевдослучайного кода, блок памяти, блок управления, группу элементов И, элемент И. 3 ил.

| Имитатор абонентов | 1977 |

|

SU693365A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-04-11—Подача