Ияобретение относится к вычисли- tejibHOH технике и может быть использовано для цифровой обработки сигналов.

Цель изобретения - расширение функциональных возможностей,

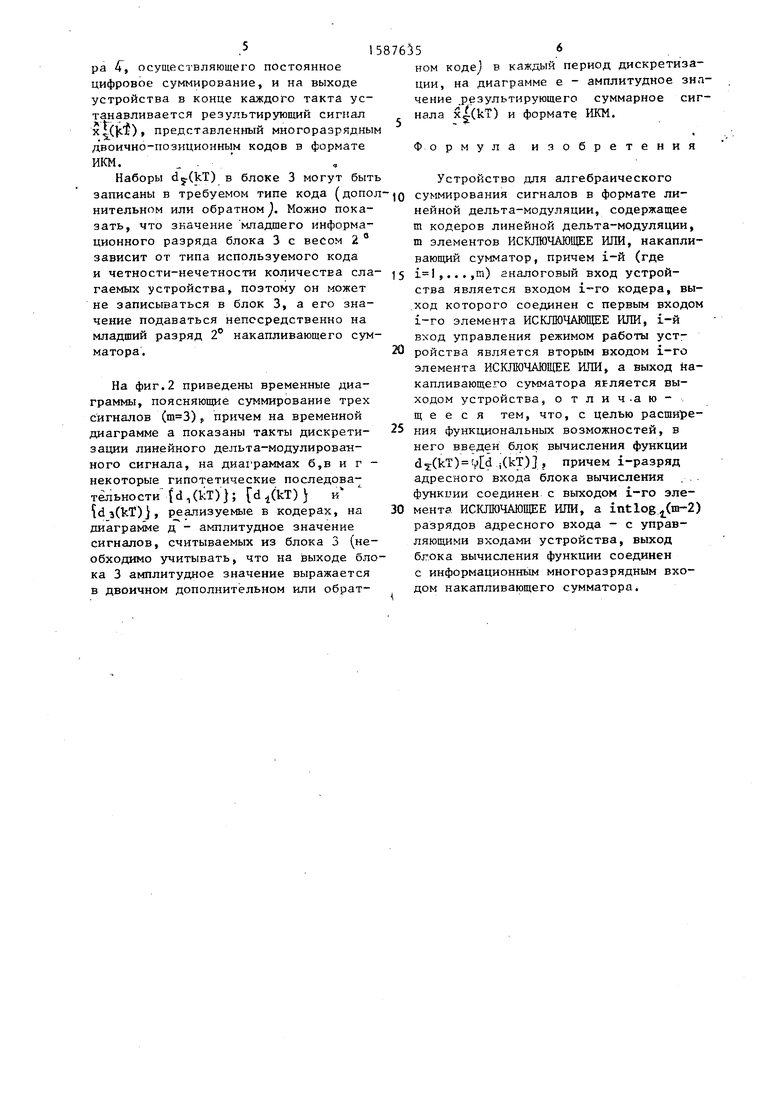

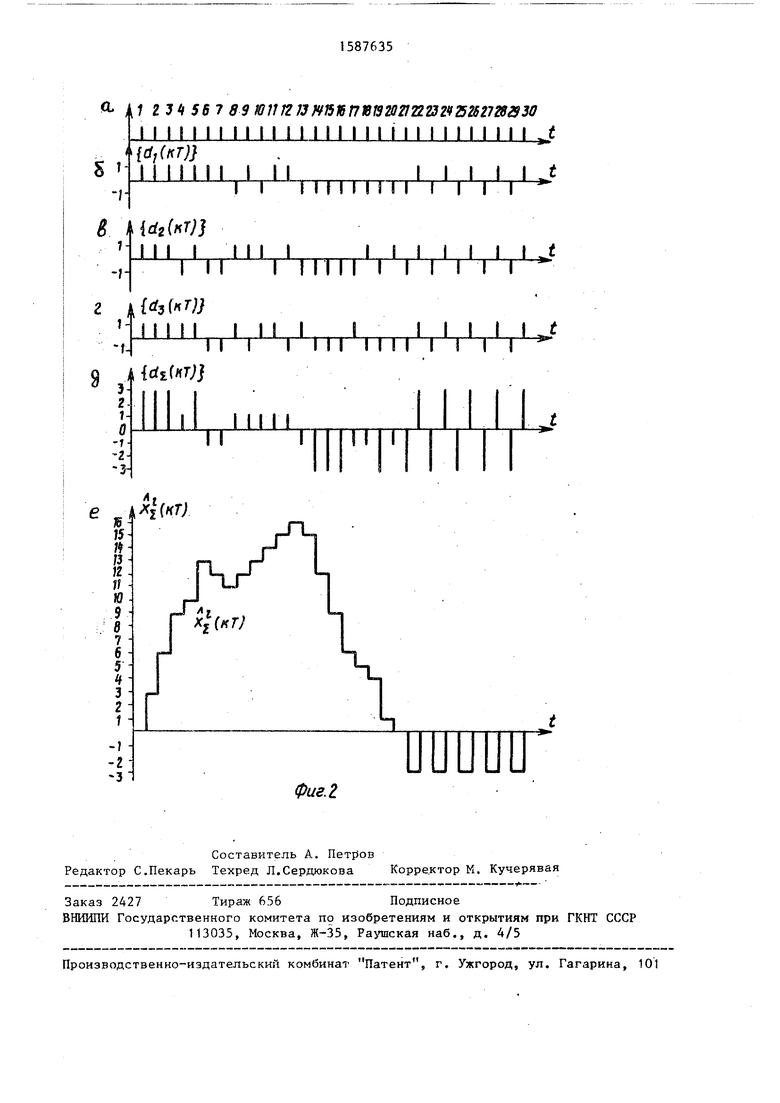

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - йременные диаграммы, поясняющие сум- ушрование в формате линейной дельта |10ДУЛЯЦИИ.

I Устройство содержит m кодеров 1, i|i элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, блок вычисления функции d(kT) (у C ; (kT)J Накапливающий сумматор 4, группу ана jjiorcBbix входов 5, группу входов 6 Отправления режимом работы, группу равляющих входов 7, выход 8. : Алгоритм суммирования в формате |;ельта-модуляции можно .представить следующим образом. Если x.(t) (где . о. ,т) аналоговые сигналы такие Что их частотные полосы ограничены сверху величиной f etKc °™ преобразуются при помощи кодера дельта-мо yляции в дельта-модулированные последовательности

: Jd./nT) ),..., („,(пТ)),

де п - номер отсчета; период дис сретизации;

f - частота дискретизации, причем f ., ,

то сумму аналоговых сигналов ж (пТ; m ,2-

1 x.(t) можно с требуемой точносUe ..

тью выразить через оценки сиг-Н 1лов

),.... ) и представляющие собой 1-разрядные двоично-позицион- ные импульсные кодомодулированные (ИКМ) сигнапы

5« (пТ)1(пТ), (1)

2. (с1

где х(пТ) id .(kT).

- КаО

Выражение (1) можно представить в виде

X (пТ)5 4 (n-i)T +d(nT) , (2)

5

где d(nT) d I (пТ) - шаг квантования суммарного сигнала за п-й пери дискретизации. Учитывая, что d j(kT ,1, где О и 1 имеют логичекий смысл и О соотвествует -1, а 1 - I, где +1 и - - номированный шаг квантования (одна уловная единица), можно показать, ч

-(kT) представляют собой многоуровневые сигналы, и количество различных уровней d(f.I) f определяемое различными наборами dj(kT), будет равняться (т+1), следовательно, количество разрядов, необходимых для представления d (пТ), составит

c intlo r (т+1) .

Устройство для алгебраического суммирования сигналов в формате линейной дельта-модуляции работает следующим образом.

До начала работы необходимо произвести установку группы входов 6 управления режимом работы по следующему правилу: если i-e слагаемое должно участвовать в общей сумме со знаком -, то соответствующая дельта-мо дулированная последовательность должна быть инвертирована и, следовательно, сигнал В.1, если же i-e слагаемое участвует в общей сумме со знаком +, то В.0, и соответствующая ему дельта-модулированная последовательность поступает на адресный вход блока 3 без изменений. Б блоке 3 записана функция )

(kT), показывающая зависимость шага квантования суммарного сигнала от различных наборов di(kT)npH этом наборы di(kT) можно рассматривать как ряд адресов, по которым записаны соответствующие значения d(l ,T) . Kpobje этого, можно организовать произвольный выбор количества параллельно сумми- ,. руемых сигналов в диапазоне 2,... .,т. Для зтого группа управляющих входов 7 устройства используется в качестве старших разрядов адоесного входа блока 3 AJ, где ...,Ьэ а intloga(m-2).

Аналоговые сигналы преобразуются в кодерах 1 в дельта-модулированные последовательности, i-й элемент ИС- КЛЮЧАадЕЕ ИЛИ 2 служит для определения знака i-ro аналогового сигнала (в зависимости от сигнала управления режимом работы В . Полученные дельта-модулированные последовательности являются младшими разрядами адресного входа блока 3. Блок 3, накапливающий сумматор 4 и кодеры 1 тактируются частотой дискретизации. С выхода блока 3 в каждый период дискретизации считывается шаг квантования суммарного сигнала, который подается на вход накапливающего сумматоpa 4, осуществляющего постоянное цифровое суммирование, и на выходе устройства в конце каждого такта устанавливается результирующий сигнал л t

V

), представленный многоразрядным двоичио-позиционны м кодов в формате ИКМ. , .

Наборы dj-CkT) в блоке 3 могут быть записаны в требуемом типе кода (ДОПОЛ нительном или обратном. Можно показать, что значение младшего информационного разряда блока 3 с весом 2 зависит от типа используемого кода и четности-нечетности количества слагаемых устройства, поэтому он может не записываться в блок 3, а его значение подаваться непосредственно на младший разряд 2° матора.

накапливающего сум

На фиг.2 приведены временные диаграммы, поясняющие суммирование трех сигналов (), причем на временной диаграмме а показаны такты дискретизации линейного дельта-модулирован- ного сигнала, на диаграммах б,в и г - некоторые гипотетические последовательности fd (kT)) ; d.i( kT)) и 3(kT)}, реализуемые в кодерах, на диагра1«ме д - амплитудное значение сигналов, считываемых из блока 3 (необходимо учитывать, что на выходе блока 3 амплитудное значение выражается в двоичном дополнительном или обрат5876 5

ном коде в каждый период дискретизации, на диаграмме е - амплитудное значение ,результирующего суммарное сиг- , нала x/(kT) и формате ИКМ.

Формула изобретения

Устройство для алгебраического суммирования сигналов в формате линейной дельта-модуляции, содержащее m кодеров линейной дельта-модуляции, m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, накапливающий сумматор, причем i-й (где

i,...,Ti) аналоговый вход устройства является входом i-ro кодера, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, i-й вход управления режимом работы устройства является вторым входом i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход Накапливающего сумматора яЕляется выходом устройства, о т л и ч .а ю - щ е е с я тем, что, с целью расщи1реНИН функциональных возможностей, в него введен блок вычисления функции d(kT) i(kT) , причем i-разряд адресного входа блока вычисления функиии соединен с выходом i-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а intlog(m-2) разрядов адресного входа - с управляющими входами устройства, выход блока вычисления функции соединен с информационньш многоразрядным входом накапливающего сумматора.

tt.

1 г IS it 567 89IOn 3f K№f7ie02ffZf22232V25№27Z8ff30 I I I I I I I I I 1 I 1 I M I I I M M I I II I M Jt

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр | 1986 |

|

SU1387174A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодово-модулированный сигнал | 1986 |

|

SU1347190A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1989 |

|

SU1661969A1 |

Изобретение относится к вычислительной технике и может быть использовано для цифровой обработки сигналов. Цель изобретения - расширение функциональных возможностей. Устройство, содержащее M кодеров 1, M элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, обеспечивает увеличение количества параллельно суммируемых сигналов до M и произвольный выбор их количества в диапазоне от 2 до M. Достигается это введением блока вычисления функции D @ (KT)=Ψ [D I(KT)], адресной информацией которого являются все возможные наборы дельта-модулированных последовательностей суммируемых сигналов и количество суммируемых сигналов, а вычисляемой информацией-амплитудное значение суммарного сигнала в произвольный период дискретизации. 2 ил.

I .1 . U

I . I . I . I .

M M M I I I I I

iiffyi T)}

1- fJM M . „ I .1 i . I

I . I . I . ( .

1 I I I I M I M I I I I I

Э 2

tH

{dEWj

ULLUL

-T -2-3I I

e ()

15- If- 13- 12 - If - Ю 9 В

7 - 6 - 5

- 3 - 2- f -) - -2- -3

фиг. г

I . I . I . I . I J

I I I I

I . I . I . ( . I

I I I I

I I

иииш

| Joseph L., Donald L., Carod- nick J | |||

| Realization of ADM Arithmetic Signal Processors | |||

| - IEEE Trans on Comm, 1979, vol | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Погрибной В.A., Яковлев В.П | |||

| Дельта-модуляция при цифровой фильтрации, корреляционном анализе и дискретном преобразовании Фурье | |||

| - Зарубежная электроника, 1987, № 8 | |||

| , | |||

Авторы

Даты

1990-08-23—Публикация

1988-07-07—Подача