Изобретение относится к вычисли- т0льной технике и предназначено для преобразования кодов,

: Целью изобретения является сокра- щение аппаратурных затрат.

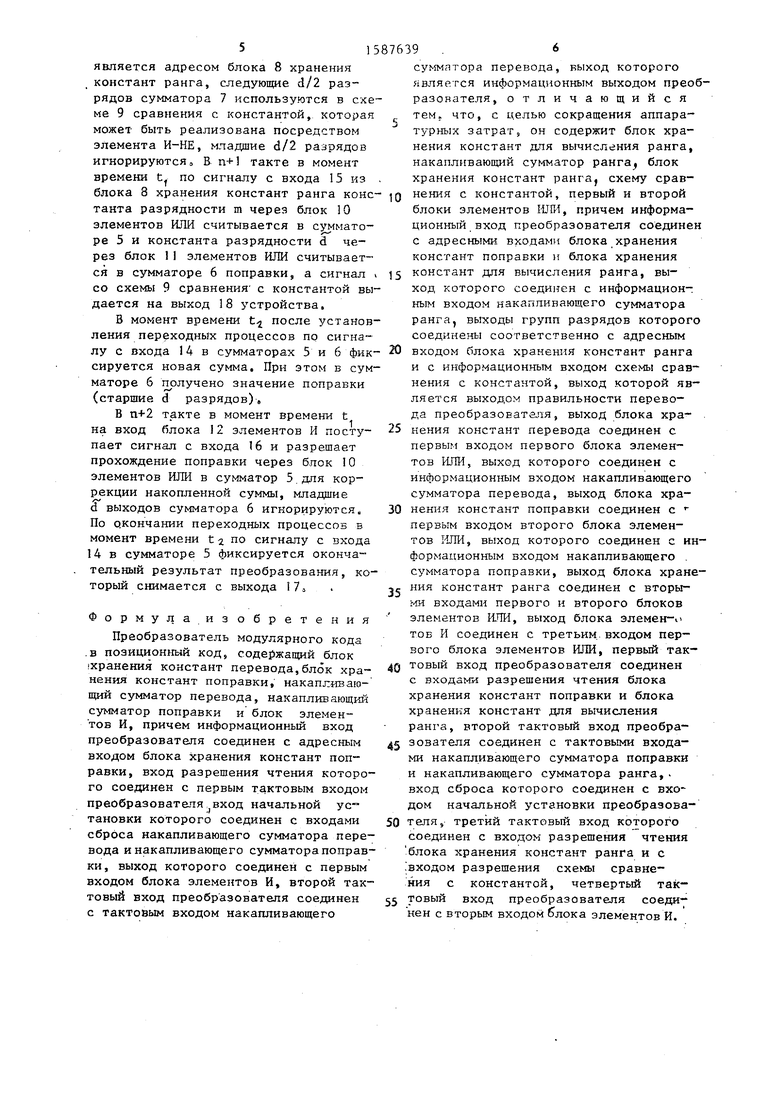

На чертеже представлена схема преобразователя модулярного кода в позиционный код,

; преобразователь содержит информа- ц онный вход 1 преобразователя, блок 2iхранения констант перевода, блок 3 хранения констант поправки, блок 4 хранения констант для вычисления ран- г, накапливающий сумматор 5 перево- дЬ, накапливающий сумматор 6 поправки, накапливающий сумматор 7 ранга, 8 хранения констант ранга, схему 9 сравнения с константой, первый и|второй блоки 10 и.11 элементов ИЛИ б|1ок 12 элементов И, с первого по чет в(гртый тактовые входы 13-16 преобра- зЬвателя, информационный выход 17 пре оЬразователя, выход 18 правильности перевода преобразователя, вход 19 на- чальной установки преобразователя

Преобразователь реализует последо В1ательный принцип работы. I Цикл преобразования занимает (п+2) тактов, где п - число инфор- йационных оснований в реализуемой м |eли модулярной арифметики, для ко- :(орой константы следует вычислить lio формулам:

константы для вычисления ранга

(d/m./d, + -.-)/Р()/Р,

константы для вычисления поправки

.()/p,

константы ранга -V P/Mk-(P-l)/2Mk,

d(- - (P-) константы перевода

P/m,/o(.-b(PrO/2) / Р, /MkP.,

i 1-n,

где - остатки исходного числа;

P. - основания системы (Р нечетные) ;

0 5 0 5

0

5

0

5

0

5

п - число оснований; Р - диапазон системы; k - масштабный коэффициент; М - общий знаменатель дроби, представляющий числа (для целых чисел М ); Vf - ранг числа; Х - целая часть; Х - дробная часть;

,d - точностные параметры.

Предполагается, что сумматоры и константы должны использовать систему счисления, в которую осуществляется перевод

Преобразователь работает следующим образом.

В начале цикла по сигналу с входа 19 происходит обнуление сумматоров 5 - 7. .

В каждом из п тактов на информационный вход 1 устройства поступает очередной остаток с соответствующим номером основания. Этот код образует адрес (jlog.n. 1 ) для блоков 2-4 хранения констант перевода, констант поправки констант для вычисления ранга (1„,,, - максимально

ff &nCвозможный размер остатка числа для всех оснований). В момент времени t по сигналу с входа 13 константа перевода из блока 2 разрядности m через блок 10 элементов. ИЛИ считывается в накапливающий сумматор 5 перевода, константа поправки из блока 3 разрядности d Jlop,п + 1 t через блок 1 элементов.ИЛИ считывается- в накапливающий сумматор 6 поправки, константа для вычисления ранга из блока 4 разрядности d 2 считывается в накапливающий сумматор 7 ранга. Разрядность сумматоров должна быть достаточной для получения соответствующего результата. Для сумматора 5 она определяется количеством цифр в представлении числа с учетом знака, для сумматора 6 - не менее 2 d бит, для сумматора 7 - не менее 3/2 d бит. В момент времени t после установления переходных процессов по сигналу с входа 14 в сумматорах фиксируется полученная сумма. Через п тактов в сумматорах перевода 5 и поправки 6 накоплены суммы соответствующих констант по всем основаниям, а в сумматоре 7 получено значение ранга. Значение ранга, образуемое старшими d/2 разрядами сумматора 7, .

является адресом блока 8 хранения констант ранга, следующие d/2 разрядов сумматора 7 используются в схеме 9 сравнения с константой, которая может быть реализована посредством элемента И-НЕ, младшие d/2 разрядов игнорируются., В п+ такте в момент времени t по сигналу с входа 15 из блока 8 хранения констант ранга коне такта разрядности m через блок 10

элементов ИЛИ считывается в суммато-

f-

ре 5 и константа разрядности d через блок 11 элементов ИЛИ считывается в сумматоре 6 поправки, а сигнал со схемы 9 сравнения с константой выдается на выход 18 устройства,

В момент времени t после установления переходных процессов по сигналу с входа 14 в сумматорах 5 и 6 фик сируется новая сумма. При этом в сумматоре 6 получено значение поправки (старшие d разрядов),

В п+2 такте в момент времени t на вход блока 12 элементов И посту- пает сигнал с входа 16 и разрешает прохождение поправки через блок IО элементов ИЛИ в сумматор 5 для коррекции накопленной суммы, младшие d выходов сумматора 6 игнорируются. По окончании переходных процессов Б момент времени t по сигналу с входа 14 в сумматоре 5 фиксируется окончательный результат преобразования, который снимается с выхода 17,

Формулаиз обретения

Преобразователь модулярного кода .в позиционный код, содержащий блок хранения констант перевода,блок хранения констант поправки, накапливаю- 1ЦИЙ сумматор перевода, накапливающий сумматор поправки и блок элементов И, причем информационный вход преобразователя соединен с адресным входом блока хранения констант поправки, вход разрешения чтения которого соединен с первым тактовым входом преобразователя вход начальной установки которого соединен с входами сброса накапливающего сумматора перевода и накапливающего сумматора поправки, выход которого соединен с первым входом блока элементов И, второй тактовый вход преобразователя соединен с тактовым входом накапливающего

д

5

0

5 0

5

0

5

0

5

cyNiMtTTOpa перевода, выход которого является информационным выходом преобразователя, отличающийся тем. что, с целью сокращения аппаратурных затрат, он содержит блок хранения констант для вычисления ранга, накапливающий сумматор ранга блок хранения констант ранга, схему сравнения с константой, первый и второй блоки элементов ШШ, причем информационный вход преобразователя соединен с адресными входами блока хранения констант поправки и блока хранения констант для вычисления ранга, выход которого соединен с информационным входом накапливающего сумматора ранга, выходы групп разрядов которого соединены соответственно с адресным входом блока хранения констант ранга и с информационным входом схемы сравнения с константой, выход которой является выходом правильности перевода преобразовата-пя, выход блока хра- . нения констант перевода соединен с первым входом первого блока элементов ИЛИ, выход которого соединен с информационным входом накапливающего сумматора перевода, выход блока хранения констант поправки соединен с первым входом второго блока элементов ИЛИ, выход которого соединен с информационным входом накапливающего сумматора поправки, выход блока хранения констант ранга соединен с вторыми входами первого и второго блоков элементов ИЛИ, выход блока элемен-и тоБ И соединен с третьим., входом первого блока элементов ИЛИ, первый тактовый вход преобразователя соединен с входами разрешения чтения блока хранения констант поправки и блока хранения констант для вычисления ранга, второй тактовый вход преобразователя соединен с тактовыми входами накапливающего сумматора поправки и накапливающего сумматора ранга,. вход сброса которого соединен с вко дом начальной установки преобразователя, третий тактовый вход которого соединен с входом разрешения чтения блока хранения констант ранга и с . входом разрешения схемы сравнения с константой, четвертый тактовый вход преобразователя соединен с вторым входом блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования интегральных характеристик модулярного кода | 1984 |

|

SU1216777A1 |

| Устройство для масштабирования чисел в модулярной арифметике | 1988 |

|

SU1541605A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для формирования позиционного признака в модулярной арифметике | 1988 |

|

SU1532924A1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Преобразователь модулярного кода в двоичный код | 1984 |

|

SU1238244A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

Изобретение относится к вычислительным средствам, работающим в модулярной арифметике, и позволяет совместить преобразование модулярного кода в позиционный код с масштабированием и повысить точность перевода путем вычисления поправки и добавления ее к переведенному числу при несущественных аппаратурных затратах. Преобразователь содержит блок 2 хранения констант перевода, блок 3 хранения констант поправки, блок 4 хранения констант для вычисления ранга, накапливающий сумматор 5 перевода, накапливающий сумматор 6 поправки, накапливающий сумматор 7 ранга, блок 8 хранения констант ранга, схему 9 сравнения с константой, блоки 10 и 11 элементов ИЛИ и блок 12 элементов И с соответствующими связями. 1 ил.

| ПРЕОБРАЗОВАТЕЛЬ КОДА ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЛИАДИЧЕСКИЙ КОД | 0 |

|

SU328448A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-08-23—Публикация

1988-05-04—Подача