112

Изобретение относится к вычислительной технике и ориентировано на использование в быстродействующих специализированных системах. ци.фровой обработки сигналов для вычисления различных элементарных функций (тригонометрических, логарифмических, экспоненциального вида и др,) от аргументов, изменяющихся в (-щтервале -1,l и представленных в модулярной системе счисления.

Целью изобретения является повышение быстродействия.

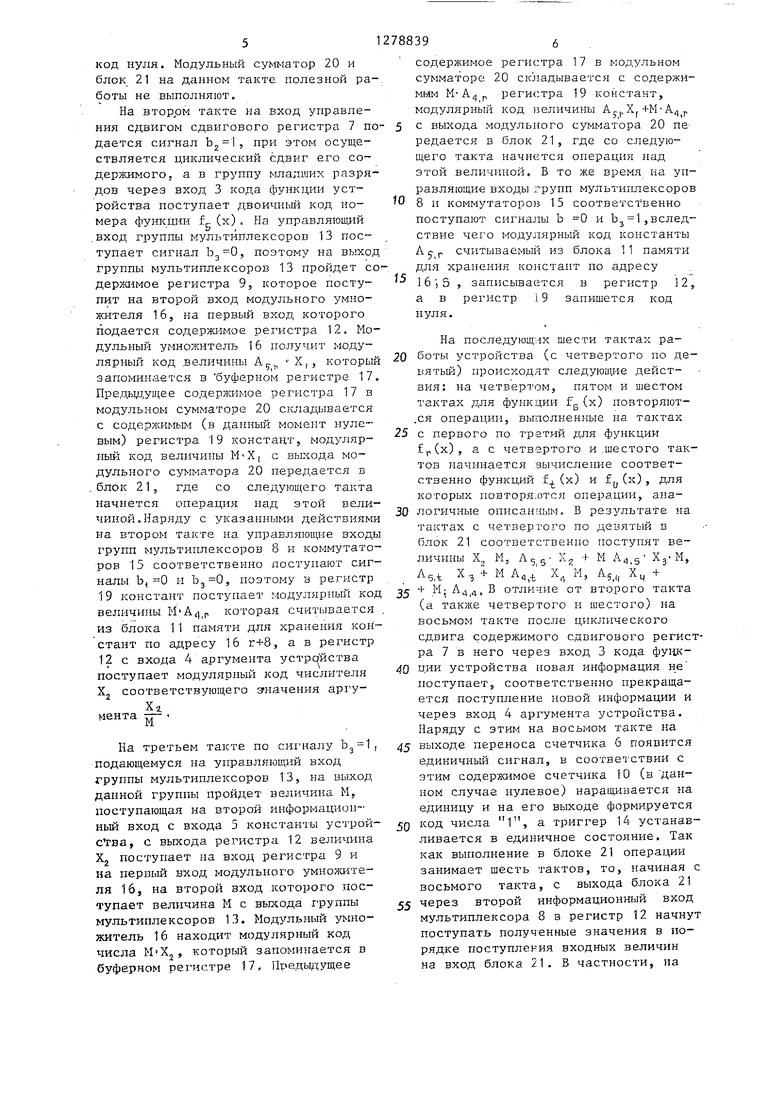

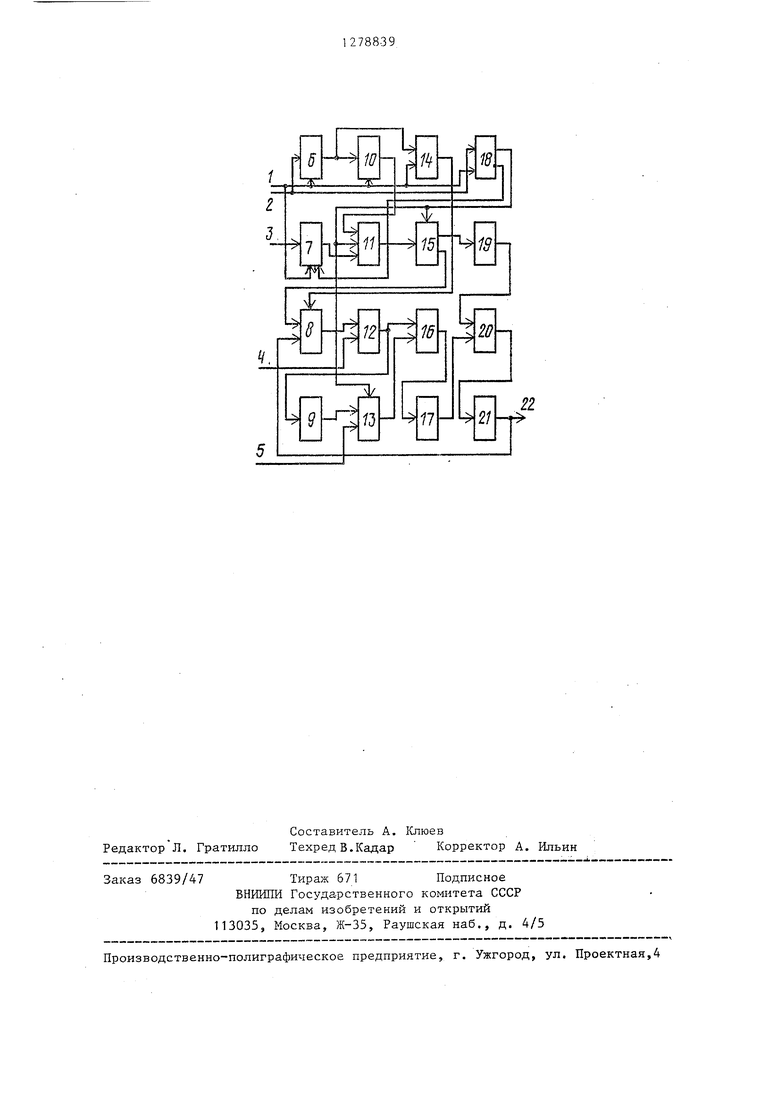

На чертеже представлена схема устройства для вычисления функций в модуля р I ом коде.

Устройство для вычисления функций в модулярном коде содержит установочный вход, 1 устройства, тактовый вход 2 устройства, вход 3 кодгг функции устройства5 вход, 4 аргумента устройства, вхо,а; 5 константы устройства, счетчик б по модулю, сдвиговый

регистр 7, первую группу мультиплексоров 8, первый вспомогательный регистр 9, счетчик 10, блок 11 памяти для хранения констант, второй -вспомог ательный регистр 12, вторую I pyniiy мультиплексоров 13, первый триггер 14, группу коммутаторов 15, модульный умногкитель 16, буферный регистр 17, второй триггер 18, регистр 19 констант, модульный сумматор 20, блок 21 делания на константу и выход 22 устройства.

Разрядность сдвигового регистра 7 составляет . бит, г,це N - число , вычисляемых устройством., через х обозначается наименьшее целое число, не меньшее X. Регистр 7 выполняет циклический сдвиг содержимого на бит.

Счетчик б работает по модулю восемь. Счетчик 10 имеет три разряда.

Блок 11 памяти для хранения кон -rH+lEoqoN L

стант обладает емкостью 2. -

слоев разрядностью

I log.

m;

би ,

01., т,,,.., ,т - основа п-1я модулярной системы счисления, k - число оснований, причем ш,; 2p-i-k-2 (р - фиксированное натуральное число), ikieB.

Модулярные коды, констант, относящихся к п-ой из вг51числяемых устройством функций (,1,. ., sN-lJ ) записываются в ячейке блока 11 памяти по адресу 2o+8E,+16n, где информация на выходе счетчика 10j t. - информация на выходе-триггера 18,

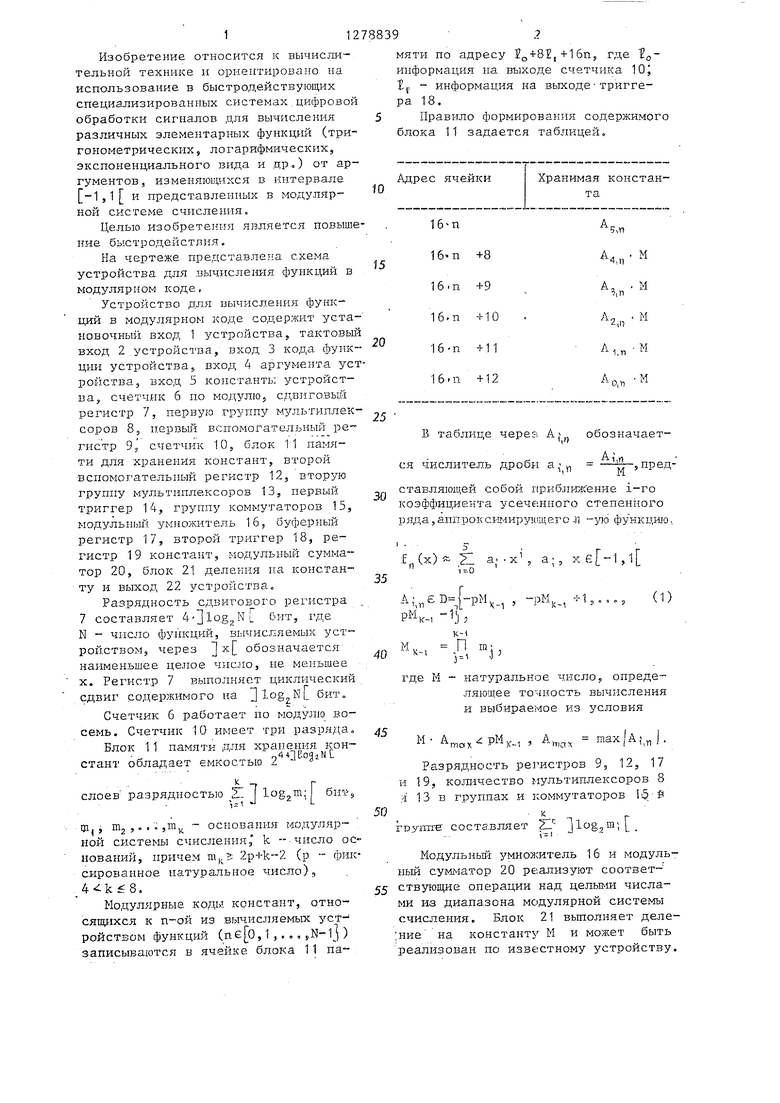

Правило формирования содержимого блока 11 задается таблицей.

30

ставляющей собой приблилсение i-го коэффициента усеченного степенного ряда аппрокси-шр пощего л функцию.

f,(x)

z:

а X

X

Q

D--

-рм,,, -м,

(1)

рМкч ,

K-i М-К-, Д in,j;

где М - натуральное число,, определяющее To iHocTb вычисления и выбирае уюе из условия

М А

тох

рМ

К-1

А

max

|А;

,П

50

Разрядность регистров 9, 12, 17 19, кол1-1чество мультиплексоров 8 13 в группах и коммутаторов 1i5 е

.

гоупи-е составляет 21 jlogj

m

Модульный з множитель 16 и модульный сумматор 20 реализуют соответ- 55 ствующие операции над целыми числа- ьш на диапа.зона модулярной системы счисления. Блок 21 вьшолняет деле- ;ние на константу М и может быть реализован по известному устройству.

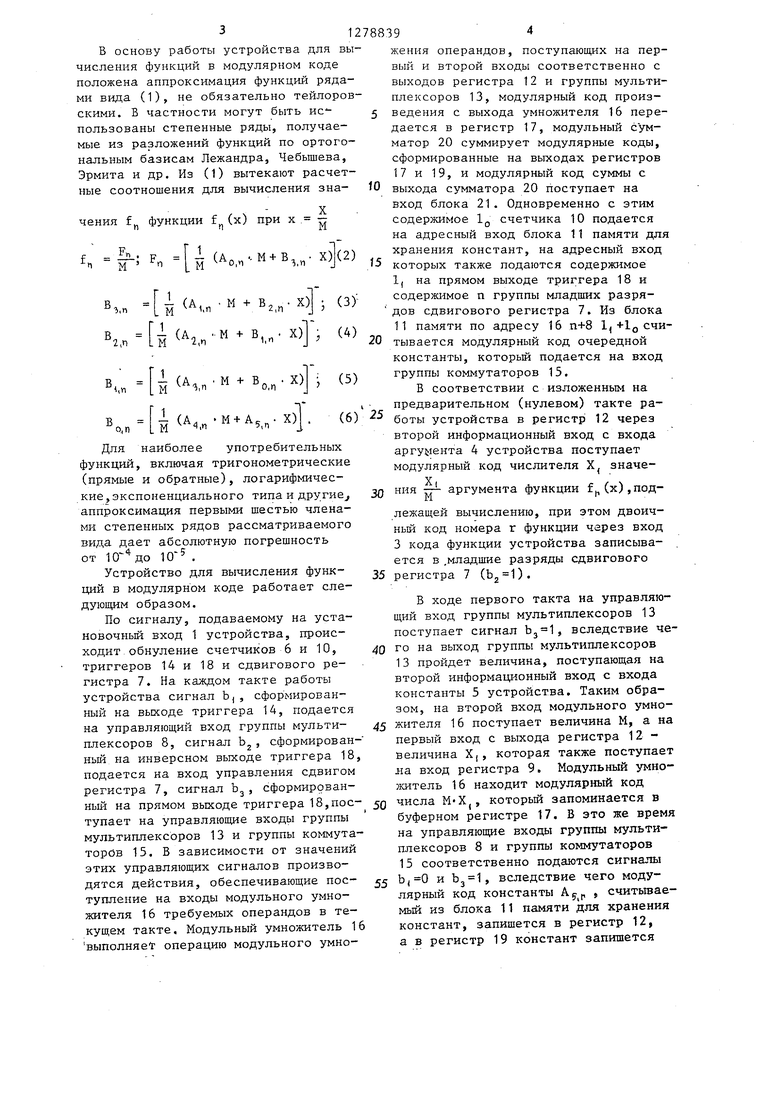

В осыову работы устройства для вчисления функций в модулярном коде положена аппроксимация функций рядами вида (1), не обязательно тейлороскими. В частности могут быть ис- пользованы степенные ряды, получаемые из разложений функций по ортогональным базисам Лежандра, Чабышева, Эрмита и др. Из (1) вытекают расчетные соотношения для вычисления зна-

чения f функции

fjx)

X при X - -п - Т7-

Zu м

РП

(А

Ъ:П

2.П

М+В,„. X)J(2)

1 А,,п М + В.,- X) (ЗУ X), (4)

(А

М + В

,п

о.,п ля

(А

il

i.i

4,п

М +

Во,п-

(5)

М+А

5,п

X,-.

наиболее употребительных

(6) 25

функций, включая тригонометрические (прямые и обратные), логарифмические ,экспоненциального типа и дpyгиeJ аппроксимация первыми шестью членами степенных рядов рассматриваемого вида дает абсолютную погрешность от 10 до 10 .

Устройство для вычисления функций в модулярном коде работает следующим образом.

По сигналу, подаваемому на уста- новочньй вход 1 устройства, происходит . обнуление счетчиков 6 и 10, триггеров 14 и 18 и сдвигового регистра 7. На каждом такте работы устройства сигнал Ь,, сформированный на вьпсоде триггера 14, подается на управляющий вход группы мультиплексоров 8, сигнал bj , сформированньш на инверсном выходе триггера 18, подается на вход управления сдвигом регистра 7, сигнал Ъ, сформированный на прямом выходе триггера 18,поступает на управляющие входы группы мультиплексоров 13 и группы коммутаторов 15. В зависимости от значений этих управляющих сигналов производятся действия, обеспечивающие поступление на входы модульного умножителя 16 требуемых операндов в те- куш,ем такте. Модульный умножитель 16 выполняет операцию модульного умно0

5

0

5

0

5

жения операндов, поступающих на первый и второй входы соответственно с выходов регистра 12 и группы мультиплексоров 13, модулярный код произведения с выхода умножителя 16 передается в регистр 17, модульный сумматор 20 суммирует модулярные коды, сформированные на выходах регистров 17 и 19, и модулярный код суммы с выхода сумматора 20 поступает на вход блока 21. Одновременно с этим содержимое l счетчика 10 подается на адресный вход блока 11 памяти для хранения констант, на адресный вход которых также подаются содержимое 1, на прямом выходе триггера 18 и содержимое п группы младших разрядов сдвигового регистра 7. Из блока 11 памяти по адресу 16 п+8 1,+1о считывается модулярный код очередной константы, который подается на вход группы коммутаторов 15.

В соответствии с изложенным на предварительном (нулевом) такте работы устройства в регистр 12 через второй информационный вход с входа аргумента 4 устройства поступает модулярный код числителя Х значеу

ния гр аргумента функции f(x),подлежащей вычислению, при этом двоичный код номера г функции через вход 3 кода функции устройства записывается в .младшие разряды сдвигового регистра

7 (Ь,,1).

В ходе первого такта на управляющий вход группы мультиплексоров 13 поступает сигнал , вследствие чего на выход группы мультиплексоров 13 пройдет величина, поступающая на второй информационный вход с входа константы 5 устройства. Таким образом, на второй вход модульного умножителя 16 поступает величина М, а на первый вход с выхода регистра 12 - величина Х,, которая также поступает ла вход регистра 9. Модульный умно- 5китель 16 находит модуляр1шй код

числа М Х|, который запоминается в

буферном регистре 17. В это же время на управляющие входы группы мультиплексоров 8 и группы коммутаторов 15 соответственно подаются сигналы Ь(0 и , вследствие чего модулярный код константы Aj-p считываемый из блока 11 памяти для хранения констант, запишется в регистр 12, а в регистр 19 констант запишется

код нуля. Модульный сумматор 20 и блок 21 на данном такте полезной работы не выполняют„

На вторрм такте на вход управления сдвигом сдвигового регистра 7 подается сигнал , при этом осуществляется циклический сдвиг его содержимого, а в группу младших разрядов через вход 3 кода функции устройства поступает двоичный код номера функции f (х) На управляющий .вход группы мультиплексоров 13 поступает сигнал b,, поэтому на выход группы мультиплексоров 13 пройдет со дерлшмое регистра 9, которое поступит на второй вход модульного умножителя 16, на первый вход которого подается содерж1-1мое регистра 12, Модульный умножитель 16 получит модулярный код .величины А.,, Х,, который запоминается в буферном регистре 17. Предьщущее содерзкимое регистра 17 в модульном сумматоре 20 складывается с содержимым (в данный момент нулевым) регистра 19 констант, модулярный код величины М Х| с выхода модульного сумматора 20 передается в блок 21, где со следующего такта начнется операция над этой величиной. Наряду с указанными действиями на втором такте на управляющие входы групп мультиплексоров 8 и коммутаторов 15 соответственно поступают сигналы Ь, 0 и , поэтому в регистр 19 констант поступает модулярный код величины М А,|,р которая считывается из блока 11 памяти для хранения кон- стант по адресу 16 г+8, а в регистр 12 с входа 4 аргумента устрс йства поступает модулярный код числителя Xj соответствующего значения арг У

иента

Xj М

На третьем такте по сиг налу подающемуся на управляющий вход группы мультиплексоров 13, на выход дайной группы пройдет величина М поступающая на второй информацион- ньй вход с входа 5 константы устройства, с выхода регистра 12 величина Xj поступает на вход регистра 9 и на первый вход модульного умноисите- ля 16, на второй вход которого поступает величина М с вькода группы мультиплексоров 13. Модульный умножитель 16 находит модулярный код числа M Xj, который запоминается в буферном регистре 17. Предыдущее

содержимое регистра 17 в модульном сумматоре 20 складывается с содержимым регистра 19 констант, модулярный код величины А.Х -i-M А

с выхода модульного сумматора 20 не редается в блок 21, где со следующего такта начнется операция над этой величиной. В то же время на управляющие входы групп мультиплексоров

8 и коммутаторо)з 15 соответственно поступают сигналы b 0 и Ь2 15вслед- ствие чего модулярный код константы считываемый из блока 11 памяти для хранения констант но адресу

16, 5 , записывается в регистр 12, а в регистр 19 запишется код нуля.

На последующих шести тактах ра-

боты устройства (с четвертого по .девятый) происходят следующие действия: на четвертом, пятом и шестом тактах для функции fg(х) повторяют- .ся операции, выполненные на тактах

с первого по третий для функции

fp(x), а с четвертого и .шестого тактов начинается вычисление соответственно функций f (х) и f JJ (х) , для которых повторя.отся операции, аналогичные описан 1ым, В результате на тактах с четвертого по девятый в блок 21 соответственно поступят величины X., М, Х + М ,g Xj M, Аел Х, - М A.t Х М, Aj,,, Х +

I М; -.4,4. отличие от вто.рого такта (а таклсе четвертого и шестого) на восьмом такте после циклического сдвига содержимого сдвигового регистра 7 в него через вход 3 кода функЦии устройства новая информация не поступает, соответственно прекращается поступление новой информации и через вход 4 аргумента устройства. Наряду с этим на восьмом такте на

выходе переноса счетчика. 6 появится единичный сигнал, в соответствии с этим содерхшмое счетчика 10 (в данном случае нулевое) наращивается на единицу и на его выходе форми.руется

код числа 1, а триггер 14 устанавливается в единичное состояние. Так как выполнение в блоке 21 операции занимает шесть тактов, то, начиная с восьмого такта, с выхода блока 21

через второй информационный вход мультиплексора 8 в регистр 12 начнут поступать полученные значения в порядке поступления входных величин на вход блока 21. В частности, на

восьмом такте в регистр 12 поступит модулярный код велич йны X,.

На девятом такте по сигналу , подающемуся на селекторный вход группы мультиплексоров 13, на выход пройдет величина М, поступающая на второй информационный вход с входа 5 константы устройства, с выхода ре- истра 12 величина Х( передается в Iрегистр 9 и на первый вход модульноiго умножителя 16, на второй вход которого с выхода группы мультиплек- соров 13 поступает величина М, Модульный умножитель 16 находит мо- дулярный код числа М-Х, который запоминается в буферном регистре 17. Одновременно с этим на селекторные входы групп мультиплексоров 8 и коммутаторов 15 поступают сигналы и , вследствие чего в регистр 19 констант запишется код нуля, а в регистр 12 - модулярный код величины BOH , поступающий с выхода

блока 21 (6), I

На десятом такте на вход управления сдвигом сдвигового регистра 7 подается сигнал , при этом осуществляется циклический сдвиг его содержимого и на выходе младших разрядов сдвигового регистра 7 появится двоичный код номера S функции. На управляющий вход группы мультиплексоров 13 поступает сигнал Ь 05поэтому содержимое регистра 9, поступающее на второй инфopмaп, вход пройдет на второй вход модульного умножителя 16, на первый вход которого поступает с выхода регистра 12 величина BQ . Модульный умножитель 16 получит модулярный код величины Вдр X,, который запоминается в буферном регистре 17. Предыдущее содержимое регистра 17 в модульном сумматоре 20 складывается с содержимым регистра 19 констант, модулярный код величины М-Х( с выхода модульного сумматора 20 подается в блок 21. Наряду с указанными действиями на десятом такте на селекторные входы групп мультиплексоров 8 и коммутаторов 15 соответственно поступают сигналы Ь, 1 и , поэтому в регистр 19 констант поступает модулярный код величины считываемый из блока 11 памяти для хранения констант по адресу 16 г+9 (таблица), а в регистр 12 с выхода блока 21 поступает модулярный код величины Х.

На одиннадцатом такте по сигналу , подающемуся на управляющий вход группы мультиплексоров 13, на выход данной группы пройдет величина М,

поступающая на второй информационный вход с входа 5 константы устройства, содержимое регистра 12 поступает на вход регистра 9 и на первый вход модульного умножителя 16, па второй вход которого с выхода группы мультиплексоров 13 поступает величина М. Модульный умножитель 16 находит модулярный код числа M Xj ,, который запоминается в буферном регистре 17.

Предыдущее содержимое регистра 17 в модульном сумматоре 20 складывается с содержим151М ре.гистра 19 констант, модулярный код величины М А,,,+ЗррХ, с выхода модульного сумматора 20 пе- редается в блок 21. Наряду с этим на управляющие входы групп мультиплексоров 8 и коммутаторов 15 соответственно поступают сигналы Ь, 1 и b.j 1, вследствие чего в регистр 19 запишется код нуля, а модулярный код константы с выхода блока 21 поступит в регистр 12.

На последующих шести тактах работы устройства (с двенадцатого по семнадцатый) происходят следующие действия: на двенадцатом и тринадцатом тактах для функции fg ,(х) повторяются операции, выполненный на тактах десятом и одиннадцатом для функции . f,, (х), а с двенадцатого и четырнадцатого тактов для фу 1кций f-j.(x) и fу(х) повторяются операции, аналогичные операциям, выполняемым с восьмого такта для функции f„(х) (3).

На последующих тактах с шестнадцатого по двадцать третий (5), с двадцать четвертого по тридцать первый (4), с тридцать второго по тридцать девятый (3) и с сорокового по сорок седьмой (2) для функции выпол- няются действия, аналогичные действиям, реализуемым на тактах с восьмого по пятнадцатый. При этом на сорок первом, сорок третьем, сорок пятом и сорок седьмом тактах блок 21 завершает формирование величи f , fg , f, fy (2) соответственно. Модулярные коды искомых величин в yica- занных тактах снимаются с выхода 22 устройства и на этом процесс вычисления функций в заданных точках заканчивается,

Начиная с сорокового такта, в предлагаемом устройстве может быть начато вычисление новых четырех значений одной и той же или четырех различных функций.

Формула изобретения

Устройство для вычисления функций в модулярном коде, содержащее сдвиговый регистр, блок памяти для хранения констант, регистр констант, модульный умножитель, модульный сумматор, группу коммутаторов 5 счетчик по модулю, два триггера, два вспомогательных регистра и буферный регистр, причем вход кода задания функции устройства соединен с входом младших разрядов сдвигового ре- . гистра, выход регистра констант соединен с входом первого слагаемого модульного сумматора, информационный вход первого вспомогательного регистра соединен с выходом второго вспомогательного регистра и с входоьз первого сомножителя модульного умножителя, установочный вход второго вспомогательного регистра соединен с входом аргумента устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит счетчик, две группы-мультиплексоров и блок деления на константу, причем установочный вход устройства подключен к входам обнуления сдвигового регистра, счетчика и счетчика по модулю, а также к входам сброса первого и второго триггеров, тактовый вход устройства подключен к счетному входу второго триггера и счетному входу счетчика по модулю, выход переноса которого соединен со счетным входом счетчика и

входом установки первого триггера, разрядный выход счетчика, прямой В14ХОД второго триггера и выходы младших разрядов сдвигового регистра

соединены соответственно с разрядами адресного входа блока памяти для хранения констант, выход которого соединен с информационными входами коммутаторов группы, первые и вторые выходы которых соединены соответственно с информационным входом регистра констант и с первыми информационными входами мультиплексоров первой группы, выходы которых соединень с соответствующими разрядами информационного входа второго вспомогательного регистра, выход первого триггера соединеп с управляющими, входами мультиплексоров первой группы, вторые -информационные входы которых соединены с выходом блока деления на константу, выход которого является выходом устройства, прямой выход второго триггера соединен с управляюпшмк входами коммутаторов группы и с управляющими 1зходами мультиплексоров второй группы, инверсный выход второго триггера соединен с входом управления сдвигом сдвигового регистра, выход первого вспомогательного регистра, и вход константы устройства соединены соответственно с первыми и вторыми информационными входами мультиплексоров второй гру ппы, выходы которых соединены с соот- ветствуюпдами разрядами входа второго сомножителя модульного умножителя, выход которого соединен с входом буферного регистра,, выход которого

соединен с входом второго слагаемого модульного сумматора, выход которого соединен с входом блока деления на константу.

Редактор Л. Гратилло

Составитель А, Клюев

Техред В.Кадар Корректор А. Ильин

6839/47

Тираж 671 Подписное БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

| Устройство для вычисления элементарных функций в модулярной системе счисления | 1985 |

|

SU1291977A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

Изобретение относится к вычисг- лительной технике и ориентировано на использование в быстродействуюгцих специализированных системах цифровой обработки сигналов для вычисления различных элементарных функций (тригонометрических, логарифмических, экспоненциального вида и других) от аргументов, представленных в модулярной системе счисления.Цель изобретения состоит в повышении быстродействия. Поставленная цель достигается тем, что устройство, содержащее сдвиговый регистр, блок памяти для хранения констант, регистр констант, модульный умножитель, модульный сумматор, группу коммутаторов, счетчик по модулю, два триггера и буферный регистр, содержит счетчик, две группы мультиплексоров и блок деления на константу с соответствующими связями. 1 ил. с (Q С

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-14—Подача