(46) 30.02.93. Бюл. /8 .

(21) 4361227/07

(22)11.01.(72) В.И.Котенев. Л.Я.Мзкаровский. А.В.Закутилин, А.А.Оськин и А.З.Яценко

(56)Авторское свидетельство СССР 1221706, кл. Н 02 Р 5/00. 1986.

Авторское свидетельство СССР № 1503486. кл. Н 02 Р 5/00. 1987.

(54) ЗАДАЮЩЕЕ УСТРОЙСТВО

(57)Изобретение относится к электротехнике и может найти применение а устройствах программного изменения создаваемых па раметров электроприводов, например скорости. Целью изобретения является

повышение точности задания программы при существенно отличающихся темпах нарастания и снижения выходного сигнала. Устройство содержит интеграторы 2. 15. 19. задатчик 1 начального напряжения, задат- чик 16 времени цикла, задатчик 5 начала замедления, задатчики 9 и 10 максимального и минимального уровней выходного сигнала, задатчики 13 и 14 темпа нарастания и снижения, блоки 12 и 18 умножения и ключи 7. 8. 20. 21. 22, 23. Формирование программ нарастания и снижения выходного сигнала осуществляется интеграторами 15 и 19 с различными и независимыми постоянными времени интегрирования, чем достигается поставленная цель. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство программного управления нагревом роторов турбоагрегатов при разгонно-циклических испытаниях | 1990 |

|

SU1763930A1 |

| Устройство программного управления индукционным нагревом | 1991 |

|

SU1784948A1 |

| Устройство для точного останова электропривода | 1985 |

|

SU1272447A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ИНТЕНСИВНОСТЬЮ ОХЛАЖДЕНИЯ ПРИ ТЕРМОЦИКЛИЧЕСКИХ ИСПЫТАНИЯХ ДИСКОВ ТУРБОМАШИН | 1989 |

|

SU1616299A2 |

| Устройство для управления процессом контактной точечной сварки | 1985 |

|

SU1281357A1 |

| Устройство программного управления нагревом роторов турбоагрегатов при разгонно-циклических испытаниях | 1987 |

|

SU1502974A2 |

| Устройство для задания скорости электропривода | 1986 |

|

SU1419465A2 |

| Способ автоматического контроля и регулирования процесса контактной сварки и устройство для его осуществления | 1987 |

|

SU1423320A1 |

| Система позиционирования с двухзонным регулированием скорости электропривода | 1991 |

|

SU1798765A1 |

| Система автоматического регулирования | 1987 |

|

SU1483429A1 |

Изобретение относится к электротехнике и может найти применение в устройствах программного измене(ия задаваемых параметров электроприводов, например скорости.

Целью изобретения является повышение точности задания программы при существенно отличающихся темпах нарастания и снижения выходного сигнала.

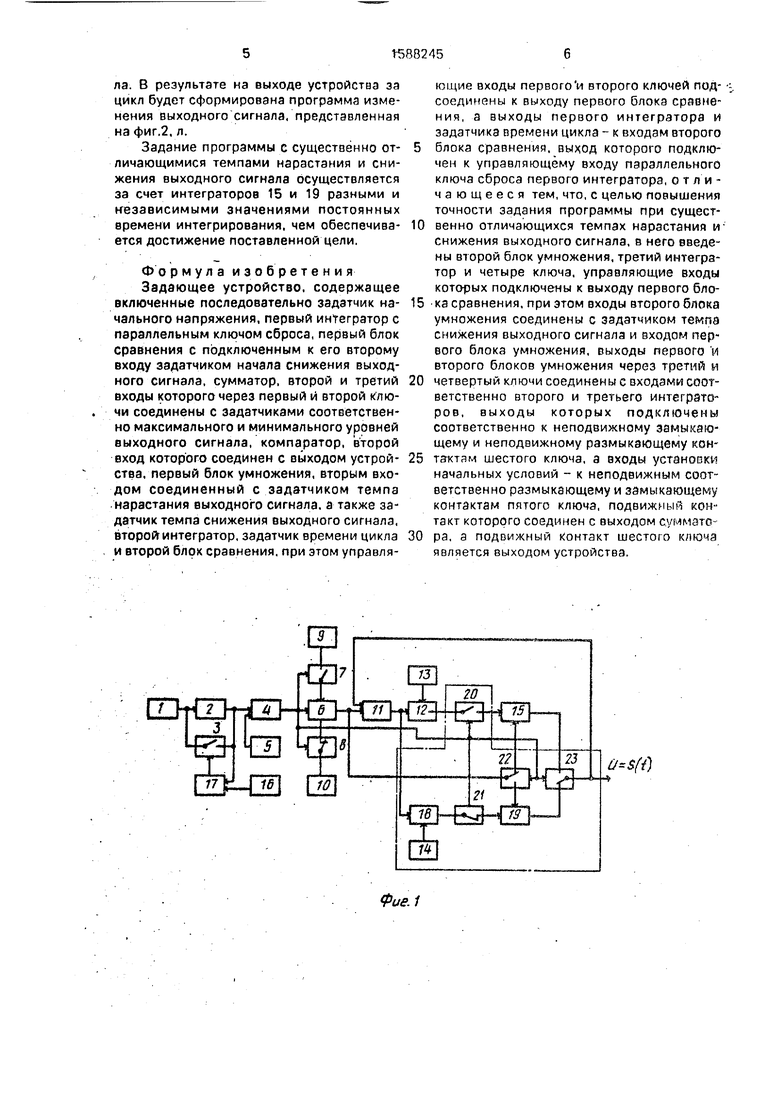

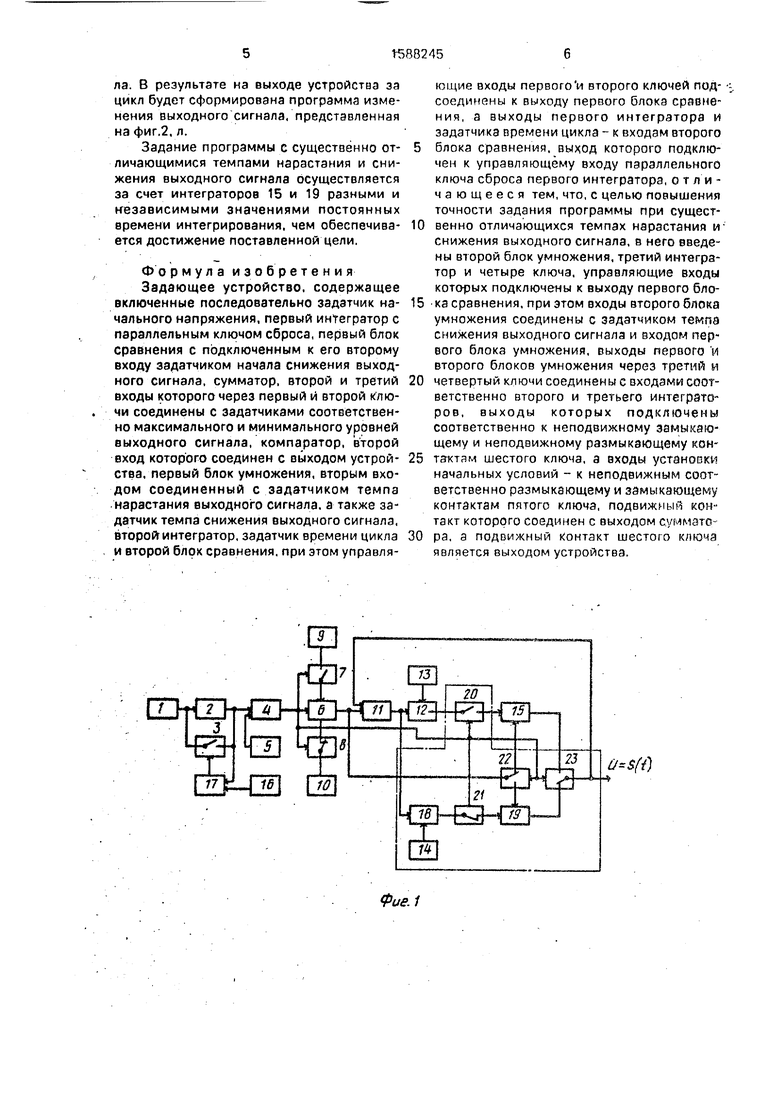

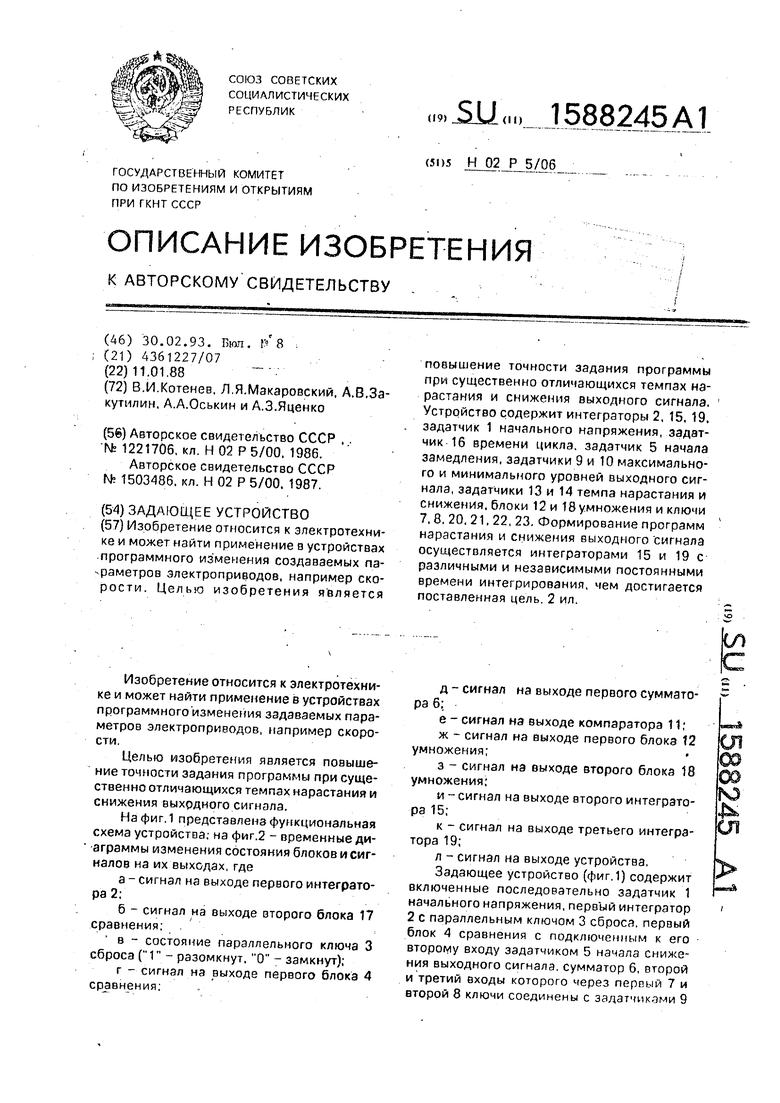

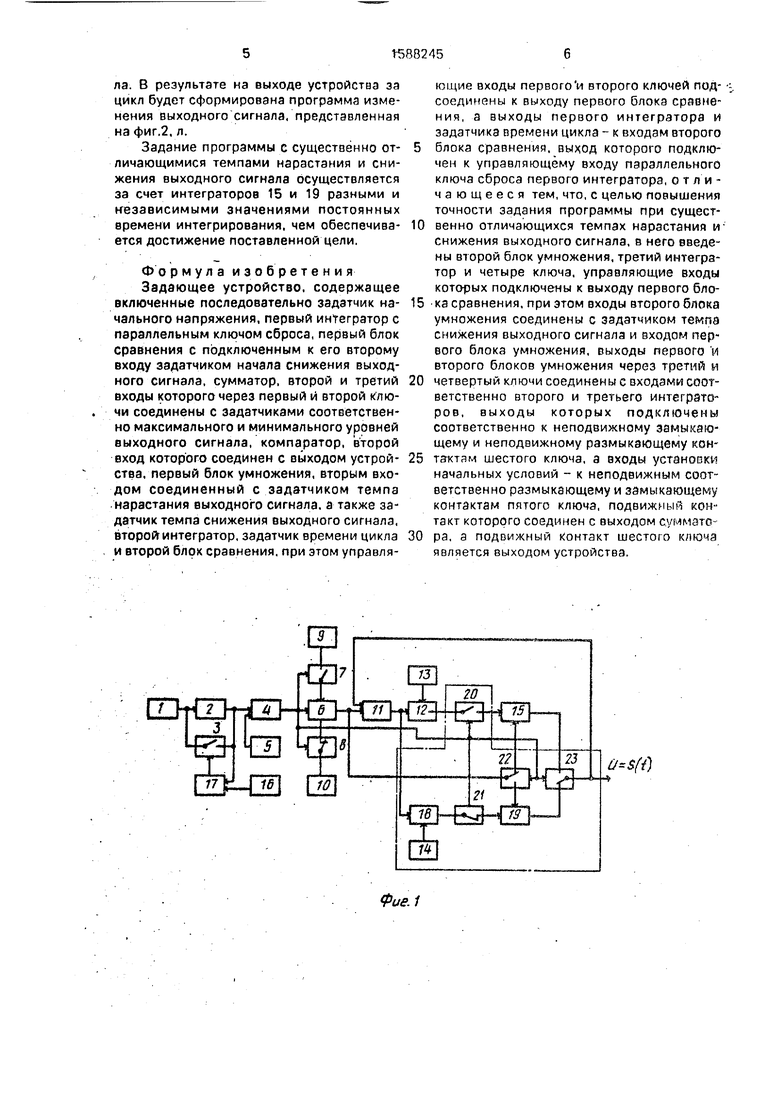

На фиг. 1 представлена функциональная схема устройства. на фиг.2 - временные ди- аграммы изменения состояния блоков и сигналов на их выходах, где

а - сигнал на выходе первого интегратоРЗ &4

б - сигнал на выходе второго блока 17 сравнения: .

в состояние параллельного ключа 3 сброса (1 - разомкнут. О - замкнут):

г - сигнал на выходе первого блока 4 сравнения:.

д - сигнал на выходе первого сумматора 6;

е - сигнал на выходе компаратора 11,- ж - сигнал на выходе первого блока 12 умножения:

3 - сигнал на выходе второго блока 18 умножения:

и сигнал на выходе второго интегратора 15:

к - сигнал на выходе третьего интегратора 19:

л - сигнал на выходе устройства.

Задающее устройство (фиг.1) содержит включенные последовательно задатчик 1 начального напряжения, первь1й интегратор 2 с параллельным ключом 3 сброса, первый блок 4 сравнения с подключенным к его второму входу задатчиком 5 начала снижения выходного сигнала, сумматор 6, второй и третий входы которого через первый 7 и второй 8 ключи соединены с задатчиками 9

ю

и 10 соответственно максимального и минимального уровней пыходного сигнала, компаратор 11, второй вход которого соединен с выходом устройства, первый блок; 12 умножения, вторым входом соединенный с за- датчиком 13 темпа нарастания выходного сигнала, а также задатчик 14 темпа снижения выходного сигнала, второй интегратор 15, задатчик 16 времени цикла и второй блок

17сравнения, Управляющие входы первого 7 и второго 8 ключей подсоединены к выходу первого блока 4 сравнения, а выходы первого интегратора 2 и задатчика 16 времени цикла - к входам второго блока 17 сравнения, выход которого подключен к управляющему входу параллельного ключа сброса первого интегратора 2,

Устройство содержит также вторЬй блок

18умножения, третий интегратор 19 и ключи 20-23, управляющие входы которых подключены к выходу первого блока 4 сравнения. Входы второго блока 18умноже- 1ия соединены с задатчиком 14 темпа снижения выходного сигнала и входом первого блока 12 умножения. Выходы первого 12 и второго 18 блоков умножения через третий 20 и четЕ ертый 21 клЬчи соединены с входа-ми соответственно второго 15 и третьего 19 интеграторов, выходы которых подключены соответственно к неподвижному замыкающему и неподвижному размыкающему контактам шестого ключа 23, а входы установки начальных условий - к неподвижным собт- ветственно размыкающему и замыкающему контактам пятого ключа 22. подвижный контакт которого соединен,с выходом сумматора 6. Подвижный контакт шестого ключа 23 является выходом устройства.

Устройство работает следующим образом.

Время полного цикла изменения выходного сигнала устройства задается с помощью напряжения задатчика 16. Скорость нарастания напряжения на выходе первого интегратора 2 устанавливается напряжением задатчика 1. Напряжение на выходе первого интегратора 2 нарастает по линейному закону (фиг,2.а), Момент времени ti. при котором начинается снижение выходного сигнала устройства, устанавливается задатчиком 5. Максимальный и минимальный уровни выходного сигнала устройства регулируются задатчиками соответственно 9 и 10. а темпы нарастания и снижения - задатчиками 13 и 14.

Для формирования времени цикла ц выходное напряжение первого интегратора 2 сравнивается с напряжением задатчика 16 во втором блоке 17 сравнения. В момент равенства этих напряжений на выходе блока 17 появляется импульс напряжения (фиг,2,б). Ключ 3 замыкается (фиг,2,в), что приводит к интенсивному снижению напряжения на выходе первого интегратора 2 (фиг,2,а). При достижении этим напряжени- ем нулевого значения вновь срабатывает второй блок 17 сравнения (фиг.2,б), ключ 3 размыкается (фиг,2,в) и цикл повторяется.

При равенстве напряжений первого ин- тегратора 2 и задатчика 5 (момент времени ti на фиг.2,а) на выходе первого блока 4 сравнения устанавливается нулевое значение сигнала (фиг.2.г), а в момент 1ц - максимальное. На интервале времени ti - О, когда 5 напряжение на выходе-блока 4 сравнения максимально, срабатывает первый ключ 7 и на выходе сумматора 6 устанавливается сигнал задатчика 9 максимального уровня (фиг.2,д). Соответственно на интервале 1ц - 0 ti, когда сигнал на выходе блока 4 сравнения равен нулю, с помощь ю ключа 8 на выходе сумматора б устанавливается сигнал задатчика 10 минимального уровня.

С появлением на выходе сумматора 6 5 максимального уровня сигнала на интервале ti - О на выходе компаратора 11 также устанавливается максимальный уровень сигнала (фиг.2,е). который, будучи умноженным на сигнал задатчика 13 в первом 0 блоке 12 умножения, поступает через замкнутый в это время третий ключ 20 на вход второго интегратора 15. Напряжение на выходе интегратора 15 начинает нарастать по линейному закону (фиг,2.и) и через шестой 5 ключ 23 поступает на второй вход компаратора 11, В момент равенства напряжений на входах компаратора 11 его выходной сигнал (фиг.2.е). а также сигнал на входе второго интегратора 15 становятся равными нулю, а 0 на выходе интегратора сохраняется достигнутый уровень сигнала (фиг.2,и).

В момент ti напряжение на выходе первого блока 4 сравнения становится равным нулю, переключаются ключи 7, 8, 20, 21, 22, 5 23 и начинается формирование программы снижения выходного сигнала устройства (фиг,2,к),Напряжение с выхода коммутатора (фиг,2.е) перемножйется с Напряжением задатчика 14 вторым блоком 18 умножения и 0 через замкнутый четвертый ключ 21 поступает на вход третьего интегратора 19. Напряжение на выходе интегратора 19 начинает снижаться по линейному закону и через ключ 12 поступает на второй вход 55 компаратора 11. Когда напряжения на входах компаратора 11 станут равными, сигнал на его выходе.и на входе третьего интегратора 19 будет равен нулю, а на выходе интегратора 19 будет сохраняться достигнутый уровень сигнала (фиг.2,к) до конца цикла. В результате на выходе устройства за цикл будет сформирована программа изменения выходного сигнала, представленная на фиг.2, л.

Задание программы с существенно от- пинающимися темпами нарастания и снижения выходного сигнала осуществляется за счет интеграторов 15 и 19 разными и независимыми значениями постоянных времени интегрирования, чем обеспечива- ется достижение поставленной цели.

Ф о рмула изобретения Задающее устройство, содержащее включенные последовательно задатчик на- чального напряжения, первый интегратор с параллельным ключом сброса, первый блок сравнения с подключенным к его второму входу задатчиком начала снижения выходного сигнала, сумматор, второй и третий входы которого через первый и второй ключи соединены с задатчиками соответственно максимального и минимального уровней выходного сигнала, компаратор, второй вход которого соединен с выходом устрой- ства. первый блок умножения, вторым входом соединенный с задатчиком темпа нарастания выходного сигнала, а также задатчик темпа снижения выходного сигнала, второй интегратор, задатчик времени цикла и второй блох сравнения, при этом управляющие входы первого и второго ключей подсоединены к выходу первого блока сравнения, а выходы первого интегратора и задатчика времени цикла - к входам второго блока сравнения, выход которого подключен к управляющему входу параллельного ключа сброса первого интегратора, отличающееся тем, что, с целью повышения точности задания программы при существенно отличающихся темпах нарастания и- снижения выходного сигнала, в него введены второй блок умножения, третий интегратор и четыре ключа, управляющие входы которых подключены к выходу первого блока сравнения, при этом входы второго блока умножения соединены с задатчиком темпа снижения выходного сигнала и входом первого блока умножения, выходы первого и второго блоков умножения через третий и четвертый ключи соединены с входами соответственно второго и третьего интеграторов, выходы которых подключены соответственно к неподвижному замыкающему и неподвижному размыкающему контактам шестого ключа, а входы установки начальных условий - к неподвижным соответственно размыкающему и замыкающему контактам пятого ключа, подвижмый контакт которого соединен с выходом сумматора, а подвижный контакт шестого ключа является выходом устройства.

Авторы

Даты

1993-02-28—Публикация

1988-01-11—Подача