Изобретение относится к цифровому моделированию биологических нейронов и предназначено для физиологических экспериментальных и теоретичес- Boix исследований при изучении целенаправленного поведения биологичес- lUix объектов и, в частности, самообучения. Кроме того, способ, может най- ти применение в системах управления.

предназначенных для работы в автономном режиме, без участия программиста и оператора.

Цель изобретения - повышение точности моделирования поведения реального нейрона путем регулирования порога генерации сигнала команды в зависимости от прогноза информационного значения входного сигнала.

При реализации способа « дeлиpoвa- ния, основанного на приеме многомерных входных сигналов,- нахождении, суммы координат поступившего сигна- ла и генерации сигнала команды,если эта сумма пpeiзыcилa з аданную величину порога, осуществляют регулирование, величины порога, заключающееся :в Том, что при приеме входного сиг- I нала устанавливают математические ожидания вероятностей прихода сигна- : ла награды при условии генерации сиг- : нала команды и в его отсутствии, и величина порога генерации сигнала команды в ответ на поступивший вход- ; ной сигнал уменьшается или увеличи- вается в засимости от знака равности : вычисленных математических ожиданий : и вероятности безошибочного прогноза этой разности, причем факт генерации сигнала команды и поступления награды запоминают, как следствие .входного .сигнала.

Благодаря этому обеспечивается воз можность безошибочного распознавания 2 сигналов по. запоминаемым следствиям, вызванных этими сигналами, и ухудшается эффективность целенаправленного поведения,, в частности,са- мообучения за счет учета свойства обратимого регулирования текушей эффективности генерации сигнала команда, что, в конечном счете, существенно повышает точность моделирования вследствие приближения к свойствам реального нeйpoнat

Способ осуществляется следующим образом. Пусть на вход модели поступил сигнал X(t) ((t), XgCt),... ...X.Ct)), где г - число входов модели, а t 0,2,1..; Xt(t)0 или 1 Сигнал Х. является наградой, напри- X (1,0,0...0). .Модель може

мер, -„ . , .V ,

генерщзовать сигнал команды Y i

или Y 0. Если X(t) Хо ранее поступал на вход модели и при первом появлении являлся j-ым He3HaKOh iM сигналом, то ему соответствуют nt, п , пЛ , чис.па случаев,

когда после сигнала X(t) генерировася сигнал команда и поступил синал награды Х 1, генерировался

сигнал команда Y. 1 и поступил сиг йап награды Х О и т.д.

Если X(t) безразличный сигнал, а V - порог для безразличного сигнала, то сигнал команды Y 1 генерируется , „. Если X(t) не

является безразличным сигналом, то порог генерации сигнала команды изменяют в зависимости от прогноза его информационного значения. Математические ожидания вероятностей привода сигнала награды при условиях генерации сигналов команды Y 1 или Y О рассчитывают по формулам

.1.„

JJ

2

м

D.lt-L

п + 2

Здесь учтено, что математические ожидания для незнакомого сигнала,который считается безразличным,принимаются равными 0,5. Вероятность безошибочного прогноза разности М,| - М оценивают по критерию Стьюдента.Критерий t| достоверности разности Мп - М оценивают по формуле

I Mt - Мг1

1 14 - I J i f

го

-st

-ошибка репрезентативности

-стандартное значение критерия СтьюДента.

Ошибка репрезентативности в данном случае зависит от числа степеней свободы сравниваемых выборок п + + „4-- + п + п -2 (т.е. от числа поступлений данного сигнала), но не зависит от разности М(-М. Поэтому в первом приближении можно считать, что порог генерации сигнала команды пропорционален .

Разность вычисленных математических, ожиданий изменяется в пределах от -1 до 1. Поэтому степень предпочтительности генерации сигнала команды Y 1 для получения награды Х 1 удобно выразить через

1+М« - Mi .

Условие генерацш сигнала команда Y 1 выводится из предположения,что истинное значение сигнала команды градуально и зависит от величины поступившего входного сигнала по типу S-образной функции, как это наблюдается в биологических нейронах:

.

Y 1 - е

Сигнал команды становится равным 1 при переходе через точку перегиба. Отсюда

Y

Г,если 2r(- 2-i-f : I, Vo

О иначе.

Команщ генерируют, если Х; Уд/42у. После прихода входного сигнала оценивают это условие ив зависимости от результатов оценки генерирует или не генерируют сигнал команды и принимают сигнал награды X, 1 или Х( .0. Эти результаты запоминают и модель нейрона готова к приему новых порций информации.

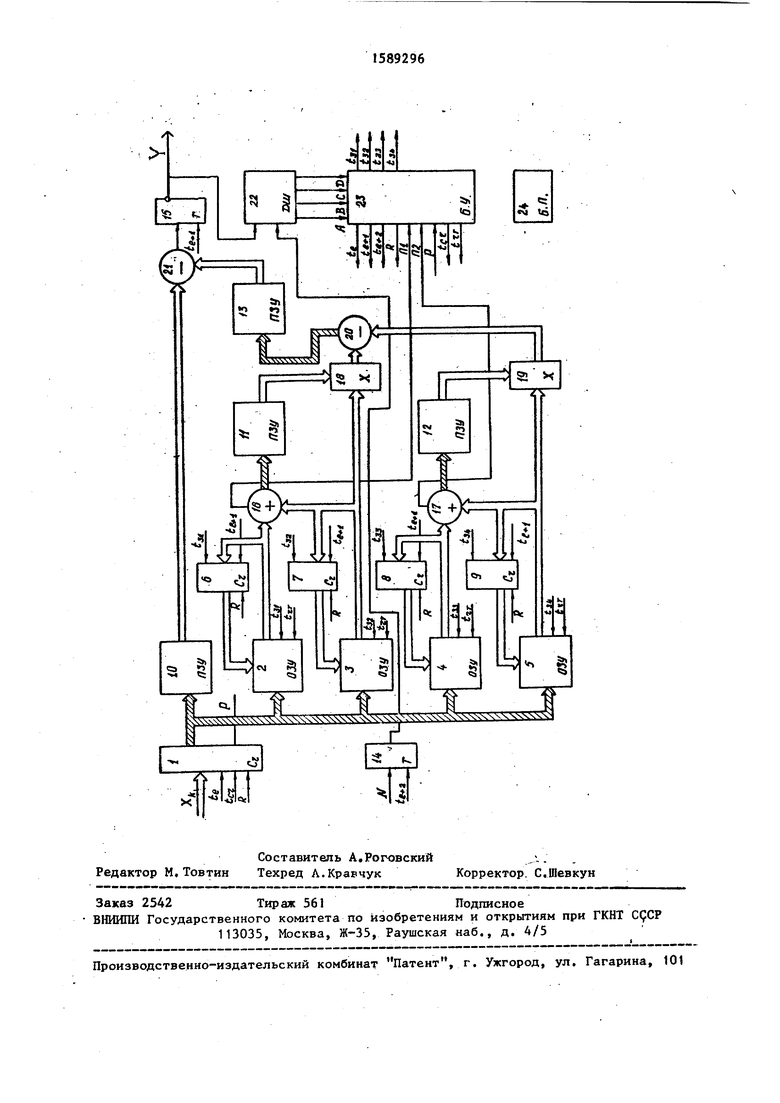

Сущность устройства для .и- рования нейрона поясняется блок-схемой. .

Устройство содержит входной двои . ный счетчик 1, группу оперативных запоминающих устройств (ОЗУ) 2,,3,4 и 5, группу двоичных счетчиков 6 - 9, группу постоянных запоминающих устройств (ПЗУ) 10 - 13, два триггера и 15, два сумматора 16 и 17, два умножителя 8 и 19, два вычитателя 20 и 21, дешифратор 22, блок 23 управления, блок 24 питания

Информационные входы счетчика 1. и триггера 14 являются входами уст- .ройства. ИнЛормационкый выход счетчика 1 соединен с адресными входами ОЗУ 2,3j4 и 5 и адресным входом ПЗУ 10. Информационные выходы ОЗУ 2 и 3 соединены с первым и вторым входами сумматора 16 и информационными входами счетчиков 6 и 7, а инЛор мационные выходы ОЗУ 4 и 5 соедине-. ны с первым и вторым входами сумма тора 17 и информа ионными .входами сумматора 17 и информ2циоцнь;мк входами счетчиков 8 и 9. Кроме того,информационные выходы ОЗУ 3 и 5 соединены с первыми входами умножителей 18 и 19. Информационные выходы счетчиков 6-9 связаны с информационными входами ОЗУ 2-5. Выходы сумматоров 16 и 17 соединены с адресными входами ПЗУ Пи 12, информационные выходы которых связаны соответственно с вторыми входами умножителей 18 и 19. Выход умножителя 18 является входом уменьшаемого, а умножителя 19 - входо вычитаемого вычитателя 20, выход которого соединен с адресным входом ПЗУ

589296

13. Информационный вход ПЗУ 10 соединен с входом хменьшаемого, а информационней выход ПЗУ 13 - с входом вычи- е таемого вычитателя 21, выход которого является входом триггера 15. Выход триггера 15, являющийся выходом устройства, соединен с первым входом дешифратора 22, второй вход которого

10 соединен с выходом триггера 1,4. Выходы дешифратора 22, выход переполнения счетчика 1 и выходы переноса.сумматоров 16 и 17 соединены с одноименными входами блока управления 23,Так15 товые выходы блока управления 23 соединены с одноименными тактовыми входами счетчика 1, триггеров 14 и 15 счетчиков 6 - 9, а также ОЗУ 2-5. Устройство работает следующим об,20 разом.

При включении блока 24 питания и запуска устройства блок.23 управления вырабатывает сигнал Р, который приводит в исходное, т.е. нулевое,

25 состояние содержимое счетчиков 1,6-9, Затем блок 23 управления генерируют - последовательность импульсов t. ,увеличивающих содержимое счетчика 1, выходы которого являются адресным:-;

30 входа№5 ОЗУ 2 - 5-с нуля до максимального значения, а также сигналы 3t- Зг 33, t34 для записи единицы в соответствующие счетчики i6 - 9

5

0

5

0

Кроме того, сигналы t,,, Сзз tg из блока 23 управления поступают на одноименные входы управления ОЗУ 2

5для записи содержимого счетчиков

6- 9 в ячейки памяти по,адресам,генерируемым счетчиком 1. Блок 23 управления при получении сигнала Р из счетчика 1, сообщающего о его переполнении, заканчивает приведение устройству в исходное состояните, которому соответствует содержимое всех ячеек ОЗУ 2-5 тождественно равное

1. Это необходимо для того, чтобы учесть, что соответствующие математические ожидания случайных многомер- ньк сигналов Х,, поступающих в дискретные моменты времени на вход устройства, равны 0,5.

В д icкpeтньгй момент времени,по сиг-, налу t, генерируемому блоком 23 управления, многомерный входной сигнал 5 , X2...,Xpj, поступающий из внешней среды, записывается в счетчик 1, где ,, г - число координат, tE const. Одновременно с сигналом t блок 23. управления

генерирует сигнал чтения - t, пос- тупаняций на одноименные входы соот- ветствукяцих оперативных запоминающих устройств 2 - 5. По сигналу ti лро- j исходит считывание содержимого ячеек памяти ОЗУ 2,3,4,и 5 по адресу ), записанному в счетчик . При этом из ОЗУ 2 считывается число п число случаев, когда после прихода 10 CHrtianaXи генерировалась команда :Y 1 в момент времени tfti выходе I устройства и поступала награда N

М,

.BilJ-XiLi-l -

Х.1 +

п

+ 2

Ct2

где

г т

Ye(n,l,

: В момент времени

,Г, а 1 1,2,3, Из ОЗУ 3 считывается число число случаев, когда после прихода сигнала Хц:уст- : ройством генерировалась команда Y 1, но на вход N не поступала : награда, т.е. N О,- Из ОЗУ 4 считы- вается число Х) число случаев, (когда после прихода сигнала Х, ко- 1 манда У не вырабатывалась, а награда I N поступала. Из ОЗУ 5 считывается чие I ло п число , когда пос- : ле прихода сигнала Х команда У уст- 1 ройством не вырабатывалась, т.е. Y о, и не поступала на вход N награ- да, . То есть каждому входному i многомерному сигналу Х соответству- : йт определенная строка в ОЗУ 2,3, 4 и.5.. , , .

За интервал времени, равный tg.)5

На базе постоянных запоминающих устройств 11 и 12 реализовано устро ство деления, т.е. эти ПЗУ осущест вляют отображение адресов

,. и , + , + 2,

поступающих с сумматоров 17 и 16, в соответствующие им обратные величины

1

, н- 2

20

25

п

, -ь п-ЧХк1+ 2

Вычисленные значения М, и М с умножителей 18 и 19 поступают на в ды вычитателя 20, где определяется разность М,-М.

Условие генерации команды Y(tg на выходе устройства в соответстви с описанием способа моделирования нейрона определяется по формуле:

- t

const, после прихода и записи с - в счетчик 1 многомерного входного

сигнала X|((tj), рассчитываются мате35

Y(te,)

Vo

1,если X(tg)5 -7 .42f

О,в противном случае,

40

порог генерации команды 1 + MI - Мг

Y, -- - степень предпо

- -|..-матичёские ожидания вероятности при- где V const - заранее заданный хода на вход N в момент времени t награды N(.b как при условии генерац ш команды Y(te,,,) на выходе устройства, так и без ее генерации.

Математическо е ожидание вероятности прихода на вход N награды при условии. генера1Ц1и команды Y на выходе устройства вычисляется на сумматоре 16, постоянном запоминающем устройстве 11 и умножителе 18 по формуле

тительности генерации команды Y на

для получения

выходе устройства If .

награды, 51X(tg) - сумма коорди 45 нат многомерного входного сигнала Xj5« Постоянное запоминающее устрой ство 10 осуществляет однозначное отображение адреса X|(tg), поступа щего со счетчика 1, в величину,рав

++

п

п

...

Х, -ь

+ 2

Математическое ожидание вероятнос- ти прихода на вход N награды Nltg) при условии, что команда на выходе устройства Y не будет генерировать-/ ся, вычисляется на сумматоре 17,noci тоянном запоминающем устройстве 12 и умножителе 19 по формуле.

.BilJ-XiLi-l -

Х.1 +

п

+ 2

На базе постоянных запоминающих устройств 11 и 12 реализовано устройство деления, т.е. эти ПЗУ осуществляют отображение адресов

,. и , + , + 2,

поступающих с сумматоров 17 и 16, в соответствующие им обратные величины

, н- 2

п

, -ь п-ЧХк1+ 2

Вычисленные значения М, и М с умножителей 18 и 19 поступают на входы вычитателя 20, где определяется разность М,-М.

Условие генерации команды Y(tg ) на выходе устройства в соответствии с описанием способа моделирования нейрона определяется по формуле:

Y(te,)

Vo

1,если X(tg)5 .42f

О,в противном случае,

порог генерации команды 1 + MI - Мг

Y, -- - степень предпочгде V const - заранее заданный

где V const - заранее заданный

тительности генерации команды Y на

для получения

выходе устройства If .

награды, 51X(tg) - сумма коорди- 5 нат многомерного входного сигнала Xj5« Постоянное запоминающее устройство 10 осуществляет однозначное отображение адреса X|(tg), поступающего со счетчика 1, в величину,рав0

5

о иХ5

ную сумме координат Х; входного сигнала, а постоянное запоминающее

устройство 13 осуществляет отображение адреса, поступающего из вычитателя 20, равного разности математических ожиданий, в величину б (М - Мп) -;r r:r:zi:r,. Вычитатель 21, на первый входЧоторого приходит

число, равное сумме координат входного сигнала X|(tg), а на второй вход число, равное б (М , - М), производит их сравнение. Если разность

Y

21 X ; - 0(М, - мрг О, то энак числа на выходе вычитателя 21 равен О, в противном случае - 1. По сигналу tg, , генерируемого блоком 23 управления, знак числа на выходе вычитателя 21 записывается в триггер 15, инвбрсньй выход которого является выходом устройства Y, а. также одним из выходов дешифратора 22, -Значение Y 1 говорит о генерации команды устройством в момент времени , а значение Y О - об ее отсутствии.

По сигналу tg,, генерируемому блоком управления, в счетчики 6-9 записывается содержимое ячеек памяти, соответствующих ОЗУ 2 - 5,считы- BaeNbix по адресу X)((tg). По окончании записи в счетчики 6-9 сигнал чтения - t ц блоком 23 управления снимается и ОЗУ 2-5 переходят в режим хранения информации.

В дискретный момент времени tp+u по сигналу генерируемому бло- .ком 23 управления, в триггер 14 записывается значение награды NCtg)- .Выход триггера 14 соединен с вторым входом дешифратора 22, который в зависимости от сочетания входных сигна лор Y(tg+l) и ) генерирует значение 1 на одном.из своих выходов, а на других - значение О. Выходы дешифратора 22 подключены к соответствующим входам блока 23 управления, которьй в зависимости от информационного значения, выходов дешифратора 22 генерирует один из сигнало

ъ -Зг. По

33.

или t

54

из

одному из этих сигналов один счетчиков 6-9 увеличивает свое

значение на единицу, после чего содержимое этого счетчика записывается в соответствующее ему оперативное запоминающее устройств по адресу - Xj,(tj), Выходы ПГ и П2 сумматоров 16 и 17 (выходы переносов переполнения) подключены к одноименным входам блока 23 управления. Сигналы П1 и П2 участвуют в формировании сигналов

St ния.

«t f It 1 t

t-iz t33 -И г блока 23 управле- Если значение П1 или П2 равно то П1 запрещает выработку сигналов t к t,2,, а П2 - t. После того, как в ячейки памяти одного из

5

0

5

четырех ОЗУ 2 - 5 по адресу X(tj) была произведена запись содержимого одного из счетчиков 6 - 9| устройство готово к новому циклу приема многомерного сигнала Х, генерации команды Y и приему награды N.

Технические преимущества изобретения проявляются в том, что за счет небольшого увеличения сложности и стоимости модели достигается значительное расширение ее функциональных возможностей - прежде всего объема запоминающих и распознаваемых сигналов. Благодаря этому предлагаемая модель при том же объеме пе- . рераёатываемой информации проще вследствие резкого сокращения числа связей между моделями.

Предложенный способ моделирования и основанное на нем устройство позволяют моделировать свойства избирательного изменения возбудимости биологических нейронов при обучении. Это способствует разработке перспективных направлений исследований в области нейробиологии.

30 Формула изобретения

5

0

5

1. Способ моделирования нейрона, предусматривающий прием многомерных входных сигналов и сигнала награды, нахождение суммы координат поступившего сигнала, генерацию сигнала команды при превьш1ении суммы координат заданной величины порога, о т л и - ч ающийся тем, что, с целью повышения точности моделирования поведения реального нейрона путем регулирования порога генерации сигнала команды в зависимости от прогно за информационного значения поступившего сигнала, в качестве сигнала награды используит заранее выделенный входной сигнал, при приеме входного сигнала устанавливают значения математического ожидания вероятностей прихода сигнала награды при условии генерации сигнала команды и в его от сутствии, величину порога генерации сигнала команды в ответ на поступив- .ший входной сигнал уменьшают или увеличивают в зависимости от знака разности установленных математических ожиданий и вероятности безошибочного прогноза этой разности, а сигналы о наличии или отсутствии возникшей

5

0

команды и поступившей награды запоминают, ...

2, Устройство для- моделир ования нейрона, содержащее три счетчика,два триггера и первый сумматор, блок 1та- тания, о т л и ,ч а ю щ е е с я тем, что, с целью повышения точности моделирования за счет учета свойств тимого регулир ования текущей эффективности генерации команды в ответ на входные воздействия в зависимости от их информационного значения,оно дополнительно .содержит два счетчика, второй сумматор, два умножителя, два вычитателя, четыре оперативных запоминающих устройства, четыре постоянных запоминающих устройства, дешифратор и блок управлениЯр при этом первый счетчик имеет г информационных входов, образующих первую группу входов, устройства, и г информационных выходов, соединенных с адресным входом первого постоянного запоминающего устройства и. адресными входами четырех оперативных запоминающих устройств, информационный-вход каждого

из которых соединен с информацион- ным выходом второго, третьего, четвертого или пятого счетчиков, информационные входы которых соединены с информационными выходами соответствующих оперативных запоминающих устройств, первые входы первого и второго сумматоров соединены с информационными выходами первого и третьего оперативных запоминающих устройств, а вторые входы - с информационньп Ш выходами второго и четвертого оперативных запоминающих устройств,выходы первого и второго сумматоров соединены соответств.енно с адресными входа

ми второго и третьего постоянных запоминающих устройств, информационный выход каждого из которых соединен с первым входом одного и з-, двух умножителей, второй вход- 1 аждого из которых соединен -с информационным входом второго или четвертого оперативных запоминающих устройств, причем выход первого умножителя соединен с входом уменьшаемого, а выход второго умножителя - с входом вычитаемого первого вычитателя, выход которого через четвертое постоянное запоминающее устройство соединен с входом вычитаемого второго вычитателя, вход уменьшаемого кото- .рого соединен с информационным-выходом первого постоянного запоминающе- - го устройства, а выход - с входом п ер- вого триггера, выход которого, являющийся выходом устройства, соединен с первым входом дешифратора, второй вход которого соединен с выходом вто- рого триггера, вход которого образует второй вход устройства, причем каждый из четырех выходов- дешифратора соединен с соответствующими входами блока управления, пятые п шестые вхо- -ды которого соединены с выходами переноса первого и второго сумматоров, а седьмой вход - с выходом переполнения первого счетчика, а выходь блока управления соединены с первым и вторым тактовыми входами и входом обнуления первого счетчика, тактовыми входами первого и второго триггеров, первыми и вторыми тактовыми .входами каждого оперативного запоминающего устройства и первыми и вто рыми тактовыми входами и входами обнуления второго, третьего, четвертого и пятого счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ моделирования целенаправленной деятельности нейрона и устройство для его осуществления | 1989 |

|

SU1737468A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОПОДОБНОЙ СЕТИ | 1992 |

|

RU2094843C1 |

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ НЕСТАЦИОНАРНОГО СЛУЧАЙНОГО ПРОЦЕССА СЕМИОТИЧЕСКОГО ТИПА | 1996 |

|

RU2133499C1 |

| КОРРЕЛЯЦИОННЫЙ АНАЛИЗАТОР ЧАСТОТНЫХ СВОЙСТВ ЛИНЕЙНОЙ СИСТЕМЫ | 2003 |

|

RU2242013C2 |

| Устройство для вычисления мультипликативной свертки | 1987 |

|

SU1451723A2 |

| Способ распознавания изображений и устройство для его осуществления | 1983 |

|

SU1238269A1 |

| ДИСКРЕТНАЯ СИСТЕМА ОЦЕНИВАНИЯ | 2007 |

|

RU2398258C2 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

Изобретение относится к цифровому моделированию биологических нейронов, предназначено для экспериментальных и теоретических исследований в нейробиологии и может найти применение в системах управления. Целью изобретения является повышение точности моделирования поведения реального нейрона путем обратимого регулирования порога генерации сигнала команды в зависимости от прогноза информационного значения ближайших следствий входного сигнала. При реализации способа, основанного на приеме сигналов, нахождении суммы их координат и генерации команды по достижению порога, осуществляют регулирование порога на основе установления матемитических ожиданий вероятностей прихода награды при условии генерации команды и ее отсутствия, причем порог уменьшают или увеличивают в зависимости от знака разности этих величин пропорционально уровням статистической значимости их различий. В устройство введены четыре оперативных запоминающих устройства для запоминания и распознавания следствий 2 R комбинаций R входных сигналов, а для регулирования порога - два сумматора, четыре постоянных запоминающих устройства, два умножителя и два вычитателя. Блок управления предназначен для управления работой устройства. 2 с.п. ф-лы, 1 ил.

| McCulluch W.S., Pitts W А logical calculus of the ideas imanent in nervous actvity.Bull | |||

| Math | |||

| Biophys., 1943, v,4, p.115 | |||

| Устройство для моделирования нейрона | 1980 |

|

SU894744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4518866, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-30—Публикация

1988-02-15—Подача