Изобретение относится к вычислительной :техн ;ке и может быть использовано при Проектировании цифровых систем гшвышек- :11ой надежности.

; Целью изобретения являегся сокращение аппаратурных затрат устройства.

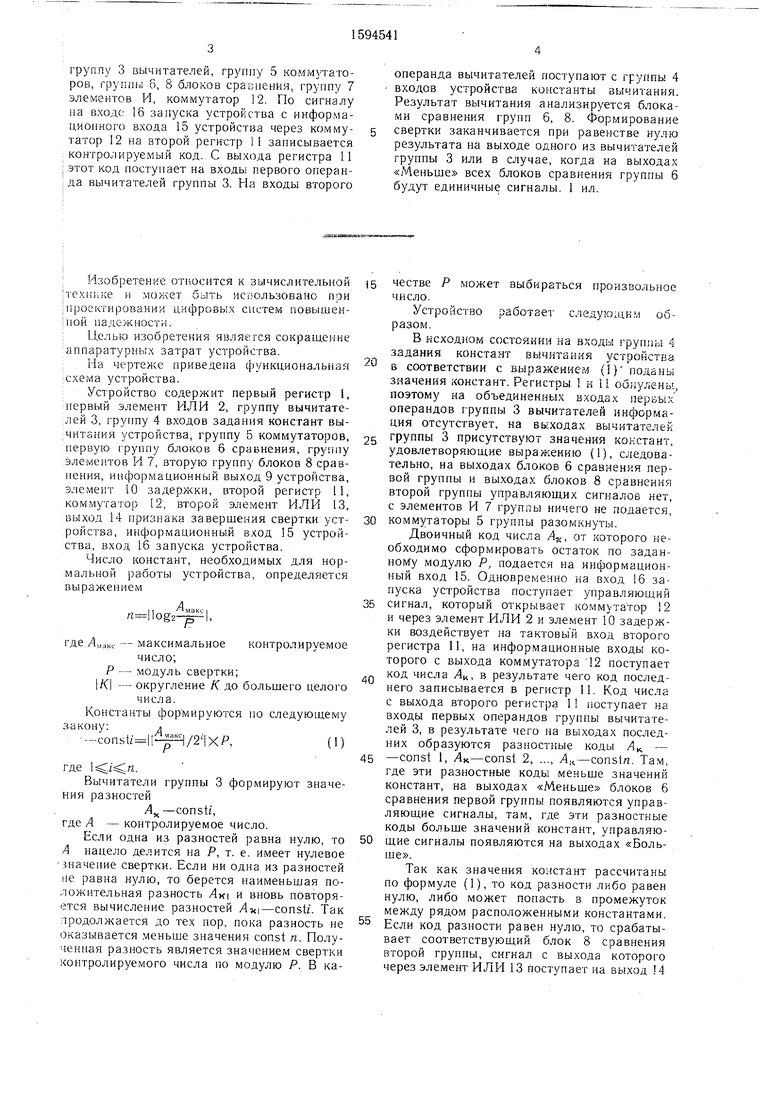

На чертеже приведе}1а функциональная :схема устройства.

Устройство содержит первый регистр I, первый элемент ИЛИ 2, группу вычитателей 3, группу 4 входов задания констант $ы- :Читания устройства, группу 5 коммутаторов, первую группу блоков 6 сравнения, группу элементов И 7, вторую группу блоков 8 сравнения, информационный выход 9 устройства, элемент 10 задержки, второй регистр 11, коммутатор 12, второй элемент ИЛИ 13, выход 14 признака завершения свертки устройства, информационный вход 15 устройства, вход 16 запуска устройства.

Число констант, необходимых для нормальной работы устройства, определяется выражением

n-|10g2%i|.

контролируемое

где Л,,,;|К(.. -- максимальное

число; Р - модуль свертки; К - округление /С до большего целого

числа.

Константы формируются по следующему закону:л

--соп8и |1 /2 1хЛ()

где .

Вычитатели группы 3 формируют значения разностей

А -const/, где А - контролируемое число.

Если одна из разностей равна нулю, то А нацело делится на Р, т. е. имеет нулевое -значение свертки. Если ни одна из разностей не равна нулю, то берется наименьшая положительная разность Лк| и вновь повторяется вычисление разностей /Iwi-const/. Так продолжается до тех пор, пока разность не оказывается меньше значения const л. Полученная разность является значением свертки контролируемого числа по модулю Р. В ка5 честве Р может выбираться произвольное число.

Устройство работает следующим образом.

В исходном состоянии на входы группы 4 задания констант вычитания устройства

-J в соответствии с выражением () поданы значения констант. Регистры 1 и 11 обнулены, поэтому яа объединенных входах первых операндов группы 3 вычитзтелей информация отсутствует, на выходах вычитателей

5 группы 3 присутствуют значения констант, удовлетворяюш,ие выражению {), следовательно, на выходах блоков 6 сравнения первой группы и выходах блоков 8 сравнения второй группы управляющих сигналов нет, с элементов И 7 группы ничего не подается,

0 коммутаторы 5 группы разомкнуты.

Двоичный код числа А.,, от которого необходимо сформировать остаток по заданному модулю Р, подается на информацион- пый вход 15. Одновременно на вход 16 запуска устройства поступает управляющий

5 сигнал, который открывает коммутатор 12 и через элемент .ИЛИ 2 и элемент Го задержки воздействует на тактовы й вход второго регистра 11, на информационные входы которого с выхода коммутатора 12 поступает

Q код числа Ли, в результате чего код последнего записывается в регистр 11. Код числа с выхода второго регистра 1I поступает на входы первых операндов группы вычитателей 3, в результате чего на выходах последних образуются разностные коды Л -

5 -const 1, Лх-const 2, ..., Лк-const«. Там, где эти разностные коды меньше значений констант, на выходах «Меньше блоков 6 сравнения первой группы появляются управляющие сигналы, там, где эти разностные коды больше значений констант, управляю0 щие сигналы появляются на выходах «Больше.

Так как значения констант рассчитаны по формуле (1), то код разности либо равен нулю, либо может попасть в промежуток между рядом расположенными константами. Если код разности равен нулю, то срабатывает соответствующий блок 8 сравнения второй группы, сигнал с выхода которого через элемент ИЛИ 13 поступает на выход 4

устройства, сигнализируя о том, что на выходе 9 сформирован остаток , а также устанавливает второй регистр П в нулевое состояние. Если код разности не равен нулю, то в промежутке между рядом расположенными константами /-и блок 8 сравнения первой группы выдает сигнал «Меньше, а (/+1)-й блок 6 срав нения первой группы выдает сигнал «Больше, следовательно, срабатывает /-и элемент И 7 группы, сигнал с выхода которого включает соответствующий коммутатор 5 группы, а через элемент ИЛИ 2 и элемент 10 задержки обеспечивает запись кода Лк-const i в регистр И. Этот процесс продолжается до тех пор, пока (Лк-const / - const / -...- -const ./7)const . в , случае последний блок 6 сравнения первой группы выдает сигнал «Меныие, который от кры- вает последний коммутатор 5 группы, записывает код г Акто6Р в первый регистр 1, через элемент ИЛИ 13 воздействует на вто- рой (упрашчяющий) выход устройства, сигнализируя об оконча1 ии процесса формирования остатка, а также обнуляет содержимое второго регистра 11. Код остатка остается на информационных выходах устройства до тех пор, пока на информационные входы 15 не поступит следующее число /4к+,, от которого необходимо сформировать оста- ток, а на вход 16 - сигнал запуска. При этом работа устройства осуществляется аналогично описанному выше.

Пример. Выполнение процесса свертки по модулю.

Пусть Лмакс 000; . Необходимо сформировать остаток для /1(999. Тогда

число констант rt |log2-y-| 8. Значения

констант в соответствии с (1) равны: const const const const const const const const . Тогда после записи кода числа 999 в регистр 11 на выходах группы вычитателей 3 образуются коды: первого 495; второго - 747; третьего - 873;

четвертого - 936; пятого - 957; шестого

978; седьмого - 985; восьмого - 992. Поэтому на выходе только первого блока 6 сравнения первой группы появляется сигнал «Меньше (), а на выходах остальных блоков 6 сравнения появляется сигнал «Больше. Следовательно, на первом цикле работы устройства в регистр 11 записывается код числа 495.

На втором цикле работы на выходах вычитателей 3 формируются коды следуюш,их чисел: первого - 9; второго - 243; третьего - 369; четвертого - 432; пятого - 453; шестого - 474; седьмого - 481; восьмого - 488. Поэтому в результате сравнения со своими константами срабатывает второй элемент И 7 группы ( и ) и Б регистр 11 записывается код числа 243, зате.м в регистр 11 последовательно записываются коды чисел 1 17; 54; 12 и, наконец, 5 5 Поэтому на шестом цикле работы последний блок 6 сравнения первой группы выдает сигнал «Меньше, в результате чего код числа «5 записывается в регистр 1 и поступает на информационный вы.ход устройства.

Формула изобретения

Устройство для свертки по произвольному модулю, содержащее группу вычитателей, две группы блоков сравнения, группу эле5 ментов И, группу коммутаторов, первый регистр и первый элемент МЛИ, причем входы первого операнда вычитателей группы подключены к соответстзующил: входа ; зада};;: - констант вычитания устройсгва, выходы ре зультата вычитателей группы соединены

0 с первыми информационными входами соответствующих блоков сравнения первой и второй групп и с информационными входами соответствующих коммутаторов , вторые информационные входы блоков сравне5 ния второй группы подключены к шине нулевого потенциала устройства, вы.код «Меньше каждого /-ГО блока сравнения первой группы соединен с первым входом г-го элемента И группы (;f :rz-i, где ri |logoX

0 ../5..,,,,,,

А-р- I Лу.акс - наибо.;1ьо1ее контролируемое число; Р значение модуля свертки) выход первого регистра является кнформа- ционны:у1 выходом устройства, отличающе2 еся гем, что, с целью сокращения аппаратурных затрат устройства, оно содержит коммутатор, элемент задержки, второй регистр и второй элемент ИЛИ, причем информационный вход коммутатора является информационным входом устройства, выход

0 коммутатора и выходы коммутаторов группы кроме последнего, объединены по с хеме МОНТ.4ЖНОЕ ИЛИ и соединены с информационным входом второго регистра, выход последнего коммутатора группы соед:-5нен с информационнььм входом первого регистра, выход каждого ;-го элемента И группы соединен с управляющим входом /-го коммутатора группы и г-м Бходог,; п срвого эл(. ме1-11-а ИЛИ, выход которого через элемент задержки соединен с тактовым входом второго реQ гистра, выход которого соединен с входами второго операнда вычитателей группы, выход «БoльпJe каждого (/-f 1 )-го бл ока сравнения первой группы соединен с вторым входом /-ГО элемента И группы, выходы равенства блоков сравнения второй группы п вы5 ход «Меньше последнего блока сравнения первой группы соединены с соответствующими входами второго элемента ИЛИ, выход которого соединен с установочным входом Etoporo .pet-HCtpa и й6ляetc i выходом первого элемента ИЛИ, выход «Меньше

признака завершения свертки устройства, последнего блока сравнения первой группы

вход запуска устройства подключен к управ-соединен с управляющим входом последнего

ляющему входу коммутатора, установочно-коммутатора группы и тактовым входом перму входу первого регистра и (/-|-1)-му входувого регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 1991 |

|

RU2024925C1 |

| Устройство для свертки по произвольному модулю | 1987 |

|

SU1509903A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Вычислительное устройство | 1981 |

|

SU1136147A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании цифровых систем повышенной надежности. Цель изобретения - сокращение аппаратурных затрат устройства. Устройство содержит регистры 1,11, элементы ИЛИ 2,13, элемент задержки 10, группу 3 вычитателей, группу 5 коммутаторов, группы 6,8 блоков сравнения, группу 7 элементов И, коммутатор 12. По сигналу на входе 16 запуска устройства с информационного входа 15 устройства через коммутатор 12 на второй регистр 11 записывается контролируемый код. С выхода регистра 11 этот код поступает на входы первого операнда вычитателей группы 3. На входы второго операнда вычитателей поступают с группы 4 входов устройства константы вычитания. Результат вычитания анализируется блоками сравнения групп 6,8. Формирование свертки заканчивается при равенстве нулю результата на выходе одного из вычитателей группы 3 или в случае, когда на выходах "Меньше" всех блоков сравнения группы 6 будут единичные сигналы. 1 ил.

| Устройство для свертки по модулю | 1983 |

|

SU1124310A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство | |||

| Устройство для свертки по произвольному модулю | 1987 |

|

SU1509903A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-23—Публикация

1988-10-05—Подача