тателя, выход третьего коммутатора соединен с первым информационным входом второго коммутатора кодов, второй информационный вход которого соединен с выходом второго элемента задержки, выход второго коммутатора кодов соединен с информационным входом седьмого сумматора-вычитателя, выход четвертого коммутатора соединен с первым информационным входом третьего коммутатора кодов, второй информационный вход которого соединен с выходом третьего элемента задержки, информационный вход которого соединен с выходом старшего разряда четвертого коммутатора, выход пятого коммутатора соединен с первым информационным входом четвертого коммутатора кодов, второй информационный вход которого соединен с выходом четвертого элемента задержки, информационный вход которого соединен с выходом старшего разряда пятого коммутатора, выходы третьего и четвертого коммутаторов кодов соединены с первыми информационными входами соответственно четвертого и первого сумматоров-вычислителей, последовательный вход первого блока регистров соединен с информационным выходом первого сумматора, последовательньй информационный выход второго блока регистров соединен с вторым информационным входом седьмого сумматора-вычитателя, информационньй выход которого соединен с первым информационным входом пятого сумматора-вычитателя, информационный выход которого соединен с вторым информационным входом первого сумматора-вычитателя, последовательный выход третьего блока i регистров соединен с вторым информационным входом шестого сумматоравычитателя, информационный выход которого соединен с вторым информационным входом второго сзгмматора-вычитателя, информационный выход которого соединен с вторым информационным входом четвертого сумматоравычитателя, информационный выход: которого соединен с последовательны информационным входом третьего блока регистров и третьим информационным выходом устройства, информационный выход пятого коммутатора соединен с вторым информационным входом пятого сумматора-вычитателя, вход

6147

первого элемента задержки соединен с выходом старшего разряда второго коммутатора, информационньй вход второго элемента задержки соединен 5 с выходом старшего разряда третьего коммутатора, информагщонный выход третьего сумматора-вычитателя соединен с первым информационным входом восьмого сумматора-вычитателя, ин-.

to формационный выход восьмого сумматора-вычитателя соединен с четвертым информационным выходом устройства, с первыми информационными входами вьгчитателя и второго сумматора и

J5 с последовательным информационным входом четвертого блока регистров, вторые информационные входы восьмого сумматора-вычитателя и вычитателя соединены соответственно с вторым и

0 третьим информационными входами устройства, второй информационный вход второго сумматора соединен с третьим информационным входом устройства, информационные выходы второго

5 сумматора и вычитателя соединены соответственно с пятым и шестым информационными выходами устройства, причем первый вход блока управления подключен к первому информационному

0 выходу первого сумматора, второй вход блока управления подключен к второму информационному выходу четвертого сумматора-вычитателя, третий вход блока управления подключен

К выходам знаковых разрядов вычитателя, второго cjTMMaTopa и восьмого сумматора-вычитателя, выход блока управления соединен с управляющими входами первого, второго, третьего,

четвертого, пятого, шестого и седьмого блоков регистров первого, второго, третьего, четвертого и пятого коммутаторов, первого, второго, третьего и четвертого элементов задержки, первого, второго, третьего и четвертого коммутаторов кодов,

t .

первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого сумматоров-йычитателей.

2. Устройство по п. 1, отличающееся тем, что первый, второй, третий и четвертьй блоки регистров содержат п параллельно соединенных сдвиговых регистров (п

1, 2, ..., It , где V - разрядность операндов), входы первого, второго, третьего и четвертого блоков регистров соединены с соответствукйцими

последовательными входами блоков регистров, последовательные выходы сдвиговых регистров первого, второго, третьего и четвертого блоков регистров соединены с последователь ными выходами соответствующих блоков регистров, параллельные выходы сдвиговых регистров первого, второго, третьего и четвертого блоков регистров соединены с параллельными выходами соответствующих блоков регистров, а пятый, шестой и седьмой блоки регистров содержат п парал136147

лельно соединенных сдвиговых регистров ( п 1, 2, ...,1, где 1 разрядность операндов), причем параллельные входы сдвиговых регистров соединены с параллельными входами соответственно пятого, шестого и седьмого блоков регистров, выходы старших разрядов п-го сдвигового регистра пятого, йестого и седьмого блоков регистров соединены с последовательными входами каждого сдвигового регистра соответственно в пятом, щестоми седьмом блоках регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Делительное устройство | 1983 |

|

SU1168929A1 |

1. ВЫЧИСЖТЕЛЬНОЕ УСТРОЙСТВО, содержащее первьй, второй, третий и четвертый блоки регистров, первый, второй, третий и четвертый коммутаторы, первьй, второй и третий сумматоры-вычитатели, вычитатель, первый сумматор и блок управления,, причем последовательный выход первого блока регистров соединен с первым информационным входом первого сумматора, информадаонный выход которого соединен с первым выходом результата устройства, выход первого коммутаторй соединен с вторым информационным входом первого сумматора, информахщонньй выход первого сумматора-вычитателя соединен с вторым информационным вькодом результата устройства и последовательным входом второго блока регистров, первьй информационньй вход второго сумматора-вычитателя соединен с выходом четвертого коммутатора, первьй информационньй вход третьего сумматора-вычитателя - с последовательным выходом четвертого блока регистров, а второй информационньй вход третьего сумматора-вычитателя с первым информационным входом .устройства, отличающееся тем, что, с.целью повышения быстродействия за счет параллельной обработки кодов, оно содержит пятьй, шестой и седьм.ой блоки регистров, пятьй коммутатор, первьй, второй, третий и четвертьй элементы задержки, первьй, второй, третий и четвер.тьй коммутаторы кодов, с четвертого по восьмой сумматоры-нычитатели, причем параллельньй информационньй выход первого блока регистров соединен с параллельным информационным входом пятого блока регистров, параллельньй информационньй выход котоКЛ рого соединен с информационным входом первого коммутатора, параллельньй информационньй выход второго g блока регистров соединен с параллельным информационным входом шестого блока регистров, параллельньй информа1щонньй выход которого соеди&0 СГ нён с информационными входами третьего, и четвертого коммутаторов, па- раллельньй информационньй выход третьего блока регистров соединен с параллельным информационн№4 входом седьмого блока регистров, тараллельньй информационньй выход которого соединен с информационными входами второго и пятого коммутаторов, выход второго коммутатора соединен с первым информационным входом первого коммутатора кодов, второй информационный вход которого соединен с выходом первого элемента задержки, выход первого коммутатора кодов соединен с первым информационным входом шестого сумматора-вычи

1

Изобретение относится к цифровой вычислительной технике и предназначено для вычисления тригонометрических функций и преобразования координат.

Известны устройства, работающие по алгоритму Волдера и содержащие регистры, сумматоры-вьгчитатели, обработка информации в которых ведется по четырем каналам СОНаиболее близким по технической сущности к изобретению является устройство, содержащее регистры, сумматоры, вычислитель, коммутаторы и сумматоры-вьгчитатели. УЬтройство работает по алгоритму двойных итераций и предназначено для вычисления тригонометри еских функций и преобразования координат 2j,

Недостатком известных устройств является их низкое быстродействие.

Цель изобретения - повьшение быс;родействия устройства за счет парал лельной обработки информации в каждом из каналов.

Поставленная цель достигается тем, что вьиислительное устройство, содержащее первый, второй, третий и четвертый блоки регистров, первый, второй, третий и четвертый коммутаторы, первый, второй и третий сумматоры-вьгчитатели, вычитатель, первьй сумматор и блок управления, причем последовательный выход первого блока регистров соединен с первым информационным входом первого сумматора, информационный выход которого

соединен с первым информационным выходом результата устройства, выход первого коммутатора соединен с вторым информационным входом первого сумматора, информационный выход первого сумматора-вычитателя соединен с вторым информационным выходом результата-устройства и последовательным входом второго блока регистров, первый информационный вход второго сумматора-вьиитателя соединен с выходом четвертого коммутатора первый информационный вход третьего сумматора-вычислителя - с последовательным выходом четвертого блока регистров, а второй информационный вход третьего сумматора-вьгчитателя с первым информационным входом уст- ройства, дополнительно содержит пятый, шестой и седьмой блоки регистров, пятый коммутатор, первый, второй, третий и четвертый элементы задержки, первый, второй, третий и четвертый коммутаторы кодов, с четвертого по восьмой сумматоры-вычитатели, причем параллельный информационный выход первого блока регистров соединен с параллельным информа1щонным входом пятого блока регистров, параллельный информационный выход которого соединен с информационным входом первого коммутатора, параллельный информационный выход второго блока регистров соединен с параллельным информационным входом шестого блока регистров, параллельный информационный выход которого

31

соединен с информационными входами третьего и четвертого комьтутаторов, параллельньй информационньй выход третьего блока регистров соединен с параллельным информационным входом седьмого блока регистров, параллельный информационньй выход которого соединен с информационными входами второго и пятого коммутаторов, выход второго коммутатора соединен с первым информационным входом первого коммутатора кодов, второй информационный вход которого соединен с выходом первого элемента задержки, выход первого коммутатора кодов соединен с первым информационным входом шестого сумматора-вычитателя, выход третьего коммутатора соединен с первым информационным входом второго коммутатора кодов, второй информационный вход которого соединен с выходом второго элемента задержки, выход второго коммутатора кодов соединен с информационным входом седьмого сумматора-вычитателя, выход четвертого коммутатора соединен с первым инфррмацибнньм входом третьего коммутатора кодов, второй информационньй вход которого соединен с выходом третьего элемента задержки, информационный вход которого соединен с выходом старшего разряда четвертого коммутатора, выход пятого коммутатора соединен с первым информационным входом четвертого коммутатора кодов, второй информационный вход которого соединен с выходом четвертого элемента задержки, информационный вход которого соединен с выходом старшего разряда пятого коммутатора, информационные выходы третьего и четвертого коммутаторов кодов соединены с первыми информационными входами соответственно четвертого и первого сумматоров-вычитателей, последовательньй информационньй вход первого блока регистров соединен с информационным выходом первого сумматора, последовательный информационньй выход второго блока регистров соединен с вторым информационным входом седьмого сумматора-вычитателя, инормационньй выход которого соединен с первым информационным входом пятого сумматора-вычитателя, информационньй выход которого соединен с вторым информационным вхЬдЬм перво361474

го сумматора-вьтитателя, последова,тельньй информационньй выход третье го блока регистров соединен с вторым информационным входом шестого сумма5 тора-вьгчитателя, информационньй выход которого соединен с вторым информационным входом второго сумматора-вычитателя, информационньй выход которого соединен с вторым информационным входом четвертого сумматоравычитателя, информационньй выход которого соединен с последовательным информационным входом третьего блока регистров и третьим информационным

15 выходом устройства, информадаонньй выход пятого коммутатора соединен с вторым информационным входом пятого сумматора-вычитателя, информационньй вход первого элемента задержки

20 соединен с выходом старшего разряда второго коммутатора, информационньй вход второго элемента задержки соединен с выходом старшего разряда третьего коммутатора, инфор5 мационньй выход третьего сумматоравычитателя соединен с первым информационным входом восьмого сумматора-вычитателя, информационньй выход восьмого сумматора-вычитателя сое3Q динен с четвертым информационным

выходом устройства, с первыми информаЦионными входами вычитателя и второго сумматора и с последовательным информационным входом четвертого

блока регистров, вторые информационные входы восьмого сумматора-вычитателя и вычитателя соединены соответственно с вторым и третьим информационными входами устройства, второй информационньй вход второго

сумматора соединен с третьим информационным входом устройства, информационные выходы второго сумматора и вычитателя соединены соответственно

5 с пятым и шестым информационными выходами устройства, причем первьй вход блока управления подключен к первому информационному выходу первого сумматора, второй -вход блока

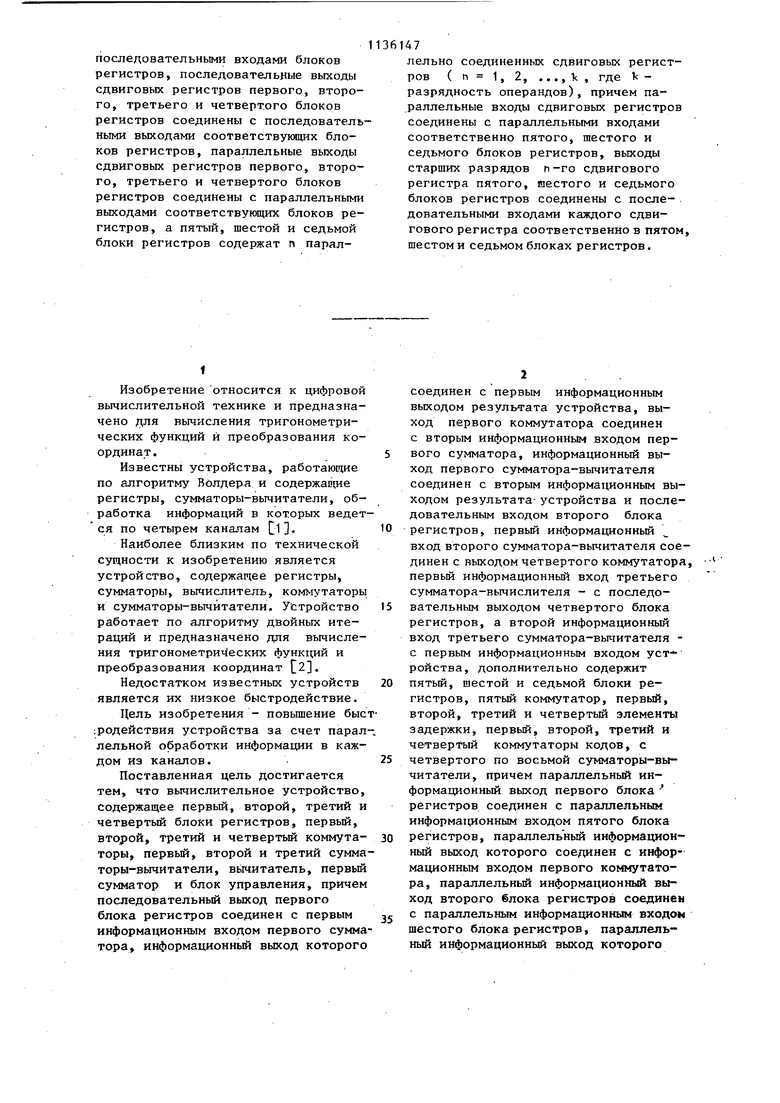

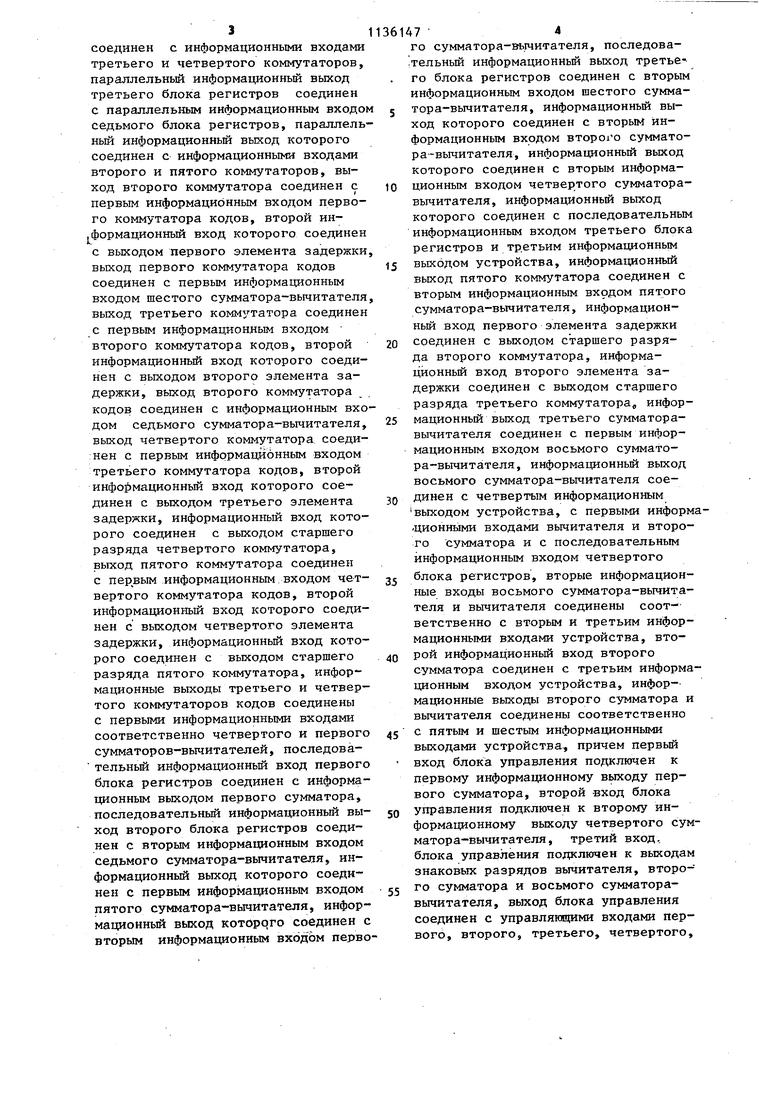

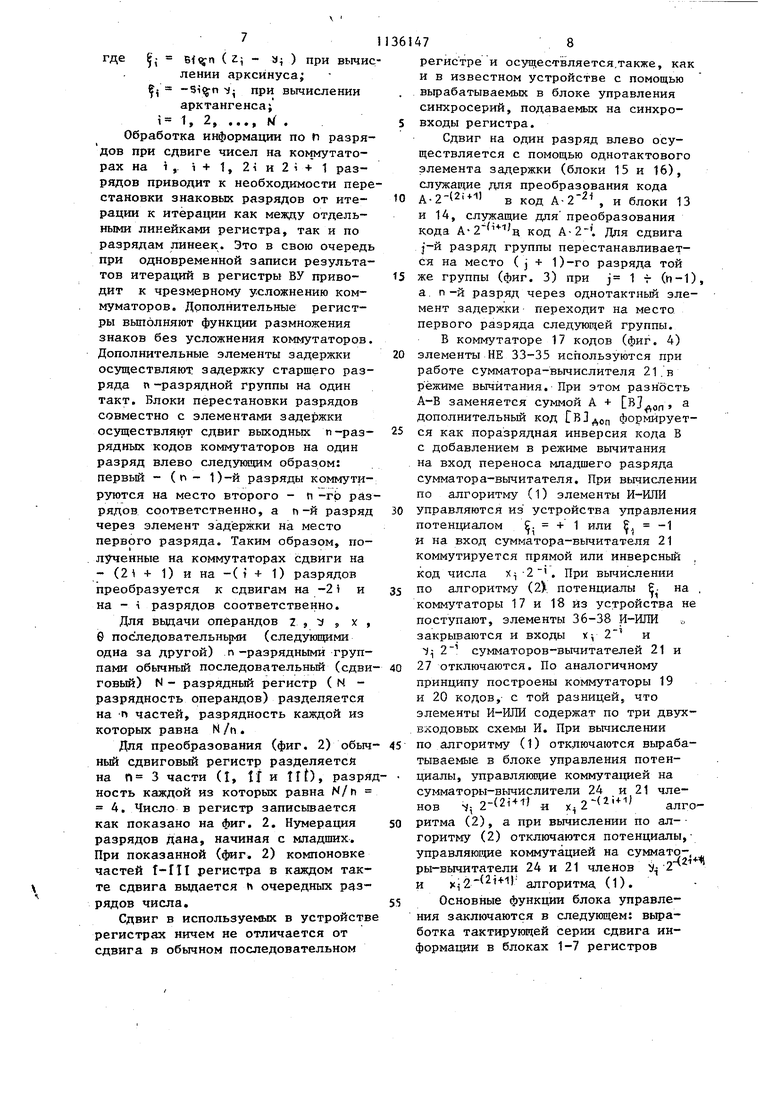

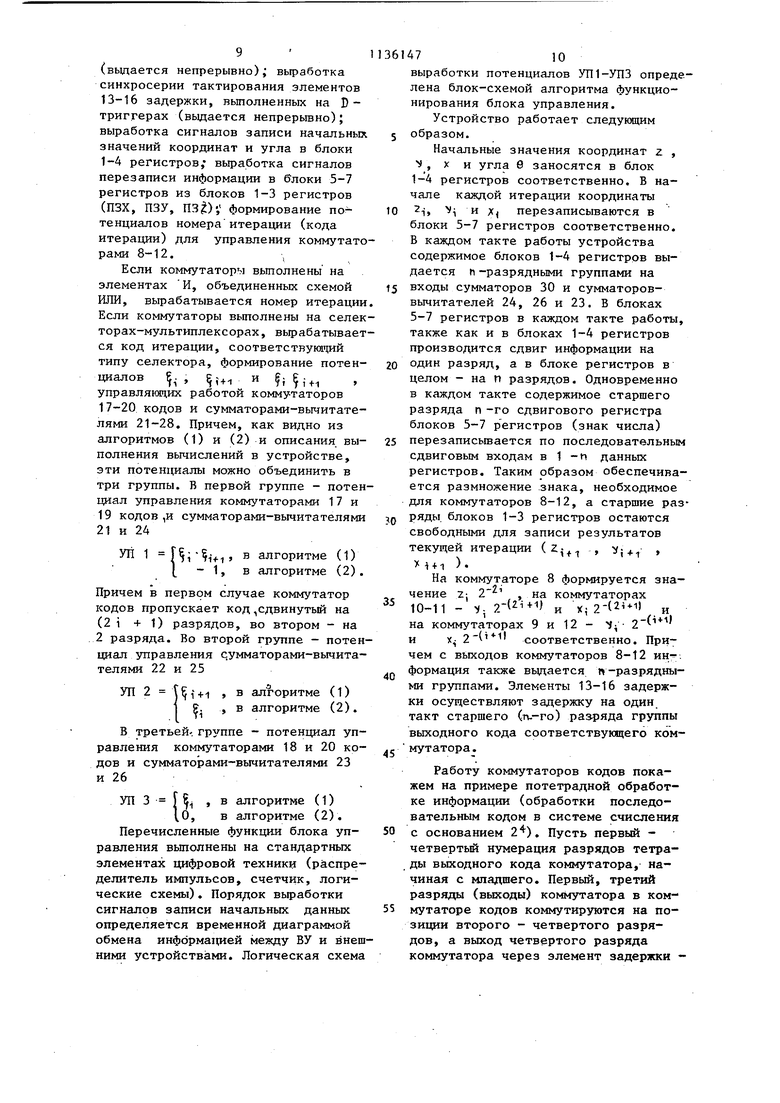

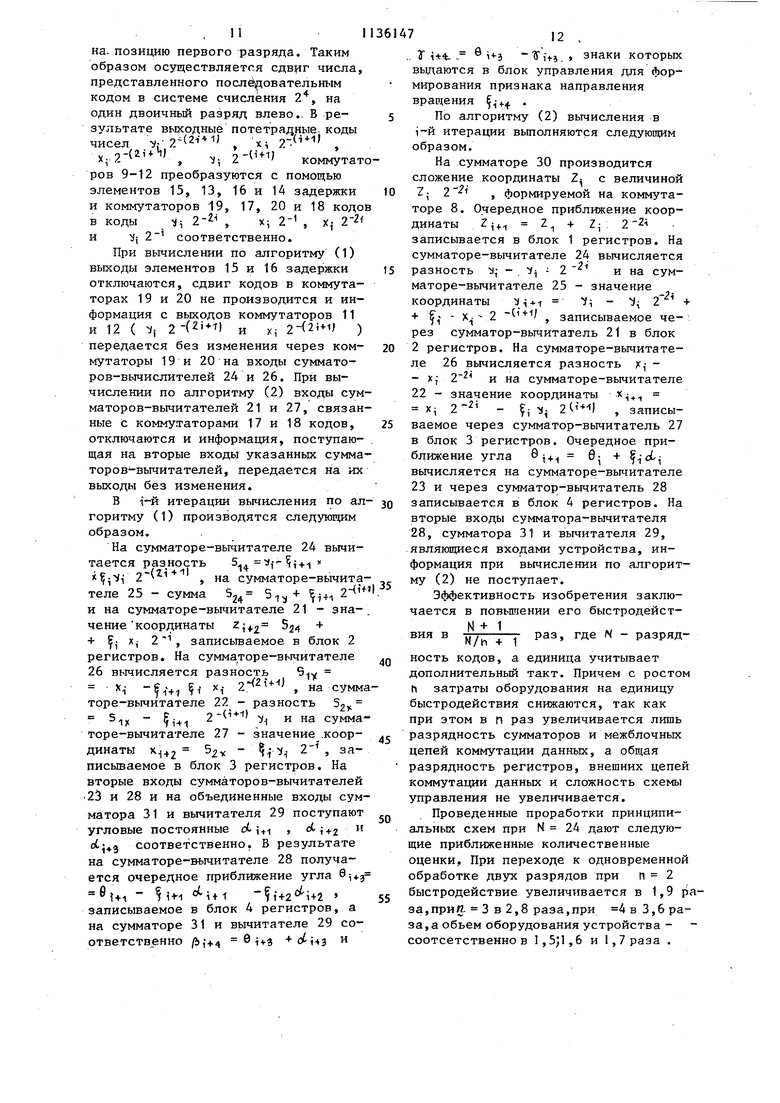

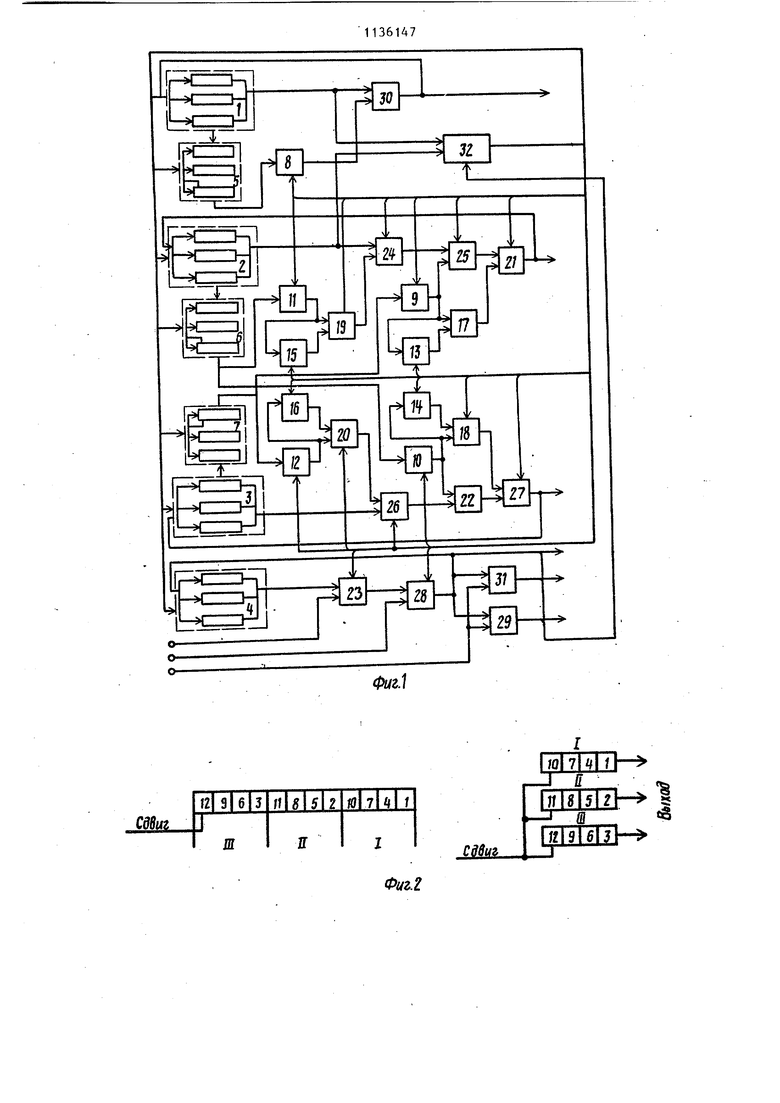

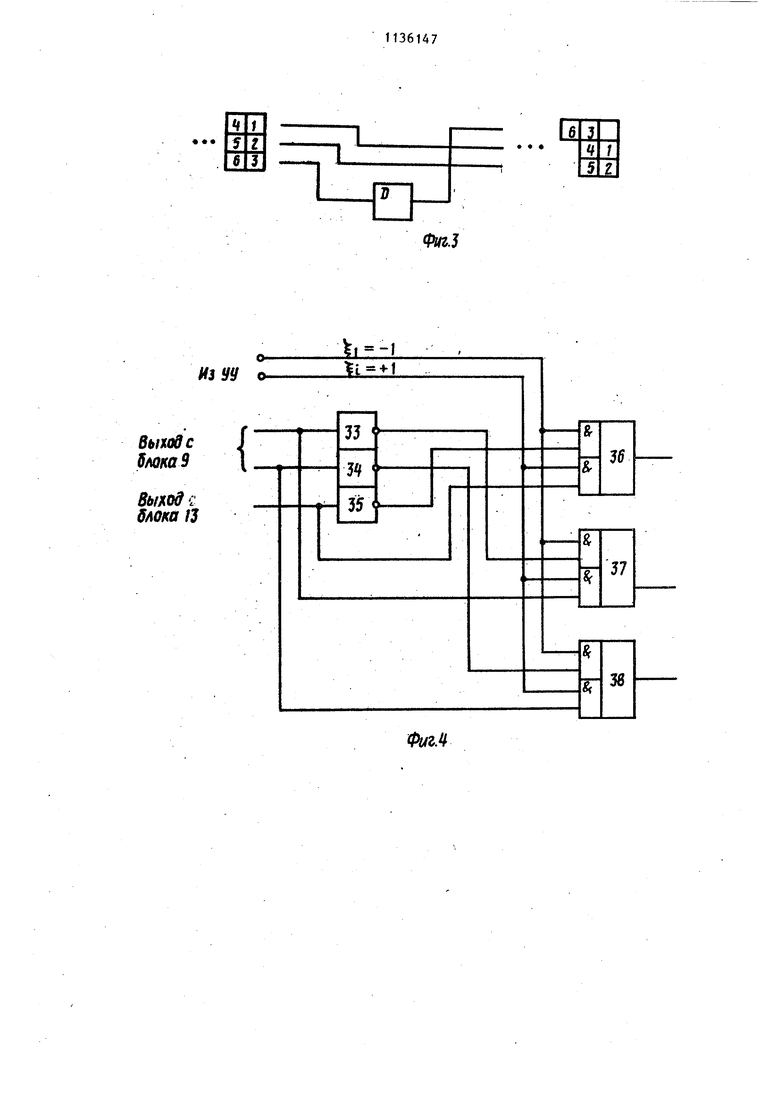

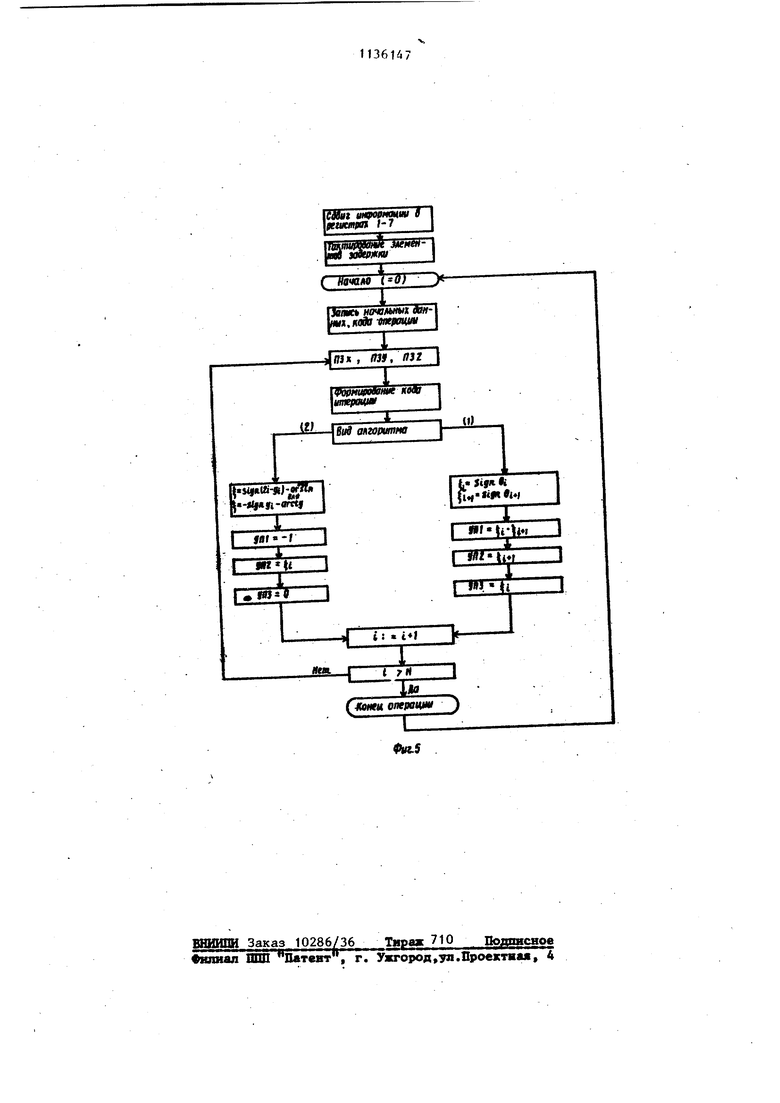

0 управления подключен к второму информационному выходу четвертого сумматора-вычитателя, третий вход, блока управления подключен к выходам знаковых разрядов вычитателя, второго сумматора и восьмого сумматоравычитателя, выход блока управления соединен с управлякщими входами первого, второго, третьего, четвертого. пятого, шестого и седьмого блоков регистров первого, второго, третьего, четвертого и пятого коммутаторов первого, второго, третьего и четвертого элементов задержки, первого, второго, третьего и четвертого коммутаторов кодов, первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого сумматороввычитателей. При этом первьй,второй, третий и четвертый блоки регистров содержат h параллельно соединенных сдвиговьж регистров (h 1, 2, ...,1, где V- разрядность операндов), входы первого, второго, третьего и четвертого блоков регистров соединены с соотвётствукщими последовательными входами блоков регистров, последова тельные выходы сдвиговых регистров первого, второго, третьего и четвертого блоков регистров соединены последовательными выходами соответствующих блоков регистров, парал лельные выходы сдвиговых регистров первого, второго, третьего и четвертого блоков регистров с оедйнены с параллельными выходами соответствунидих блоков регистров, пятый, шестой и седьмой блоки регистров содержат п параллельно соединенных сдвиговых регистров (п 1, 2, . .., где 1с- разрядность операндов), причем параллельные входы сдвиговых регистров соединены с параллельными входами соответственно пятого, шестого и седьмого блоков регистров, выходы старших разрядов и -го сдвиг вого регистра пятого, шестого и седьмого блоков регистров соединены с последовател-ьными входами каждого сдвигового регистра соответственно в пятом, шестом и седьмом блоках регистров. На фиг. 1 представлена структурная схема вычислительного устройства; на фиг. 2 - пример преобразования последовательного кода в код, представленный последовательными п-разрядными группами для случая N 12 и п 3-, на фиг. 3 - пример, иллюстрируклций сдвиг (задержку) на один разряд влево числа, представле ного последовательными и-разрядны. ми группами , на фиг, 4 - функциональная схема коммутатора кодов-, на фиг. 5 - блок-схема алгоритма функционирования б41ока управления. 1 7, 6 Блок управления может быть выполнен в виде блока с микропрограммным управлением. ВУ (фиг. 1) содержит с первого по седьмой блоки 1-7 регистров, с первого по пятый коммутаторы 8-12, с первого по четвертый элементы 1316 задержки, с первого по четвертый коммутаторы 17-20 кодов, с первого по восьмой сумматоры-вычитатели 21-. 28, вычитатель 29, первый и второй сумматоры 30 и 31,.блок 32 управления. Для преобразования кодов (фиг,2) сдвиговьй регистр разделен на части I, Пи III. Коммутатор кЬдов (фиг.4) содержит первый-третий элементы НЕ 33-35, первый-третий элементы И-ИЛИ 35-38. Разрядность линеек равна N/п (N - разрядность чисел) и информация в них размещается таким образом, что в каждом такте сдвига на последовательных выходах линеек появляется h очередных разрядов информации. Сумматоры, вычитатель и сумматоры- вычитатели также вьтолнены п -разрядными. Вычислейия в ВУ производятся по алгоритму двойных итераций: v.rV.M5,.«,. ...-,.. +2 ®ur®i4r itl i + ( i Y ) ft 0. -KJL . , j.ti .. lo-a H4- где x , S; I 6i - значения координат и угла .на i-M шаге; oi-rwrctfr2 - угловая постоянная;i s4nVl -l 1 0.2,4,..., N . а также по алгоритму двойных шагов: V.2-,., х.-х... (2) г. z. + z.2 ifi +1 7 где j ( Z; - S4 ) при вычи лении арксинуса; 5 -i при вычислении арктангенса; Обработка информации по П разря дов при сдвиге чисел на коммутаторах на i, i + 1, 2 i и 2 i + 1 разрядов приводит к необходимости пер становки знаковых разрядов от итерации к итерации как между отдельными линейками регистра, так и по разрядам линеек. Это в свою очеред при одновременной записи результатов итераций в регистры ВУ приводит к чрезмерному усложнению коммуматоров. Дополнительные регистры вьшблняют функции размножения знаков без усложнения коммутаторов Дополнительные элементы задержки осзтцествляют задержку старшего разряда п-разрядной группы на один такт. Блоки перестановки разрядов совместно с элементами задержки осуществляют сдвиг выходных п-разрядных кодов коммутаторов на один разряд влево следутотщм образом: первьй - ( Г1 - 1)-й разряды коммутируются на место второго - п го раз рядов соответственно, а п-и разряд через элемент задержки на место первого разряда. Таким образом, полученные на коммутаторах сдвиги на - (2 + 1) и на -(t + 1) разрядов преобразуется к сдвигам на -2 и на - i разрядов соответственно. Для выдачи операндов 2 , :1 у х 6 последовательнь|ми (следующими одна за другой) п-разрядными группами обычный последовательный (сдви говый) N - разрядный регистр (N разрядность операндов) разделяется на частей, разрядность каждой из которых равна N/п. Для преобразования (фиг. 2) обыч ный сдвиговый регистр разделяется на h 3 части (I, tf и ITt), разря ность каждой из которых равна N/n А. Число в регистр записывается как показано на фиг. 2. Нумерация разрядов дана, начиная с младших. При показанной (фиг. 2) компоновке частей f-fll регистра в каждом такте сдвига вьщается h очередных разрядов числа. Сдвиг в используемых в устройств регистрах ничем не отличается от сдвига в обычном последовательном 7 регистре и осуществляется,также, как и в известном устройстве с помощью вьфабатываемых в блоке управления синхросерий, подаваемых на синхровходы регистра. Сдвиг на один разряд влево осуществляется с помощью однотактового элемента задержки (блоки 15 и 16), служащие для преобразования кода А-2- 2+-) в код А-22 , и блоки 13 и 14, служащие для преобразования кода А-2 а код . Для сдвига j-й разряд группы перестанавливается на место (j + 1)-го разряда той же группы (фиг. 3) при j 1 т (n-l), а. п-и разряд через однотактньй элемент задержки- переходит на место первого разряда следующей группы. В коммутаторе 17 кодов (фиг. 4) элементы НЕ 33-35 используются при работе сумматора-вычислителя 21.в режиме вычитания. При этом разность А-В заменяется суммой А + в , а дополнительньй код ГвЗдо формйруется как поразрядная инверсия кода В с добавлением в режиме вычитания на вход переноса младшего разряда сумматора-вычитателя. При вычислении по алгоритму (1) элементы И-ИЛИ управляются из устройства управления потенциалом . + 1 или , -1 и на вход сумматора-вычитателя 21 коммутируется прямой или инверсньй , код числа . При вычислении по алгоритму (2Х потенциалы на , коммутаторы 17 и 18 из устройства не поступают, элементы 36-38 И-ИЛИ закрываются и входы Х; и :j 2 сумматоров-вычитателей 21 и 27 отключаются. По аналогичному принципу построены коммутаторы 19 и 20 кодов, с той разницей, что элементы И-ИЛИ содержат по три двухвходовых схемы И. При вычислении по алгоритму (1) отключаются вырабатываемые в блоке управления потенциалы, управляющие коммутацией на сумматоры-вьтислители 24 и 21 членов , 2-(2Н1 и . алгоритма (2), а при вычислении по ал- горитму (2) отключаются потенциалы,управляющие коммутацией на суммато-, ры-вычитатели 24 и 21 членов и xi2 l алгоритма (1). Основные функции блока управления заключаются в следующем; выработка тактирующей серии сдвига информации в блоках 1-7 регистров 9 (выдается непрерывно); вьфаботка синхросерии тактирования элементов 13-16 задержки, ньшолненных на D триггерах (выдается непрерывно); выработка сигналов записи начальных значений координат и угла в блоки 1-4 регистров, выработка сигналов перезаписи информации в влоки 5-7 регистров из блоков 1-3 регистров (ПЗХ, ПЗУ, ПЗ)-; формирование потенциалов номераитерации (кода итерации) для управления коммутат рами 8-12., Если коммутаторы вьтолнены на элементах И, объединенных схемой ИЛИ, вьфабатывается номер итерации Если коммутаторы выполнены на селек торах-мультиплексорах, вырабатывает ся код итерации, соответствукдщй типу селектора, формирование потен циалов . , }, и fj . управлянщих работой коммутаторов 17-20 кодов и сумматорами-вычитате лями 21-28. Причем, как видно из алгоритмов (1) и (2) и описания вы полнения вычислений в устройстве, эти потенциалы можно объединить в три группы. В первой группе - поте циал управления коммутаторами 17 и 19 кодов ,и сумматорами-вычитателями 21 и 24 ,, УП 1 в алгоритме I 1 в алгоритме Причем в первом случае коммутатор кодов пропускает код ,сдвинутьй на (2 i +1) разрядов, во втором - на 2 разряда. Во второй группе - потен циал управления сумматорами-вычита телями 22 и 25 УП 2 и,ч.1 в алгоритме (1) в алгоритме (2). В третьей- группе - потенциал уп равления коммутаторами 18 и 20 ко дов и сумматорами-вычитателями 23 и 26 в алгоритме (1) УП 3 в алгоритме (2). Перечисленные функции блока управления выполнены на стандартных элементах цифровой техники (распре делитель импульсов, счетчик, логические схемы), Порядок выработки сигналов записи начальных данных определяется временной диаграммой обмена информацией между ВУ и вне ними устройствами. Логическая схем 710 выработки потенциалов УП1-УПЗ определена блок-схемой алгоритма функционирования блока управления. Устройство работает следующим образом. Начальные значения координат z , N, X и угла б заносятся в блок 1-4 регистров соответственно. В начале каждой итерации координаты , v и х перезаписываются в блоки 5-7 регистров соответственно. В каждом такте работы устройства содержимое блоков 1-4 регистров выдается h-разрядными группами на входы сумматоров 30 и сумматороввычитателей 24, 26 и 23. В блоках 5-7 регистров в каждом такте работы, также как и в блоках 1-4 регистров производится сдвиг информации на один разряд, а в блоке регистров в целом - на п разрядов. Одновременно в каждом такте содержимое старшего разряда п-го сдвигового регистра блоков 5-7 регистров (знак числа) перезаписывается по последовательным сдвиговым входам в 1 -и данных регистров. Таким образом обеспечивается размножение .знака, необходимое для коммутаторов 8-12, а старшие разряды, блоков 1-3 регистров остаются свободными для записи результатов текущей итерации (. , Vj , У + -1 ). На коммутаторе В формируется значение 2; , на коммутаторах ,,. p.) и Ч) и на коммутаторах 9 и 12 - 2 и ( соответственно. Причем с выходов коммутаторов 8-12 ин-. формация также вьщается п-разрядными группами. Элементы 13-16 задержки осуществляют задержку на один такт старшего (п.-го) разряда группы выходного кода соответствующего коммутатора. Работу коммутаторов кодов покажем на примере потетрадной обработке информации (обработки последовательным кодом в системе счисления с основанием 2). Пусть первый четвертьй нумерация разрядов тетрады выходного кода коммутатора, начиная с младшего. Первый, третий разряды (выходы) коммутатора в коммутаторе кодов коммутируются на позиции второго - четвертого разрядов, а выход четвертого разряда коммутатора через элемент задержки на. позицию первого разряда. Таким образом осуществляется сдвиг числа, представленного послё1ровательним кодом в системе счисления 2, на один двоичный разряд влево. В результате выходные потетрадные. коды чисел v;2(2.) . 2-:()

(, v, коммутаторов 9-12 преобразуются с помощью элементов 15, 13, 16 и 14 задержки и коммутаторов 19, 17, 20 и 18 кодов в коды 2-2- , X; 2- , Х{ 2-2f и ( соответственно.

При вычислении по алгоритму (1) выходы элементов 15 и 16 задержки отключаются, сдвиг кодов в коммутаторах 19 и 20 не производится и информация с выходов коммутаторов 11 и 12 ( i 2-( и xi ) ) передается без изменения через коммутаторы 19 и 20 на входы сумматоров-вычислителей 24 и 26. При вычислении по алгоритму (2) входы сумма торов-вычитателей 21 и 27, связанные с коммутаторами 17 и 18 кодов, отключаются и информация, поступающая на вторые входы указанных сумматоров-вычитателей, передается на их выходы без изменения. В i-й итерации вычисления по ал горитму (1) производятся следующим образом. На сумматоре-вычитателе 24 вычи5.. ,-тается раз ность Tt-t-l , на сумматоре-вычитателе 25 - сумма 52 + +1 и на сумматоре-вычитателе 21 - значение координаты 24,2 524 + f j Xj 2 , записьтаемое в блок 2 регистров. На сумматоре-вычитателе 26 вычисляется разность 9-(у i 2. - , на сумма торе-вычитателе 22 - разность SDC - i4i 2-( 1 и на сумматоре-вычитателе 27 - значение.координаты 2v , записываемое в блок 3 регистров. На вторые входы сумматоров-вычитателей 23 и 28 и на объединенные входы сумматора 31 и вычитателя 29 поступают угловые постоянные сА u-j , i+z оС-+з соответственно, В результате на сумматоре-вычитателе 28 получается очередное приближение угла 9i+3 б{ - 4- o-i+l записываемое в блок 4 регистров, а на сумматоре 31 и вычитателе 29 соответственно /Ь,Ч4 -

в

,. Т . - -iTftj,, знаки которых выдаются в блок управления для формирования признака направления вращения . .

По алгоритму (2) вычисления в

i-й итерации выполняются следующим образом.

На сумматоре 30 производится сложение координаты 2 с величиной

Zj 2 , формируемой на коммутаторе 8. Очередное приближение координаты Z. Z + Z 22i записывается в блок 1 регистров. На сумматоре-вычитателе 24 вычисляется разность ъ - . ; 2 и на сумматоре-вычитателе 25 - значение

2-2. координаты - - i + - х - 2 , записываемое через сумматор-вычитатель 21 в блок 2 регистров. На сумматоре-вычитателе 26 вычисляется разность х,- - X,- 2 и на сумматоре-вычитателе

22- значение координаты

х 2-2 - i 2C+-t) , записываемое через сумматор-вычитатель 27 в блок 3 регистров. Очередное приближение угла i+i 0; + jjd вычисляется на сумматоре-вычитателе

23и через сумматор-вычитатель 28 записывается в блок 4 регистров. На вторые входы сумматора-вычитателя 28, сумматора 31 и вычитателя 29, являющиеся входами устройства, информация при вычислении по алгоритму (2) не поступает. Эффективность изобретения заключается в повьачении его быстродействия в . раз, где N - разрядность кодов, а единица учитывает дополнительный такт. Причем с ростом h затраты оборудования на единицу быстродействия снижаются, так как при этом в п раз увеличивается лишь разрядность сумматоров и межблочных цепей коммутации данных, а общая разрядность регистров, внешних цепей коммутации данньк и сложность схемы управления не увеличивается. Проведенные проработки принципиальных схем при N 24 дают следующие приближенные количественные оценки. При переходе к одновременной обработке двух разрядов при п 2 быстродействие увеличивается в 1,9 раза,при/1 3 в 2,8 раза,при 4 в 3,6 раза, а обьем оборудования устройства соотсетственно в 1,5)1,6 и 1,7 раза .

1 Л. ИЗУ9 о Выпаде ЫкаЗ Выходi блока 13 1

(VtenfИ ояедаиш j

Т

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1973 |

|

SU445042A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметическое устройство | 1975 |

|

SU538363A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1981-09-22—Подача